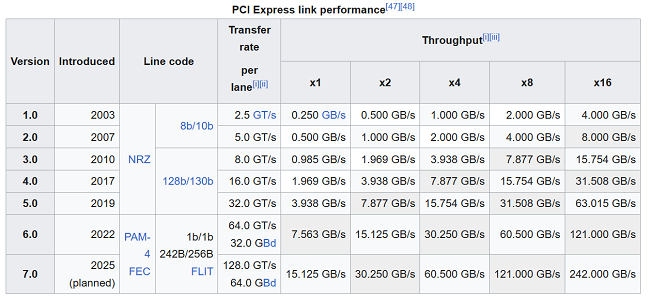

隨著高速互連技術的不斷演進,PCI Express(PCIe)標準已從 Gen3 的 8 GT/s 發展到 Gen5 的 32 GT/s,甚至到 Gen6 已達到 64 GT/s 級別。如此高的傳輸速率,對信號通道的損耗控制、阻抗匹配與抗干擾性能提出了前所未有的挑戰。

在此背景下,設計工程師們開始探索新的互連方式——例如采用 極細同軸線束(micro coaxial cable),也就是內部用于傳輸高速信號的極細同軸結構電纜。它是否能勝任 PCIe Gen5/Gen6 的高速信號傳輸任務?下面我們從結構特性、信號完整性及設計要點三個角度進行分析。

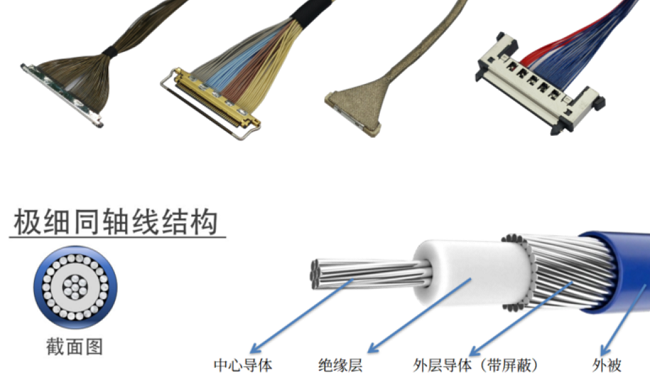

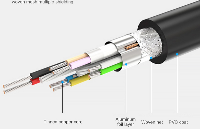

一、極細同軸線束的結構與特點

極細同軸線束由內導體、絕緣層、外導體屏蔽層及外護層組成,通常線徑非常細(如 AWG 36~40),可實現高密度、柔性化布線。與傳統的 PCB 差分走線相比,它具有以下幾個顯著特點:

1.1、高屏蔽性能:同軸結構能夠有效抑制電磁干擾(EMI)與串擾。

1.2、柔性布線能力:可彎折、可繞行,適合空間受限的設備內部連接。

1.3、機械輕巧:重量輕、體積小,有助于模塊化設計與小型化系統集成。

這些特性使得極細同軸線束在攝像模組、MIPI 接口、CoaXPress 工業相機等高速信號領域被廣泛采用。那么,它是否同樣適用于 PCIe Gen5/Gen6 呢?

二、PCIe Gen5/Gen6 的信號完整性挑戰

PCIe Gen5 與 Gen6 的信號速率已進入幾十 GHz 的頻率范圍,任何微小的不匹配或損耗都會導致誤碼率上升和眼圖收縮。主要挑戰包括:

2.1、帶寬與插入損耗控制:通道損耗必須控制在極低范圍內,否則信號幅度衰減嚴重。

2.2、回波損耗與阻抗一致性:系統要求嚴格的 85 Ω 或 100 Ω 差分阻抗匹配,任何過渡段都可能造成反射。

2.3、串擾與模式轉換:多通道并行傳輸下的互擾問題更為突出。

2.4、通道均衡與噪聲管理:需配合均衡電路、預加重及接收端濾波等方案共同優化。

這些因素共同決定了,PCIe Gen5/Gen6 的通道設計容差極小,對互連介質和結構的要求極為苛刻。

三、極細同軸線束用于 PCIe 高速信號的可行性分析

優勢方面:

3.1、出色的屏蔽性能:同軸屏蔽層可顯著降低外部干擾影響,對于高速通道非常有利。

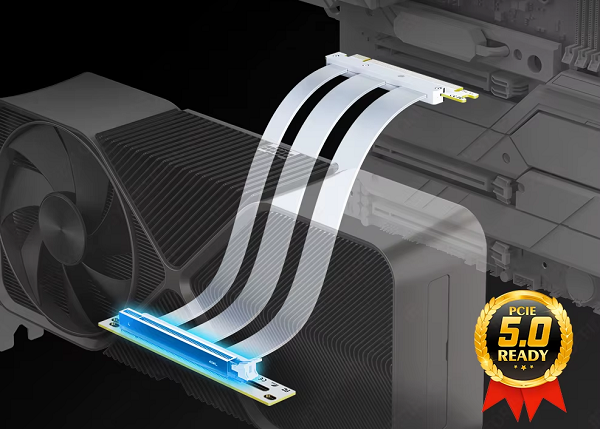

3.2、布局靈活性強:相比 PCB 差分走線,線束可在有限空間內靈活布設,特別適合模塊化、可插拔或緊湊型系統。

3.3、模塊化連接優勢:通過高速連接器可實現板間、模組間連接,便于維護和升級。

挑戰方面:

3.4、信號損耗問題:極細同軸線束直徑小,內部導體與絕緣層尺寸限制導致插入損耗較大,頻率越高衰減越明顯。

3.5、阻抗匹配難度:需確保整個鏈路(包括連接器、線束及 PCB)阻抗保持一致,否則會引起反射和眼圖閉合。

3.6、連接器與端接工藝要求高:高速同軸線的接頭必須具備極低的寄生電容與電感特性,否則會成為系統瓶頸。

3.7、制造一致性與成本壓力:微細結構對加工精度要求高,批量一致性與成本控制需權衡。

綜合來看,極細同軸線束確實具備支撐 PCIe Gen5/Gen6 傳輸的潛力,但要在工程上實現穩定可靠的信號性能,必須滿足嚴格的材料、電氣與結構要求。

四、設計實踐中的關鍵建議

4.1、盡量縮短線束長度:高速信號路徑應盡可能短,避免多余的繞行或折彎。

4.2、阻抗匹配設計:建議采用差分對同軸結構(如雙同軸線束)以獲得更好的平衡特性。

4.3、高性能連接器選型:選擇專為 32 GT/s 或更高速率設計的微同軸接口產品,確保端接穩定。

4.4、信號完整性仿真與實測:在設計階段進行 S 參數仿真與眼圖分析,并通過實測驗證損耗與抖動指標。

4.5、結構固定與屏蔽接地:確保線束不因震動或應力而改變電氣特性,屏蔽層接地可靠。

通過以上方法,極細同軸線束不僅能在結構空間上提供靈活性,還能在信號層面保持可控的損耗和低串擾,滿足高速互聯需求。極細同軸線束可在特定條件下用于 PCIe Gen5/Gen6 信號傳輸,但必須建立在高質量線束、嚴格的阻抗控制、專業的連接器選型與完善的信號仿真驗證基礎之上;對于高密度、模塊化、可插拔的高速設計來說,它是一種值得探索的解決方案;但若忽視信號完整性與損耗控制,則可能導致嚴重的系統性能問題。

我是【蘇州匯成元電子科技】,專注于高速信號互連與極細同軸線束定制,期待在電子發燒友平臺與更多工程師一起深入探討高速接口設計中的創新與實踐!

-

PCIe

+關注

關注

16文章

1464瀏覽量

88590 -

線束

+關注

關注

8文章

1130瀏覽量

26898 -

信號線束

+關注

關注

0文章

71瀏覽量

1615

發布評論請先 登錄

PCIe Gen5/Gen6 信號傳輸可以用極細同軸線束嗎?

PCIe Gen5/Gen6 信號傳輸可以用極細同軸線束嗎?

評論