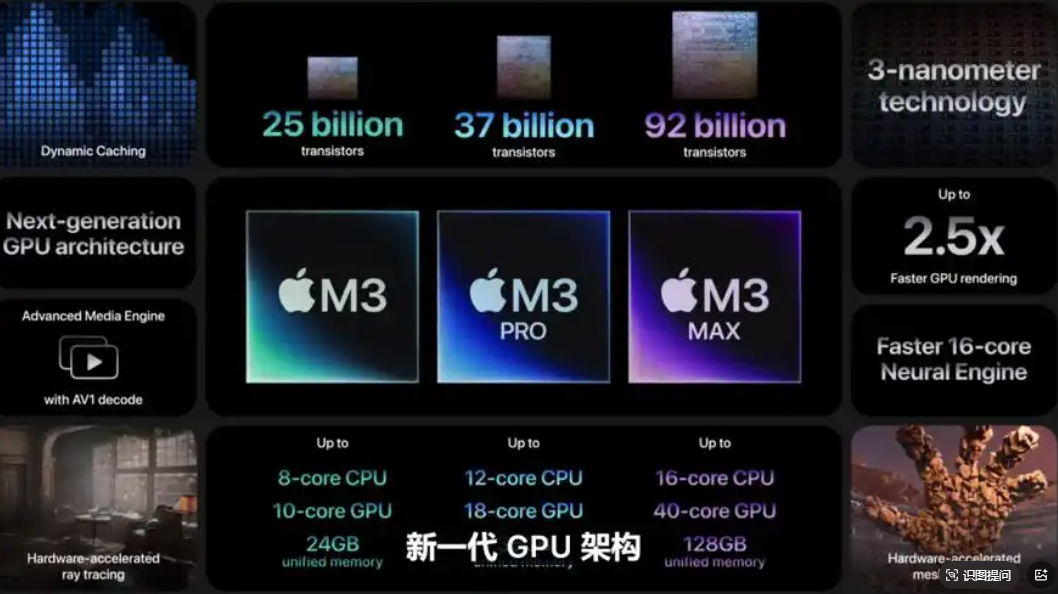

蘋(píng)果在本月初發(fā)布了最新一代的M1 Ultra芯片,采用了獨(dú)特的 UltraFusion 芯片架構(gòu)。借助橋接工藝,這款Ultra芯片擁有 1,140 億個(gè)晶體管,數(shù)量達(dá)到了M1的 7 倍之多。雖然芯片還是采用與上一代M1 max一樣的5nm工藝節(jié)點(diǎn),但在新架構(gòu)加持下,兩顆 Max 之間的互連頻寬可達(dá) 2.5TB/s。這種架構(gòu)的好處是運(yùn)行在目前M1芯片上的軟件無(wú)需修改相關(guān)的指令就可以直接運(yùn)行,省去了應(yīng)用端更新軟件或開(kāi)發(fā)新應(yīng)用層命令的需求。同時(shí),增加一個(gè)芯片后,對(duì)內(nèi)存處理的帶寬也直接翻倍,收獲的性能提升非常顯著,特別是針對(duì)GPU處理能力方面,是極具爆發(fā)力的。

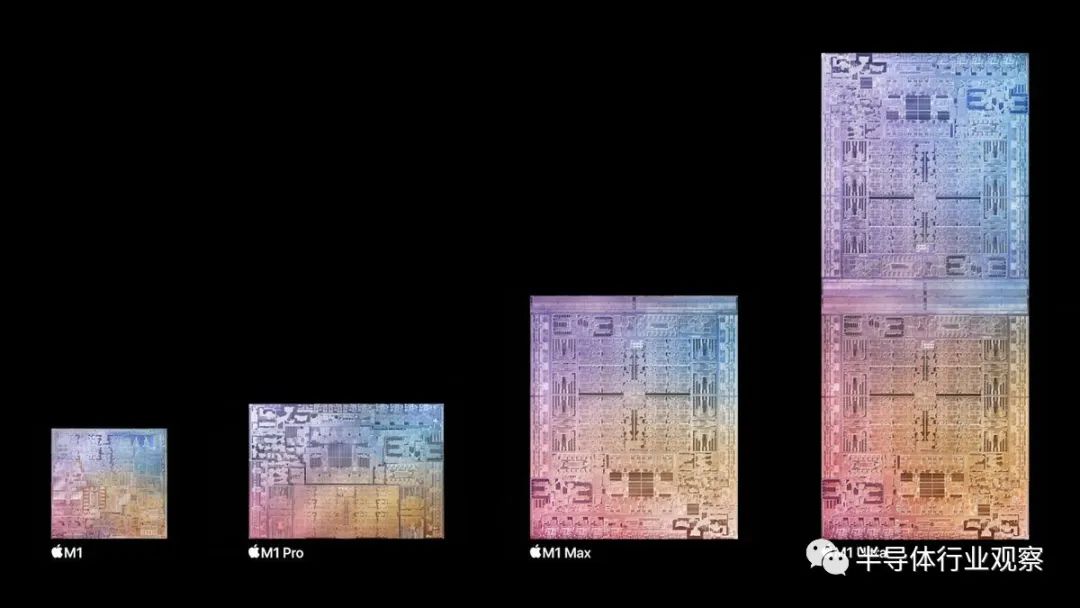

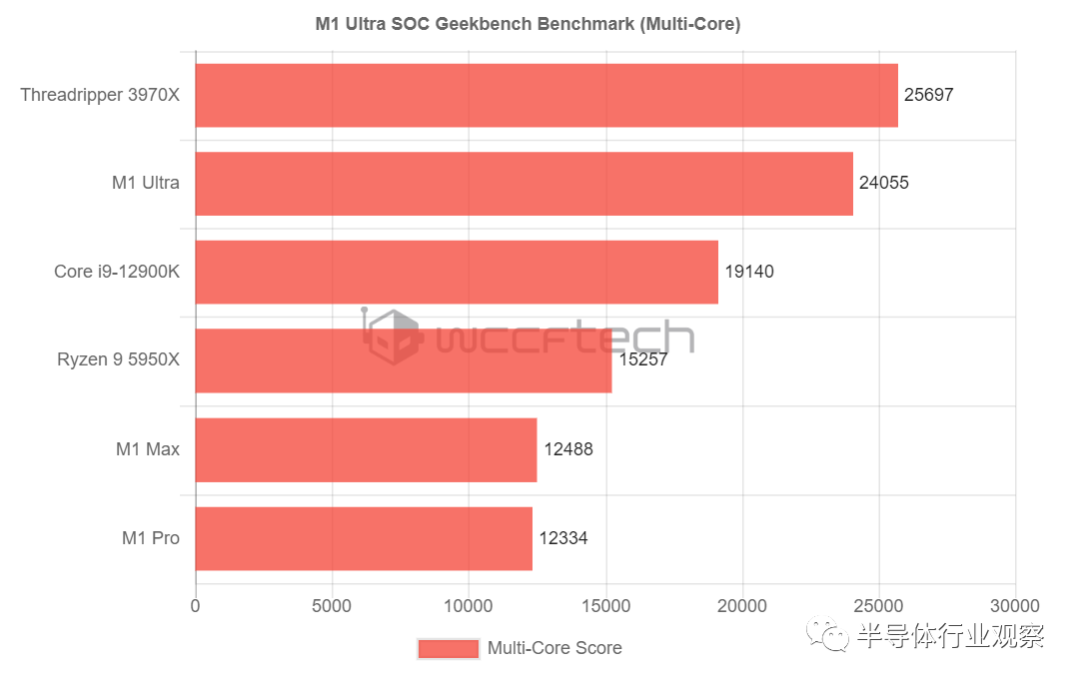

蘋(píng)果M1芯片進(jìn)化 (Source:Apple) 近日,評(píng)測(cè)機(jī)構(gòu)也對(duì)比了幾款主流芯片與M1 Ultra的性能。在單核處理能力上,Ultra并不比Max優(yōu)秀。但在多核多線程的性能上,性能翻倍,可以說(shuō)是秒殺上一代芯片。但相關(guān)的功耗并無(wú)披露,在之后的評(píng)測(cè)中可以繼續(xù)關(guān)心相關(guān)性能。

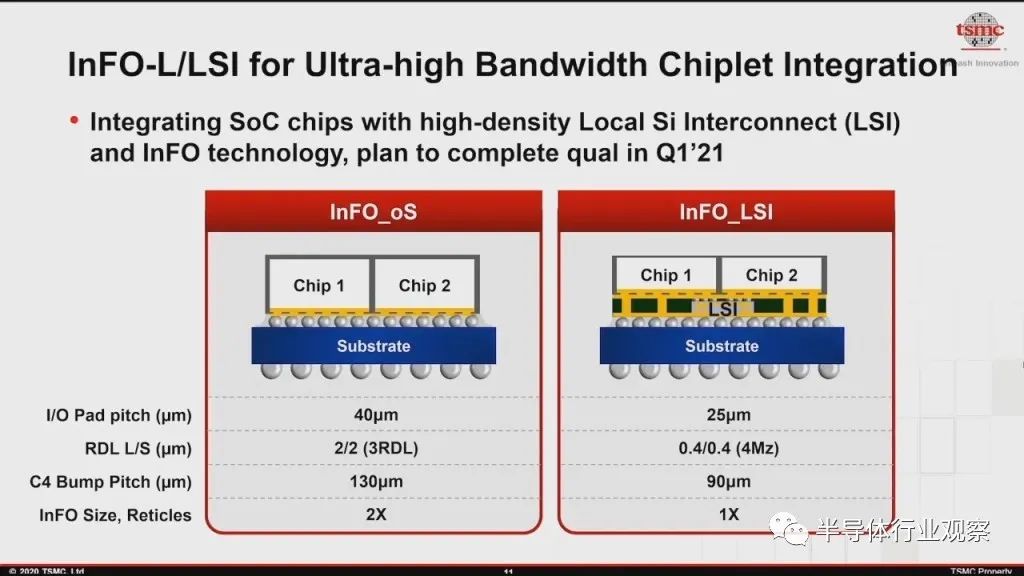

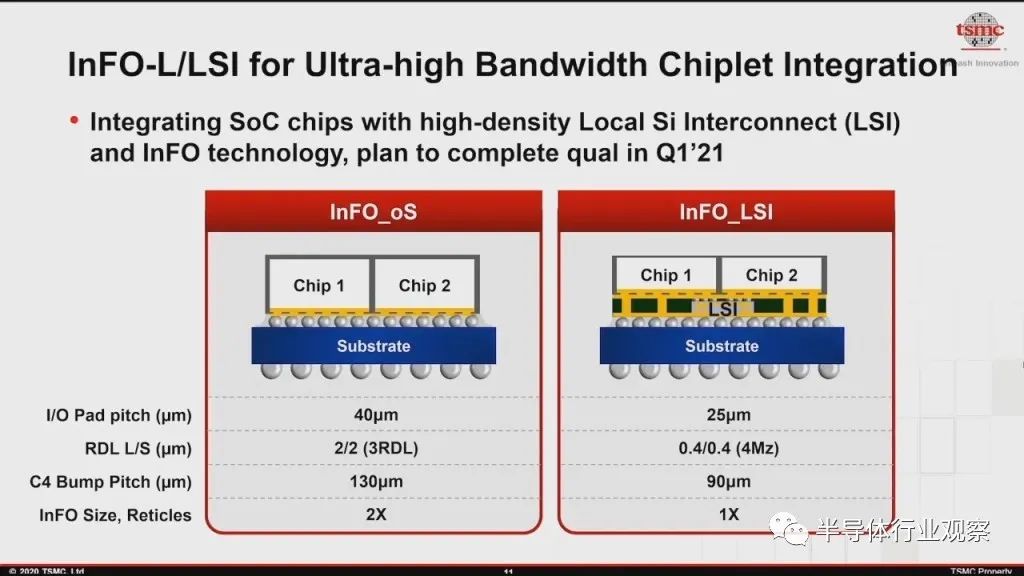

M1 Ultra多核多線程處理能力對(duì)比 (Source:WCCFtech) 從目前透露的信息,并不能確定M1 Ultra來(lái)源于哪種橋接工藝(估計(jì)隨后的Teardown即可見(jiàn)分曉),因?yàn)槟壳鞍═SMC和Intel都有埋入硅橋的類(lèi)似量產(chǎn)工藝。但由于使用的是2個(gè)同樣的芯片,從芯片設(shè)計(jì)角度來(lái)說(shuō)并不能算嚴(yán)格意義的Chiplet,更多是一個(gè)Multi-die package的設(shè)計(jì)。作者觀點(diǎn),考慮到臺(tái)積電為Apple主力代工的關(guān)系,采用臺(tái)積電埋入硅橋的可能性較大。從臺(tái)積電宣傳介紹了解到LSI在去年Q1還在做驗(yàn)證,而M1 Max在去年10月左右推出,M1 Ultra今年3月推出,在開(kāi)發(fā)時(shí)間上雖然很緊湊但也并非不可匹配。M1 Max在推出的時(shí)候也預(yù)留了橋接的I/O,加快了M1 Ultra的開(kāi)發(fā)周期。由此可見(jiàn)Ultra早已在1年前或更早時(shí)間就已經(jīng)在蘋(píng)果的計(jì)劃中。

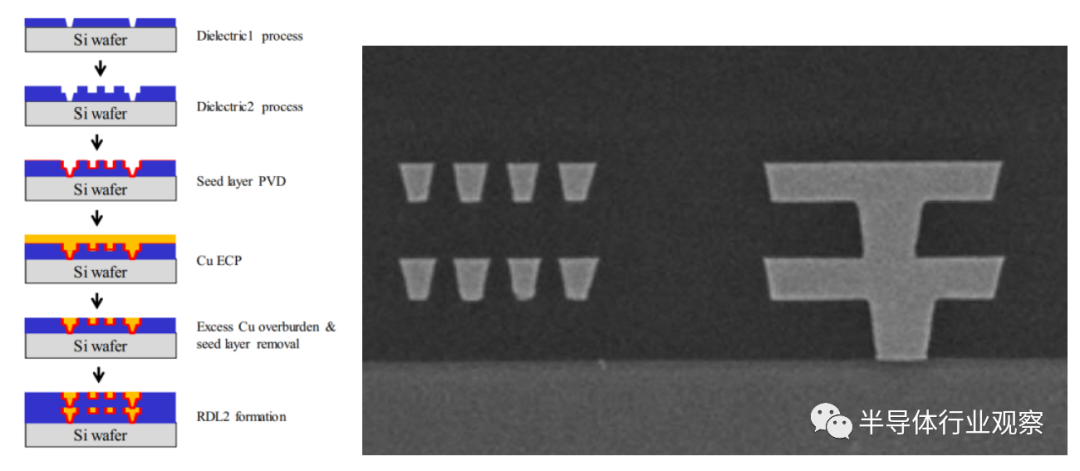

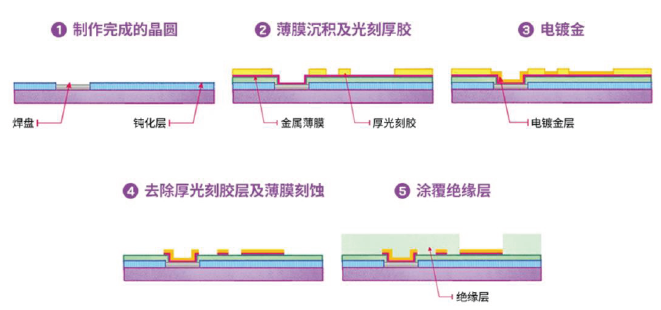

臺(tái)積電的局部硅橋(local silicon interconnect) (Source: 臺(tái)積電) 臺(tái)積電的硅橋技術(shù)分為硅通孔橋和硅上RDL橋。所謂硅通孔橋就是在埋入的硅橋中有TSV,信號(hào)穿過(guò)硅通孔,通過(guò)TSV進(jìn)行橋接。而RDL橋就是在硅上進(jìn)行RDL制備,而為了確保可靠性和工藝兼容,目前主要的絕緣層材料大多采用ABF或低熱膨脹EMC。

臺(tái)積電局部硅橋(local silicon interconnect) (Source: TSMC) 臺(tái)積電局部硅橋基于晶圓級(jí)硅工藝,比如金屬化和鈍化層形成等仍然是采用IC制造機(jī)臺(tái),因此其RDL精度非常高,可以輕松實(shí)現(xiàn)2微米線寬。這與Intel的Embedded Multi-Tile Interconnect Bridge(EMIB)工藝完全不同,因?yàn)镋MIB是使用板級(jí)基板工藝機(jī)臺(tái),雖說(shuō)硅橋本身可以做到2微米線寬,但埋入的后期工藝配合上有些挑戰(zhàn),本文后面會(huì)介紹。

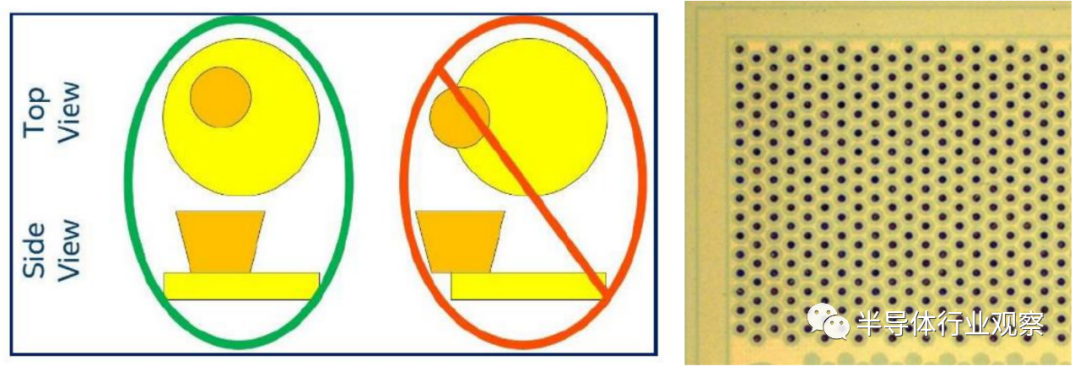

臺(tái)積電高密度RDL (Source: TSMC) 臺(tái)積電的InFO/CoW我們接收的信息比較多了,很多文章有介紹過(guò),這里不進(jìn)行詳述。接下來(lái)我們重點(diǎn)看看Intel的EMIB技術(shù)。 早在2011年的一個(gè)封裝國(guó)際會(huì)議上【1】, Intel的工程師就提出了用硅橋連接2個(gè)硅處理器的概念。而當(dāng)時(shí)的版本還未提及埋入這一概念,只是展示了橋接后較好的電性能。對(duì)如何封裝,如何大規(guī)模生產(chǎn),以及如何保證封裝體的可靠性等都是未知數(shù)。

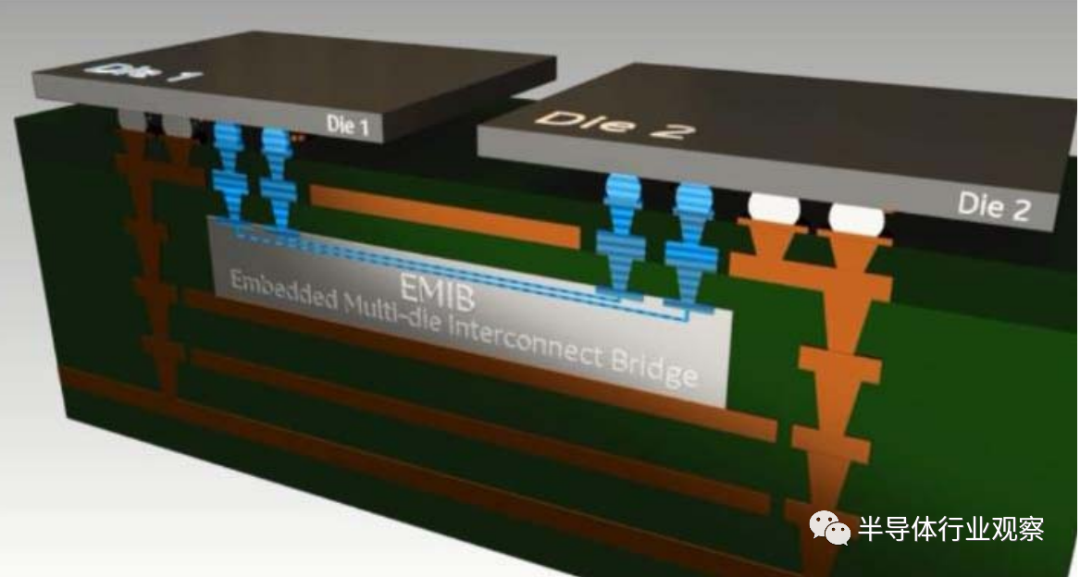

硅橋連接【1】 但很快,Intel在次年(2012)的一份專利中將目前版本的雛形進(jìn)行了描述【2】。而這份專利直到2015年授權(quán)之后才被公開(kāi)。所以,我們其實(shí)能看到的最早對(duì)EMIB的詳細(xì)描述是Intel在2016年ECTC發(fā)表的論文【3】。在這篇論文中,Intel展示了EMIB的結(jié)構(gòu),工藝,樣品性能等。通過(guò)這一技術(shù),EMIB可以實(shí)現(xiàn)與CoWoS類(lèi)似的I/O數(shù)量和帶寬。然而,開(kāi)發(fā)結(jié)合封裝基板技術(shù)與芯片制備技術(shù)的混合芯片封裝體充滿挑戰(zhàn),即使強(qiáng)大如Intel也花費(fèi)了不少時(shí)間,至今才達(dá)到了能量產(chǎn)的程度。接下來(lái)我們結(jié)合Intel發(fā)表的一些公開(kāi)的論文,試圖管中窺豹。

EMIB內(nèi)部結(jié)構(gòu)示意圖【3】 相對(duì)于其他2.5D/3D封裝技術(shù),EMIB的主要技術(shù)優(yōu)勢(shì)有以下幾點(diǎn)【4】:

| 1 | 利用先進(jìn)有機(jī)基板工藝實(shí)現(xiàn)局部高密度布線。區(qū)別于需要更大尺寸硅中介層和高密度硅通孔(TSV)的其他2.5D多芯片封裝技術(shù),能針對(duì)I/O需求實(shí)現(xiàn)局部高密度布線。 |

| 2 | 無(wú)光罩尺寸限制。由于要保證曝光顯影的精準(zhǔn)度和數(shù)值孔徑,光刻工藝的光罩尺寸范圍通常有其限制,例如M1 Max的芯片最大可用尺寸在19.05mmx22.06mm(約420mm2),已經(jīng)是臺(tái)積電硅橋CoWoS工藝的一半。EMIB則無(wú)需限制芯片尺寸,可以通過(guò)局部硅橋?qū)崿F(xiàn)相對(duì)自由的芯片尺寸搭配(InFO-LSI也是干這個(gè)事) |

| 3 | 相對(duì)硅TSV而言,EMIB的制造工藝更簡(jiǎn)單,成本也相對(duì)更低(如果良率相等的情況)。同時(shí),減少更多硅的浪費(fèi),只在需要互聯(lián)的地方放置硅橋。 |

然而主要的挑戰(zhàn)在板級(jí)工藝。因此EMIB缺點(diǎn)主要集中在工藝實(shí)現(xiàn)【4】:

| 1 | 引入了更復(fù)雜的有機(jī)基板制備工藝,在精準(zhǔn)度控制上遠(yuǎn)高于目前的有機(jī)基板布線。由此需要針對(duì)這一系統(tǒng)進(jìn)行特殊材料和工藝的開(kāi)發(fā)。 |

| 2 | 跟普通的倒裝芯片類(lèi)似,由于有機(jī)基板的熱膨脹系數(shù)(CTE)與硅橋芯片的CTE存在失配,使得表面貼裝的芯片引腳,芯片背面和填充熱界面材料之間產(chǎn)生較大的應(yīng)力。 |

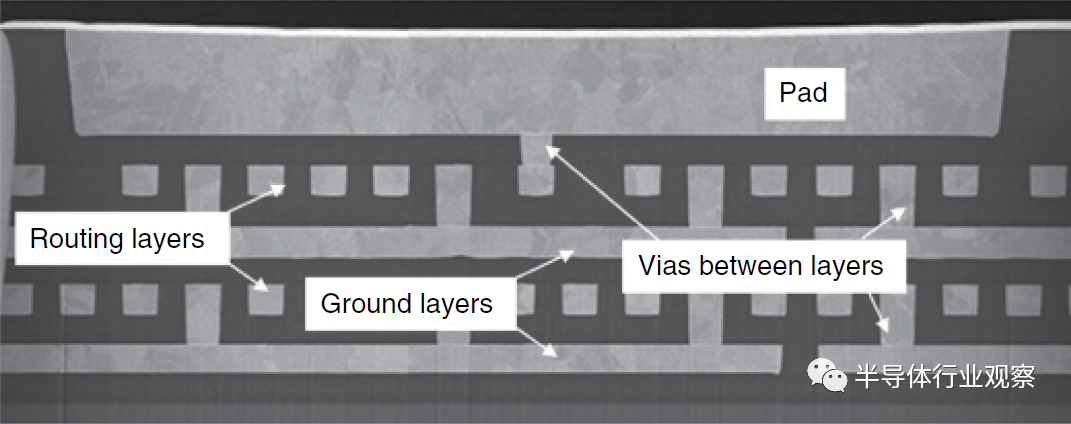

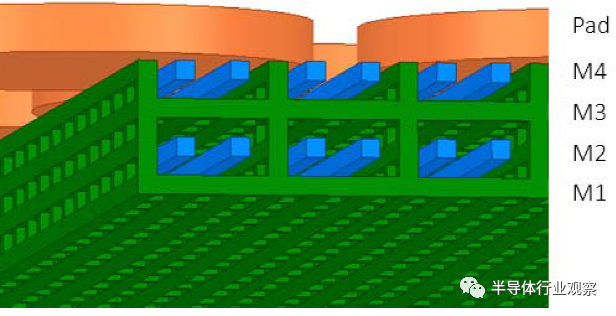

EMIB工藝由于搭配了硅和有機(jī)基板工藝,所以在技術(shù)上體現(xiàn)了目前先進(jìn)封裝的一個(gè)主流趨勢(shì) - 融合,特別是前段硅制程與后端封裝制程的融合。從硅橋部分來(lái)看,通常,硅橋的尺寸在2-8毫米左右,而芯片厚度在75微米以下,從而保證跟基板工藝所匹配,同時(shí)實(shí)現(xiàn)較高精準(zhǔn)度的布線和對(duì)準(zhǔn)工藝。目前Intel針對(duì)的是4層布線結(jié)構(gòu)的開(kāi)發(fā),能滿足大多數(shù)I/O需要。雖然,目前硅橋上的金屬布線的線間距可以穩(wěn)定實(shí)現(xiàn)2微米,進(jìn)一步進(jìn)行細(xì)微化也是非常可行的,因?yàn)榻饘俨季€的結(jié)構(gòu)都是在目前成熟的硅后端工藝中進(jìn)行制造。然而,隨著布線寬度的減小,線電阻會(huì)急劇增加,線間的電容也會(huì)改變,這給信號(hào)的完整性(integrity)增加了挑戰(zhàn)。因此,在進(jìn)行硅橋走線設(shè)計(jì)時(shí),需要非常詳細(xì)的架構(gòu)設(shè)計(jì)和模擬工作來(lái)保證最終的產(chǎn)品性能。另外,介電層的材料介電常數(shù)和高頻損耗對(duì)布線也有影響。因此,硅橋的設(shè)計(jì)工作是非常挑戰(zhàn)的,它完全不同于目前的硅芯片設(shè)計(jì)師們的日常設(shè)計(jì)理念,而需要懂材料,懂封裝,懂制程和懂信號(hào)完整性的資深工程師(們)來(lái)共同實(shí)現(xiàn)。

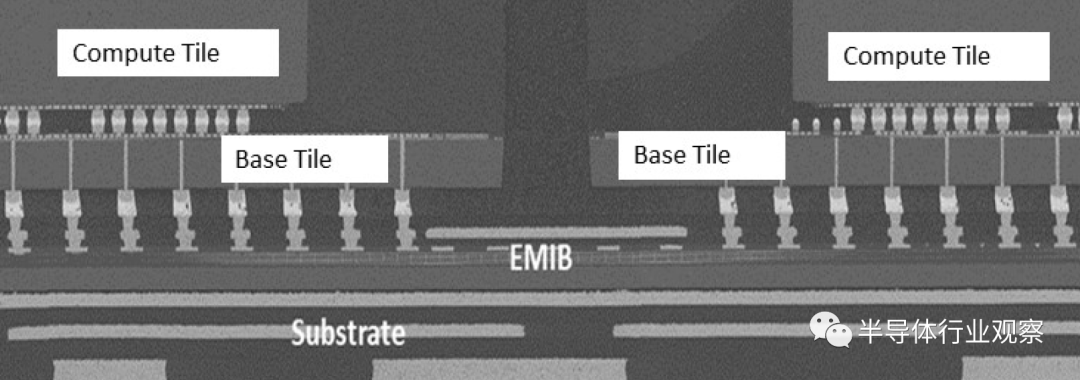

硅橋內(nèi)部結(jié)構(gòu)示意圖【4,5】 從硅橋的集成部分來(lái)看大概的工藝流程涉及到幾個(gè)關(guān)鍵步驟:基板的壓合,銅制程,激光以及芯片貼裝的埋入工藝。針對(duì)特殊工藝,Intel開(kāi)發(fā)了自家的埋入封裝(embedded)制程。其實(shí)在當(dāng)時(shí)埋入封裝已經(jīng)不是什么新東西,日本的廠家在早年曾做過(guò)針對(duì)電阻電容的埋入封裝。但由于那時(shí)還是PCB工藝,用的是CO2激光,非常粗糙;鍍銅工藝也相對(duì)落后,根本沒(méi)法做2微米的線寬,自然也不會(huì)有人想到用基板工藝去做芯片的高密度連接。Intel在10年前能想到用硅橋技術(shù)結(jié)合埋入封裝確實(shí)是一個(gè)大膽之舉。在加成法(Additive)鍍銅工藝和Coreless基板工藝成熟后,EMIB的實(shí)現(xiàn)也就水到渠成了。

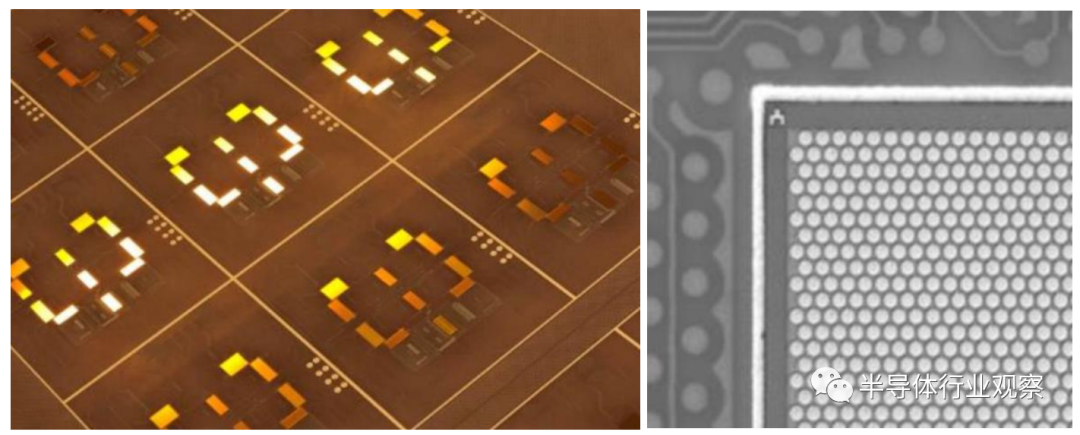

EMIB工藝示意圖【4】 埋入的過(guò)程由于采用有機(jī)基板工藝,對(duì)公差的控制提出了更高的要求,例如芯片的厚度,芯片的切割,芯片的貼裝,和薄片的轉(zhuǎn)移等都是及其挑戰(zhàn)的,需要獨(dú)有機(jī)器進(jìn)行配合。另外,整體的基板制備是扇出型的大板(FOPLP)封裝形式(500mm X 500mm),對(duì)板級(jí)的工藝一致性要求非常高。然而,在達(dá)到相對(duì)成熟的工藝良率后,產(chǎn)出的成本是相對(duì)較低的。同時(shí),大板封裝有其先天優(yōu)勢(shì),適合制造非常大的集成芯片,這與目前的小芯片(Chiplet)技術(shù)上的需求是吻合的。與普通FOPLP不同的是,EMIB并不需要將芯片從臨時(shí)的載板上取下,當(dāng)芯片被貼上之后就是永久固定的,減小了芯片在后續(xù)工序中位移的風(fēng)險(xiǎn)。

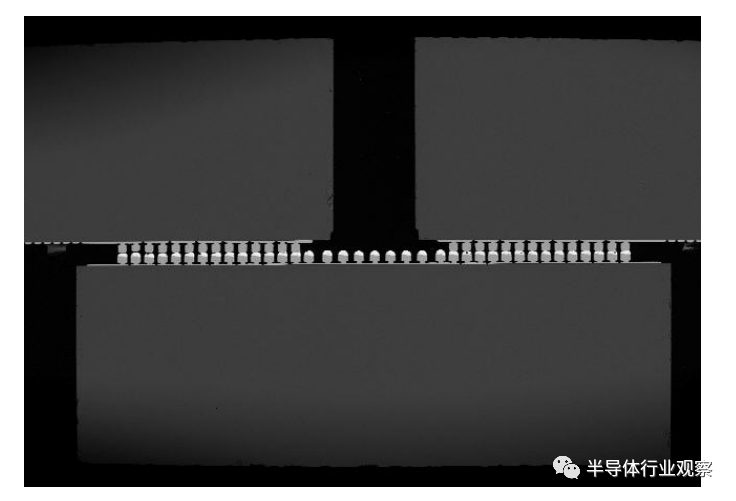

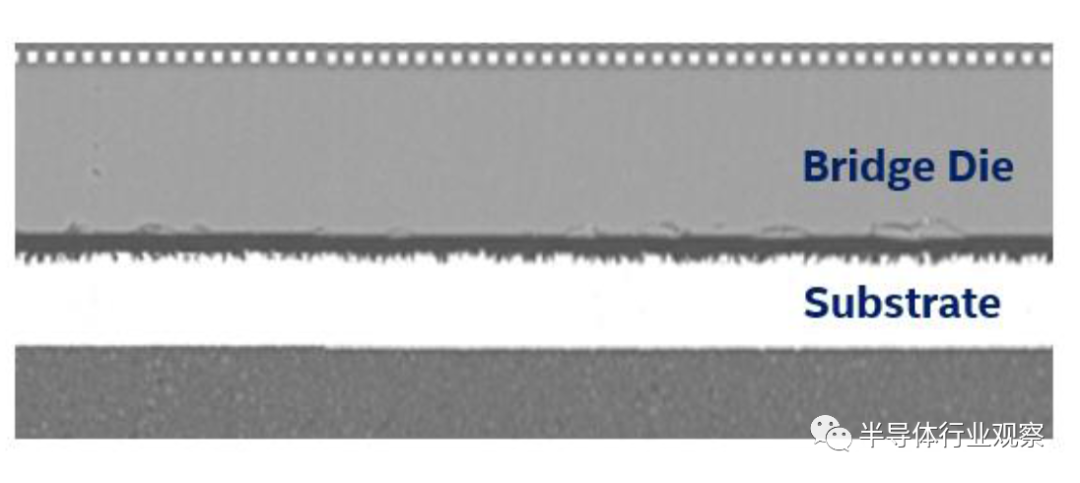

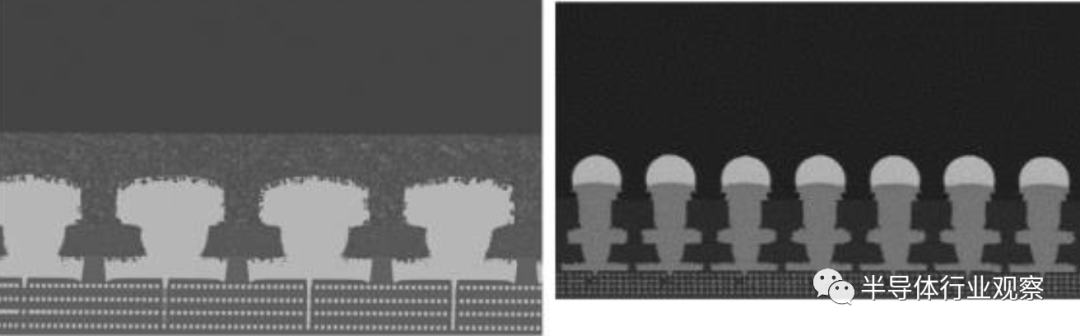

埋入在有機(jī)基板中的硅橋【6】 硅橋的芯片雖然只有2-8mm,但是小于75微米的薄片會(huì)由于內(nèi)部的Cu布線結(jié)構(gòu)產(chǎn)生芯片翹曲。另外,芯片貼裝膜(DAF)的存在也會(huì)直接導(dǎo)致切割后的芯片產(chǎn)生翹曲。因此,如何控制貼裝之后的芯片不產(chǎn)生孔洞及分層,乃至芯片破裂又是一個(gè)挑戰(zhàn)所在。針對(duì)這一要求,Intel開(kāi)發(fā)了針對(duì)這一工序的DAF材料,并通過(guò)優(yōu)化基板銅層的表面,貼裝材料固化工藝和有機(jī)材料的疊層工藝,實(shí)現(xiàn)了可接受的過(guò)程。

無(wú)分層的芯片貼裝截面【6】 在除了以上跟芯片貼裝相關(guān)的精準(zhǔn)控制要求之外,在進(jìn)行大面積高數(shù)量激光鉆孔的對(duì)準(zhǔn)上也極其挑戰(zhàn)。硅橋表面的銅引腳尺寸在50微米左右(或更小),而間距(pitch)可能在70微米(或更小)。因此對(duì)激光鉆孔機(jī)器本身的對(duì)準(zhǔn)要求極高。如激光開(kāi)口無(wú)法與硅橋上的銅引腳對(duì)應(yīng)(部分對(duì)應(yīng)也不行),在之后的阻抗匹配和信賴性的表現(xiàn)上就有可能會(huì)出現(xiàn)問(wèn)題。當(dāng)然,除了激光通孔,也可以使用掩膜版光刻的形式去形成對(duì)位孔,采用物理刻蝕的方式去形成通孔,而Intel采用何種工藝估計(jì)會(huì)根據(jù)孔的密度來(lái)進(jìn)行選擇。

埋入的硅橋需要精準(zhǔn)的激光鉆孔對(duì)位【6】 在實(shí)現(xiàn)上下通孔后,要實(shí)現(xiàn)互聯(lián)的工序就是進(jìn)行化學(xué)及電化學(xué)銅沉積,這在基板工藝中是成熟工藝。但通孔的尺寸實(shí)在是很小,對(duì)填銅工藝是有挑戰(zhàn)的,當(dāng)液體無(wú)法進(jìn)行充分的離子交換,填銅的速度在整個(gè)500mmx500mm的大板中沉積的速度不一樣時(shí)就會(huì)導(dǎo)致不同的填充厚度。同時(shí)水平和垂直電鍍線的藥水和工藝能力也存在較大差異,相信Intel在開(kāi)發(fā)過(guò)程中在這一工序上沒(méi)少嘗試。

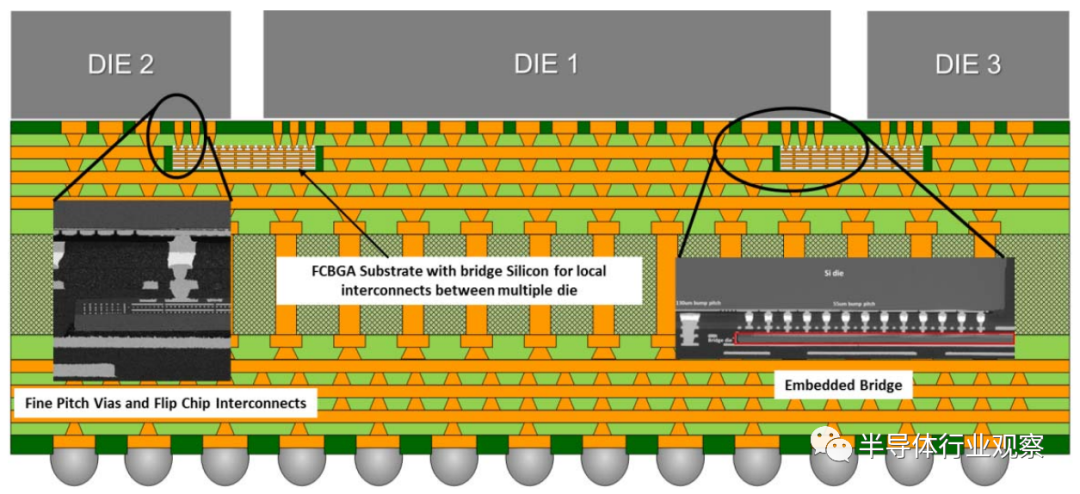

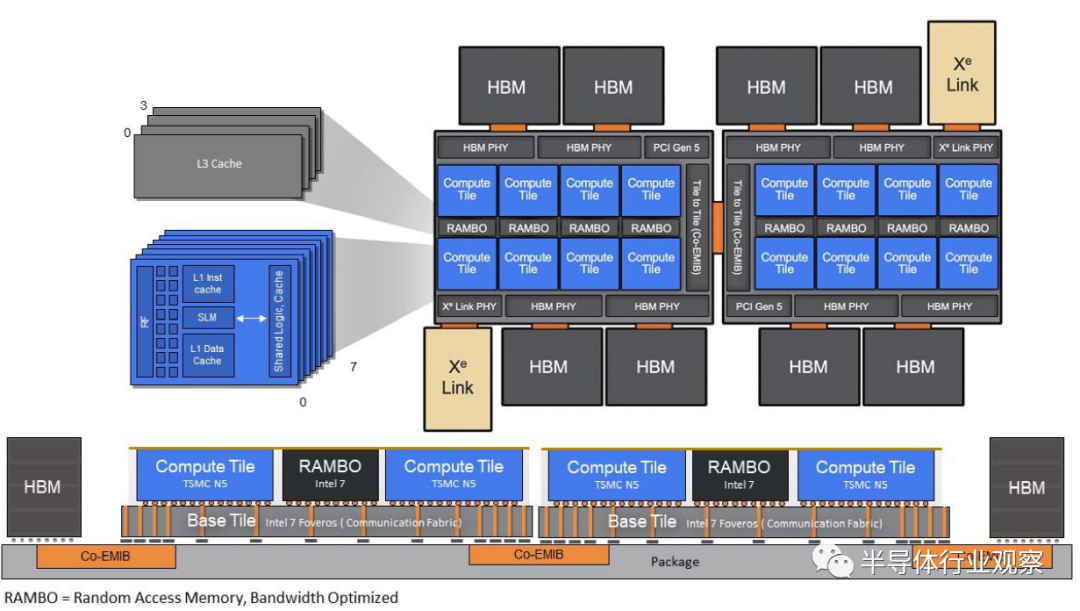

硅橋上填充的銅通孔【6】 Intel自家的技術(shù)自然也在自家的產(chǎn)品上積極運(yùn)用。針對(duì)超級(jí)計(jì)算機(jī)和人工智能應(yīng)用,Intel在2019年公布了基于Xe架構(gòu)的芯片系統(tǒng)-真的是一個(gè)芯片系統(tǒng),非常多芯片。該系統(tǒng)被命名為Ponte Vecchio,是用于高性能計(jì)算的下一代加速器。它結(jié)合47個(gè)Magical Tiles,主要由Compute Tiles、Base Tiles、Rambo Cache tile和Xe Link Tiles組成,每個(gè)Tiles都使用不同的制程制造。關(guān)于該芯片的命名,來(lái)源于意大利佛羅倫薩最古老的橋韋基奧橋(Ponte Vecchio),橋最初是以建筑師的名字命名的,類(lèi)似我們中國(guó)貴州的風(fēng)雨廊橋。而Intel以此橋?yàn)槊郑氡厥菫榱梭w現(xiàn)該系統(tǒng)的經(jīng)典和復(fù)雜,因?yàn)樵诂F(xiàn)實(shí)中這座橋和周?chē)慕ㄖ且粋€(gè)拜占庭式的龐然大物,橋的兩邊是當(dāng)?shù)氐奶厣ㄖ鼈兺ㄟ^(guò)這座橋以巧妙的方式相互連接,形成這么一個(gè)古老而又有特殊建筑風(fēng)格的大師級(jí)作品。

Intel芯片架構(gòu)及Ponte Vecchio集成 (Source: Intel) 在Ponte Vecchio芯片中,不僅有EMIB,還有FOVEROS,可謂是當(dāng)今3D集成度頂尖的芯片案例。美國(guó)能源部超級(jí)計(jì)算機(jī)Aurora將以Ponte Vecchio為核心的,每個(gè)Ponte Vecchio系統(tǒng)每秒能夠進(jìn)行超過(guò)45萬(wàn)億次32位浮點(diǎn)運(yùn)算。四個(gè)這樣的系統(tǒng)與兩個(gè)Sapphire Rapids CPU一起構(gòu)成一個(gè)完整的計(jì)算系統(tǒng)。超過(guò)54000個(gè)Ponte Vecchios和18000個(gè)SapphireRapids組合在一起,形成Aurora。

Ponte Vecchio高性能加速器GPU 及其EMIB結(jié)構(gòu)【7】 當(dāng)芯片節(jié)點(diǎn)來(lái)到5nm,僅僅通過(guò)硅工藝來(lái)延續(xù)摩爾定律似乎已經(jīng)捉襟見(jiàn)肘。臺(tái)積電和Intel用先進(jìn)封裝結(jié)合硅工藝給半導(dǎo)體行業(yè)帶來(lái)了新的范式,通過(guò)先進(jìn)封裝系統(tǒng)集成給摩爾定律的延續(xù),提供了一種新的方向。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465952 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

599瀏覽量

69303

原文標(biāo)題:摩爾定律的延續(xù),從蘋(píng)果M1 Ultra看先進(jìn)封裝技術(shù)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

神眸再發(fā)新品!M1智能親情可視通搭起遠(yuǎn)程陪伴橋梁

AI定義座艙新高度|搭載天璣座艙S1 Ultra的奇瑞風(fēng)云T9L

Microchip擴(kuò)展maXTouch? M1觸摸屏控制器系列,實(shí)現(xiàn)更廣泛的屏幕尺寸覆蓋

EVAL - M1 - 101T評(píng)估板:電機(jī)控制應(yīng)用的理想選擇

探索Eval - M1 - CM610N3評(píng)估板:電機(jī)驅(qū)動(dòng)應(yīng)用的理想之選

EVAL - M1 - IM523評(píng)估板:助力電機(jī)驅(qū)動(dòng)應(yīng)用設(shè)計(jì)

MediaTek發(fā)布天璣座艙P(yáng)1 Ultra芯片

MediaTek發(fā)布天璣座艙S1 Ultra芯片

從InFO-MS到InFO_SoW的先進(jìn)封裝技術(shù)

突破!華為先進(jìn)封裝技術(shù)揭開(kāi)神秘面紗

用于 Cat M1/1/NTN 和 WCDMA HSDPA/HSUPA/HSPA(頻段 1、2、4、5、8)和 CDMA(頻段類(lèi)別 0、1、6、15)的多模式、多頻段功率放大器模塊 skyworksinc

淺談Chiplet與先進(jìn)封裝

M3 Ultra 蘋(píng)果最強(qiáng)芯片 80 核 GPU,32 核 NPU

從蘋(píng)果M1 Ultra看先進(jìn)封裝技術(shù)

從蘋(píng)果M1 Ultra看先進(jìn)封裝技術(shù)

評(píng)論