FPGA設計不是簡單的芯片研究,主要是利用 FPGA 的模式進行其他行業產品的設計。

fpga主要有Verilog、VHDL和C語言進行編程,常用的還是前面兩種,雖然有些國外公司試圖C語言替代VHDL語言的目的,但是一般情況不使用C語言進行編程。

據悉,在IC設計領域,90%以上公司都是采用verilog進行IC設計,當然對于PLD/FPGA設計者而言,兩種語言可以自由切換。

VHDL還是verilog HDL,兩種語言其實差別并不大,描述能力也類似,但是Verilog HDL是目前應用最為廣泛的硬件描述語言,在使用上相對來說比較嚴謹,以用來進行各種層次的邏輯設計,也可以進行數字系統的邏輯綜合,仿真驗證和時序分析等。

編輯:hfy

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636328 -

編程語言

+關注

關注

10文章

1964瀏覽量

39571

發布評論請先 登錄

相關推薦

熱點推薦

Verilog HDL語法學習筆記

Verilog HDL 語 言 最 初 是 作為 Gateway Design Automation 公 司 ( Gateway DesignAutomation 公司后來被著名的 Cadence Design Systems 公司收購)模擬器產品開發的硬件建模

HLS設計中的BRAM使用優勢

高層次綜合(HLS)是一種將高級編程語言(如C、C++或SystemC)轉換為硬件描述語言(HDL)的設計方法。在FPGA設計中,設計者可以

如何使用Modelsim仿真I2C控制器

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述語言的仿真軟件。該軟件可以用來實現對設計的VHDL、Verilog HDL

嵌入式和FPGA的區別

大多數軟件開發人員快速上手。

FPGA開發則需要硬件描述語言(如Verilog或VHDL),開發者需要具備數字電路設計思維,開發周期相對較長,驗證和調試也更為復雜。

性能與靈活性權衡

在實時性方面

發表于 11-19 06:55

【產品介紹】Modelsim:HDL語言仿真軟件

概述ModelSim是業界最優秀的HDL語言仿真軟件,它能提供友好的仿真環境,是業界唯一的單內核支持VHDL和Verilog混合仿真的仿真器。它采用直接優化的編譯技術、Tcl/Tk技術、和單一內核

如何使用FPGA實現SRIO通信協議

本例程詳細介紹了如何在FPGA上實現Serial RapidIO(SRIO)通信協議,并通過Verilog語言進行編程設計。SRIO作為一種高速、低延遲的串行互連技術,在高性能計算和嵌

復雜的軟件算法硬件IP核的實現

Designer 除了可以進行傳統的電路原理圖以及 PCB 設計以外,它還可以進行單片機程序設計以及 FPGA 的開發。在本設計中將 C 語言組件轉換為 HDL 描述文件 就是使用 Altium

發表于 10-30 07:02

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRA

使用Simulink自動生成浮點運算HDL代碼(Part 1)

引言

想要實現浮點運算功能,如果自己寫Verilog代碼,需要花費較多的時間和精力。好在Simulink HDL Coder工具箱提供了自動代碼生成技術。下圖展示了HDL Coder如何生成浮點運算

發表于 10-22 06:48

基于FPGA開發板TSP的串口通信設計

本文詳細介紹基于Terasic FPGA開發板TSP(又名C5P和OSK)和其板載CP2102N USB-UART橋接芯片的串口通信系統設計與實現。系統采用Verilog HDL編寫UART收發控制器,通過CP2102N實現

一文詳解Verilog HDL

Verilog HDL(Hardware Description Language)是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。現實生活中多用于專用集成電路

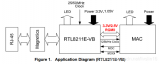

千兆網絡PHY芯片RTL8211E的實踐應用

以太網MAC模塊負責實現以太網MAC子層的功能,完成802.3ab的數據封裝與解封。其同時負責適配硬件PHY的物理接口,組成物理層的通訊接口; 硬件系統的功能可以通過 Verilog HDL硬件描述語言在

fpga用的是什么編程語言 Verilog HDL應用最為廣泛

fpga用的是什么編程語言 Verilog HDL應用最為廣泛

評論