本文詳細介紹基于Terasic FPGA開發板TSP(又名C5P和OSK)和其板載CP2102N USB-UART橋接芯片的串口通信系統設計與實現。系統采用Verilog HDL編寫UART收發控制器,通過CP2102N實現FPGA與PC間的快速穩定通信。

1CP2102N簡介及其驅動安裝

查閱數據手冊TSP_v.x.x.x_SystemCDDatasheetUart_to_USBcp2102n-datasheet.pdf可知CP2102N關鍵特性:

支持300bps至3Mbps波特率

內置USB 2.0全速控制器

自動波特率檢測和信號極性控制

3.3V UART接口電平,與FPGA直接兼容

在之前文章1-串行通信基礎知識提到在使用UART轉USB口之前,主機需要安裝串口驅動程序,在操作系統中創建一個虛擬串口(如 COM3)。這樣,上位機軟件就可以像操作傳統串口一樣,通過這個虛擬串口與 FPGA 通信了。

當TSP開發板的串口J6口插到PC的USB口以后,電腦設備管理器會出現如下設備:

右擊選中CP2102N USB to UART Bridge Controller設備,選擇更新驅動程序(P):

然后選擇瀏覽我的電腦以查找驅動程序(R):

CP2102N的PC端驅動文件在TSP_v.x.x.x_SystemCDToolserial_driver(該壓縮包在友晶官網下載)路徑下, 比如您的電腦當前版本是Win10, 事先解壓win10文件夾下的CP210x_Universal_Windows_Driver.zip壓縮包到當前路徑,然后將驅動路徑指到剛解壓的文件路徑:

在點擊下一步后會彈出驅動安裝成功窗口,最后點擊關閉按鈕即可:

安裝以后PC設備管理器如下:

1

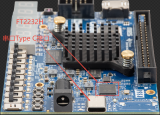

TSP的串口硬件電路

TSP的串口硬件電路圖如下:

1

串口代碼設計與功能仿真

代碼設計思想參考2-基于FPGA開發板DE23-Lite的串口通信設計 (FT2232H),Quartus工程下載:參見本文末,本工程使用Quartus 17.1 Lite版本,仿真(仿真設置步驟請參考06-基于FPGA和LTC2308的數字電壓表設計-ModelSim仿真與Matlab模擬信號產生)結果如下:

引腳分配如下:

1

串口設計下板驗證

測試之前硬件連接如下:

連接串口J6 到PC;

用USB Blaster線纜連接開發板和PC;

連接12V電源到開發板;

將sof配置文件下載到開發板:

先從設備管理器里面找到當前串口的名稱:

然后雙擊putty.exe打開串口調試工具:

點擊Serial設置串口為COM10,波特率設置為115200,停止位設置為1,然后點擊Session:

點擊 Session以后出現如下界面,點擊Open打開串口:

發送任意字符:

然后查看串口接收到的字符是否與之一致:

備注:

基于TSP(C5P/OSK)的例程下載地址:

通過網盤分享的文件:TSP_UART.rar

鏈接:https://pan.baidu.com/s/1iY0f5ef2YXWrHaXl_6q_xA提取碼: tera

-

FPGA

+關注

關注

1661文章

22443瀏覽量

637500 -

uart

+關注

關注

22文章

1315瀏覽量

106786 -

串口通信

+關注

關注

34文章

1662瀏覽量

58070 -

開發板

+關注

關注

26文章

6326瀏覽量

119091

原文標題:3-基于FPGA開發板OSK/TSP/C5P的串口通信設計 (CP2102N)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【Runber FPGA開發板】配套視頻教程——UART串口通信實驗

Altium推出智能FPGA開發板NanoBoard 300

fpga開發板用途,fpga開發板價格

基于STM32F4開發板的激光測距模塊串口通信(三)

基于FPGA開發板TSP的串口通信設計

基于FPGA開發板TSP的串口通信設計

評論