ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述語言的仿真軟件。該軟件可以用來實現對設計的VHDL、Verilog HDL 或是兩種語言混合的程序進行仿真。這里的仿真是對設計進行功能仿真(也稱之為前仿真),其目的是驗證電路功能是否符合設計要求。

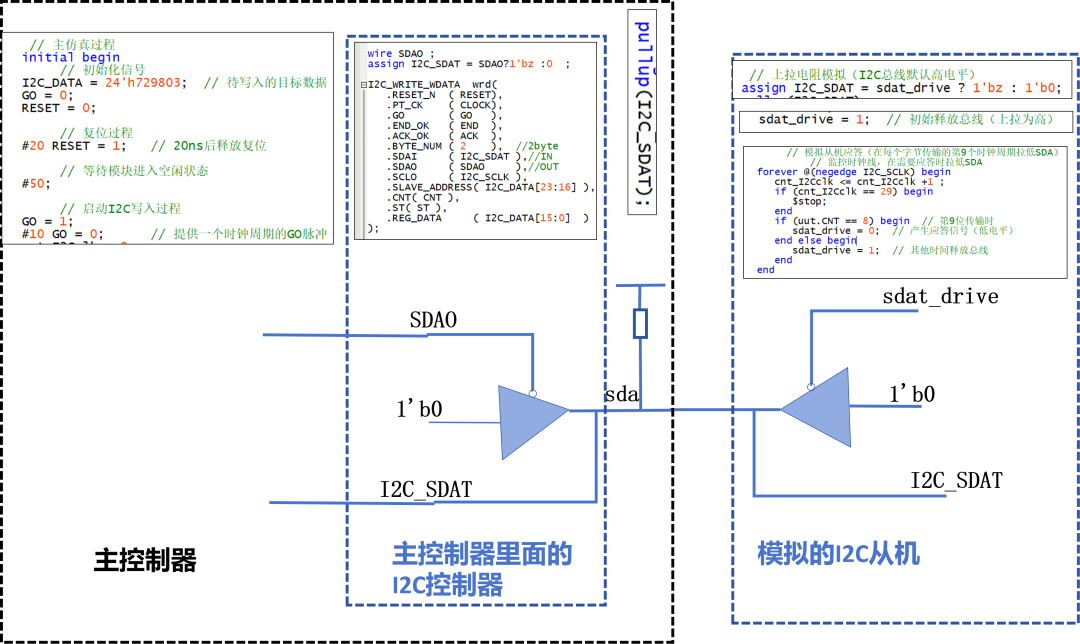

本篇主要是對I2C_Controller模塊進行功能仿真。test_bench的核心是模擬FPGA給出數據24'h729803,同時也模擬I2C外設來接收該數據并給出應答反饋。

1. 首先用Quartus打開HDMI_block_move工程(HDMI_block_move工程下載鏈接:https://pan.baidu.com/s/1XxFFj-3UTfB_Er-yz0f_Cg提取碼: tera),然后在該工程路徑下新建一個Verilog test bench仿真文件。右擊File——New, 選擇Verilog HDL File,然后點擊OK:

2. 將下面代碼拷貝到新建的.v文件當中:

`timescale 1ns/1ps module tb_I2C_Controller(); // 輸出信號定義 regCLOCK; reg [23:0]I2C_DATA; regGO; regRESET; // 雙向信號定義(I2C_SDAT需要上拉電阻模擬總線特性) wireI2C_SDAT; reg sdat_drive; // 用于模擬從機應答的驅動信號 // 輸入信號定義 wireI2C_SCLK; wireEND; wireACK; // 上拉電阻模擬(I2C總線默認高電平) assignI2C_SDAT=sdat_drive?1'bz :1'b0; // 例化被測試模塊 I2C_Controlleruut ( .CLOCK(CLOCK), .I2C_DATA(I2C_DATA), .GO(GO), .RESET(RESET), .I2C_SDAT(I2C_SDAT), .I2C_SCLK(I2C_SCLK), .END(END), .ACK(ACK) ); reg [7:0] cnt_I2Cclk; // 時鐘生成(100MHz,周期10ns) initial begin CLOCK=0; forever #5CLOCK=~CLOCK; end // 主仿真過程 initial begin // 初始化信號 I2C_DATA=24'h729803; // 待寫入的目標數據 GO=0; RESET=0; sdat_drive=1; // 初始釋放總線(上拉為高) // 復位過程 #20RESET=1; // 20ns后釋放復位 // 等待模塊進入空閑狀態 #50; // 啟動I2C寫入過程 GO=1; #10GO=0; // 提供一個時鐘周期的GO脈沖 cnt_I2Cclk=0; // 模擬從機應答(在每個字節傳輸的第9個時鐘周期拉低SDA) // 監控時鐘線,在需要應答時拉低SDA forever @(negedgeI2C_SCLK) begin cnt_I2Cclk<=?cnt_I2Cclk?+1?; ? ??if?(cnt_I2Cclk?==?29) begin ? ? ??$stop; ? ? end ? ??if?(uut.CNT?==?8) begin ?// 第9位傳輸時 ? ? ? sdat_drive?=?0; ?// 產生應答信號(低電平) ? ? end? ? ??else?begin ? ? ? sdat_drive?=?1; ?// 其他時間釋放總線 ? ? end ? end ? ? ? ? end endmodule

3. 點擊Save按鈕,將文件保存為tb_I2C_Controller.v。

4. 安裝Quartus軟件的時候也記得安裝Modelsim 工具(這些安裝步驟在后期文章里面會發布),接下來要將Modelsim 的安裝路徑設置一下就才可以在仿真時自動調用指定的仿真工具。首先是在Tools菜單下面找到Options:

5. 在彈出的對話框中選擇EDA Tool Options ,點擊...指定軟件路徑: D:intelFPGA_lite17.1modelsim_asewin32aloem:

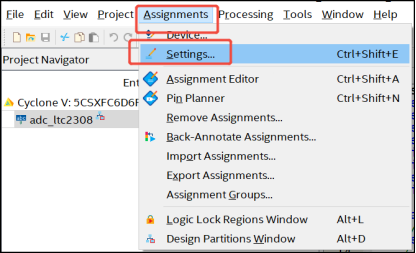

6. 接下來設置仿真文件路徑。點擊Assignments——Settings:

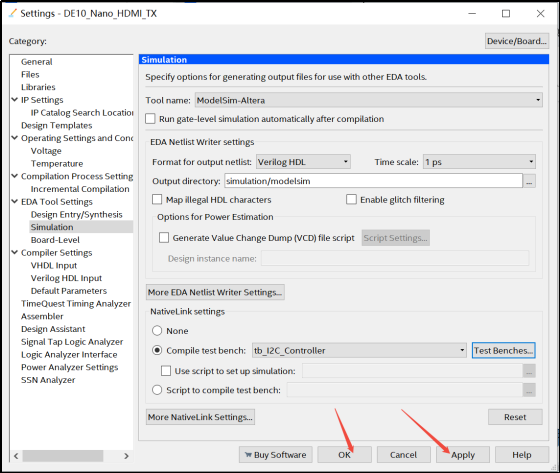

7. 點擊 Simulation,仿真工具選擇ModelSim-Altera, 然后點選Compile test bench圓圈,點擊Test Benches...

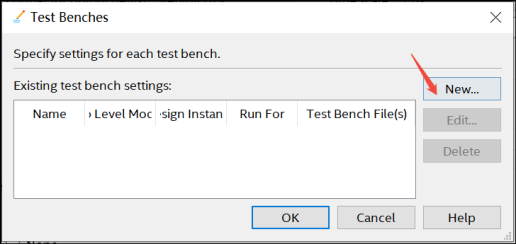

8. 點擊New...

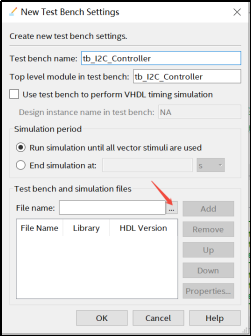

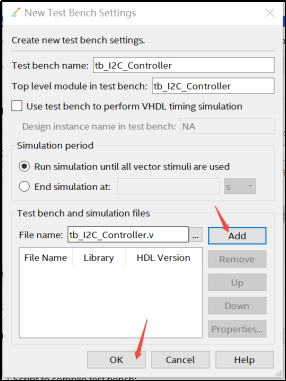

9. 然后填寫Test bench name 名稱為tb_I2C_Controller,接著點擊File name處對應的...按鈕:

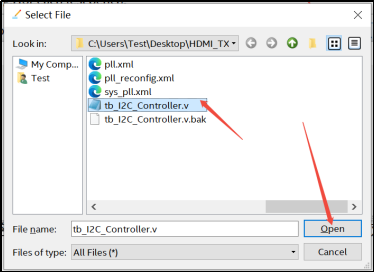

10. 選擇tb_I2C_Controller.v文件,然后點擊Open:

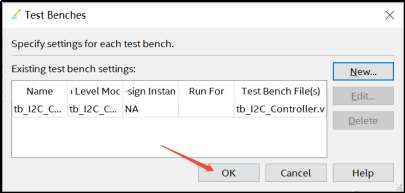

11. 接著點擊Add將仿真文件添加到Test Bench,依次點擊OK、OK、Apply和 OK退出窗口:

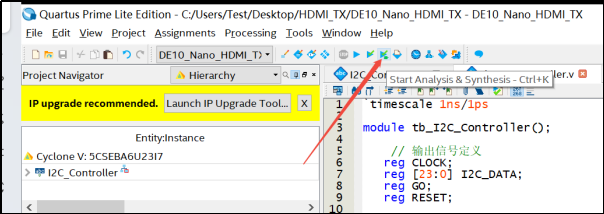

12. 在仿真之前要先點擊Start Analysis&Synthesis按鈕進行分析和綜合:

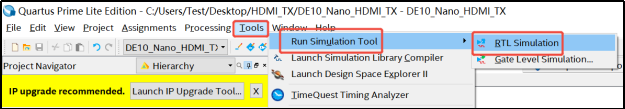

13. 再點擊Tools——Run Simulation Tool_RTL Simulation進行仿真:

14. 點擊Zoom Full按鈕將顯示全部波形。

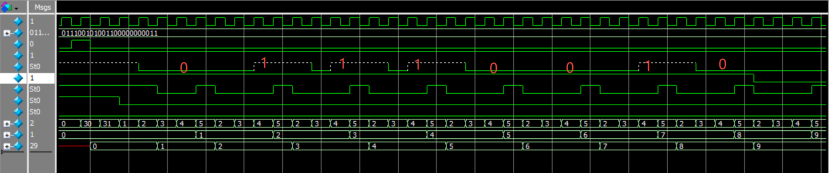

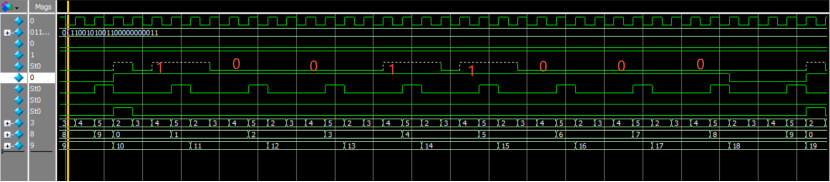

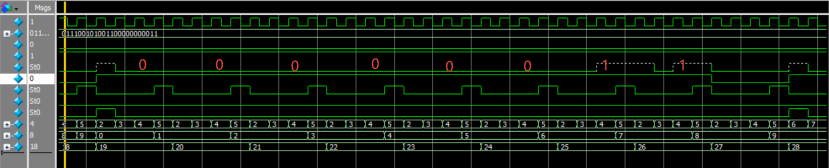

15. 最后波形生成如下:

通過波形可以看到,用于觸發I2C寫操作的GO信號拉高一個時鐘周期后,I2C開始寫數據的操作。現在要寫的數據是24'h729803,二進制是0111_0010_1001_1000_0000_0011, 將波形放大分三段截圖將看到如下內容:

數據發送的狀態循環是ST=2 → ST=3 → ST=4 → ST=5 → ST=2,這個循環發送1位數據,共循環9次(8位數據+ACK),第9位(1'b1)是確保在第9個時鐘周期主機釋放SDA總線。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636229 -

I2C

+關注

關注

28文章

1556瀏覽量

131218 -

ModelSim

+關注

關注

5文章

175瀏覽量

49277 -

仿真軟件

+關注

關注

21文章

281瀏覽量

31837

原文標題:6-DE10-Nano的HDMI方塊移動案例——使用Modelsim仿真I2C控制器

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

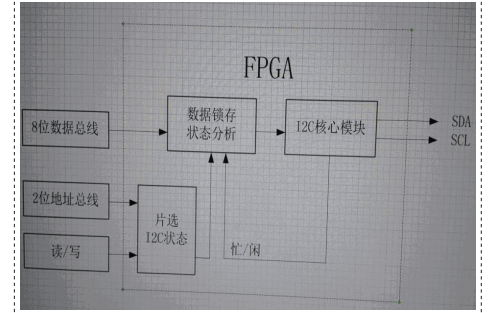

基于FPGA的I2C SLAVE模式總線的設計方案

新手求助,I2C總線從機的應答信號不能用modelsim仿真出?

實現I2C總線控制器的VHDL源代碼

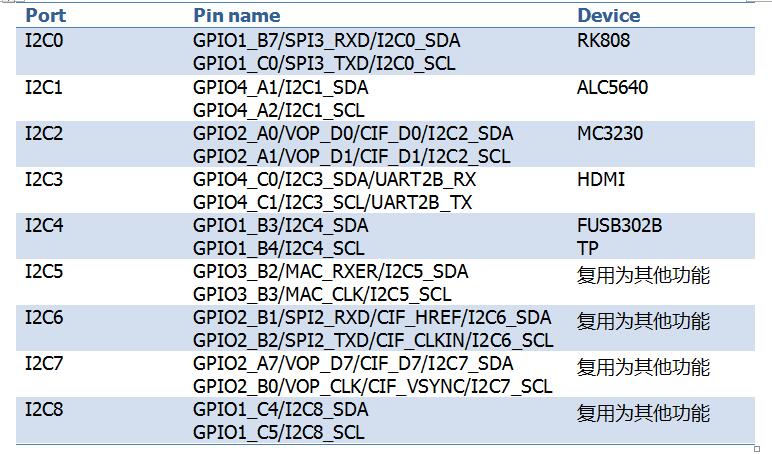

基于Verilog的I2C控制器的設計與綜合

I2C總線控制器的工作原理及EEPROM的Linux驅動程序的設計

使用FPGA實現I2C總線主機控制器的應用實例資料免費下載

硬件I2C與模擬I2C

如何使用Modelsim仿真I2C控制器

如何使用Modelsim仿真I2C控制器

評論