模塊是Verilog 的基本描述單位,用于描述某個設計的功能或結構及其與其他模塊通信的外部端口。一個設計的結構可使用開關級原語、門級原語和用戶定義的原語方式描述; 設計的數據流行為使用連續賦值語句進行描述; 時序行為使用過程結構描述。一個模塊可以在另一個模塊中使用。

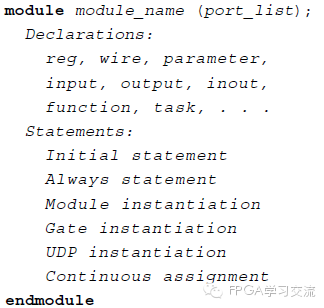

一個模塊的基本語法如下:

說明部分用于定義不同的項,例如模塊描述中使用的寄存器和參數。語句定義設計的功能和結構。說明部分和語句可以散布在模塊中的任何地方;但是變量、寄存器、線網和參數等的說明部分必須在使用前出現。為了使模塊描述清晰和具有良好的可讀性, 最好將所有的說明部分放在語句前。本書中的所有實例都遵守這一規范。

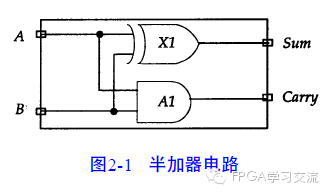

圖2 - 1為建模一個半加器電路的模塊的簡單實例。

模塊的名字是H a l f A d d e r。模塊有4個端口: 兩個輸入端口A和B,兩個輸出端口S u m和C a rry。由于沒有定義端口的位數, 所有端口大小都為1位;同時, 由于沒有各端口的數據類型說明, 這四個端口都是線網數據類型。模塊包含兩條描述半加器數據流行為的連續賦值語句。從這種意義上講,這些語句在模塊中出現的順序無關緊要,這些語句是并發的。每條語句的執行順序依賴于發生在變量A和B上的事件。

在模塊中,可用下述方式描述一個設計:

1) 數據流方式;

2) 行為方式;

3) 結構方式;

4) 上述描述方式的混合。

原文標題:Verilog HDL硬件描述語言-模塊

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

模塊

+關注

關注

7文章

2837瀏覽量

53294 -

HDL

+關注

關注

8文章

332瀏覽量

48978

原文標題:Verilog HDL硬件描述語言-模塊

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Verilog HDL語法學習筆記

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

如何使用Modelsim仿真I2C控制器

【產品介紹】Modelsim:HDL語言仿真軟件

使用NucleiStudio生成tb仿真需要的.verilog文件

復雜的軟件算法硬件IP核的實現

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

使用Simulink自動生成浮點運算HDL代碼(Part 1)

e203自定義指令硬件模塊設計不工作是怎么回事?

一文詳解Verilog HDL

千兆網絡PHY芯片RTL8211E的實踐應用

Verilog HDL硬件基本描述單位模塊

Verilog HDL硬件基本描述單位模塊

評論