本文轉載自:VagueCheung的博客

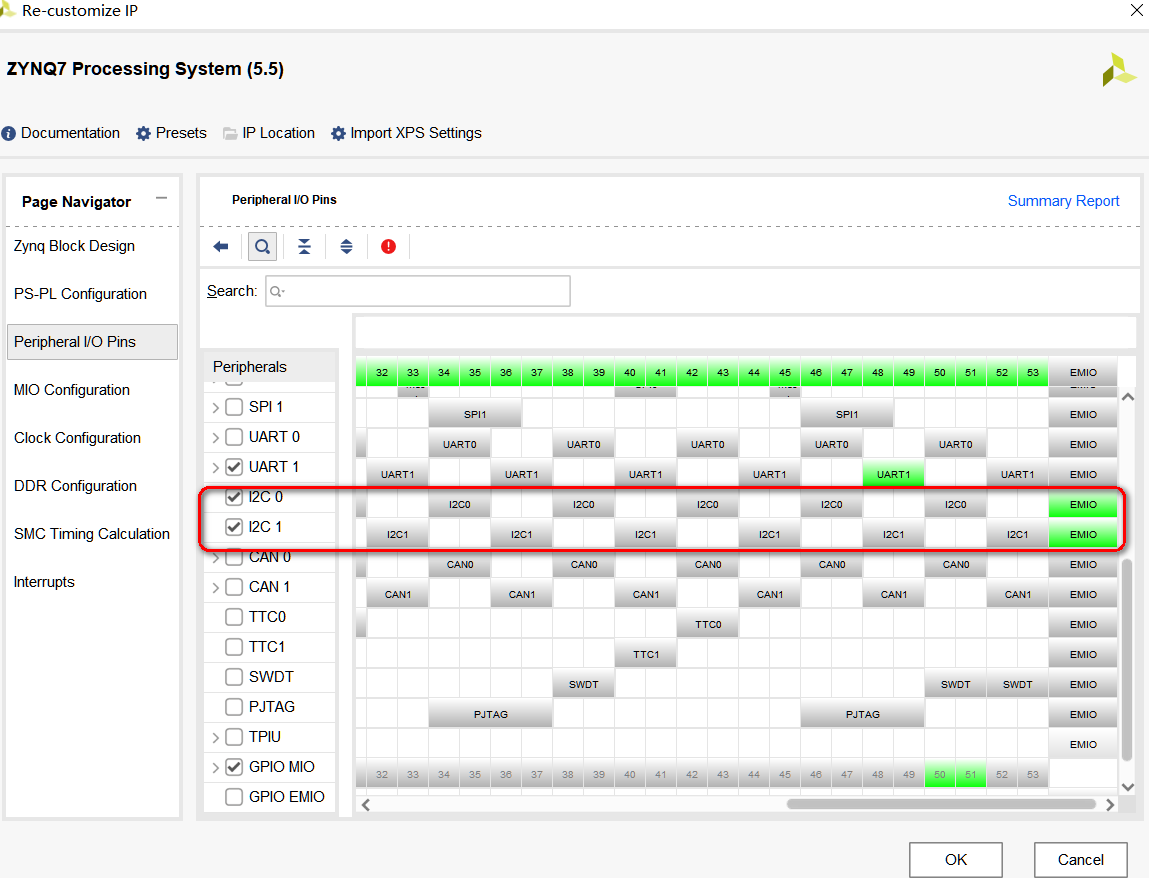

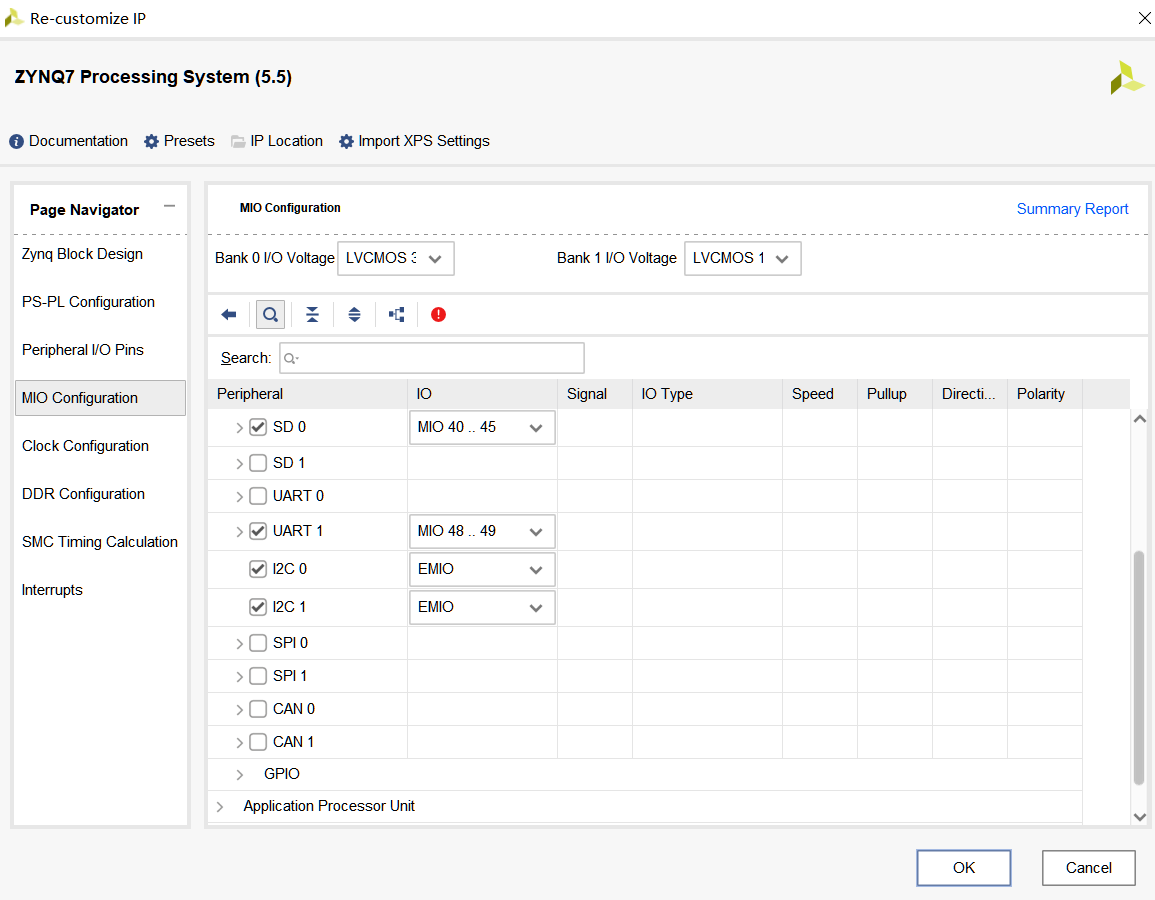

ZYNQ7000系列FPGA的PS自帶兩個IIC接口,接口PIN IO可擴展為EMIO形式即將IO約束到PL端符合電平標準的IO(BANK12、BANK13、BANK34、BANK35);

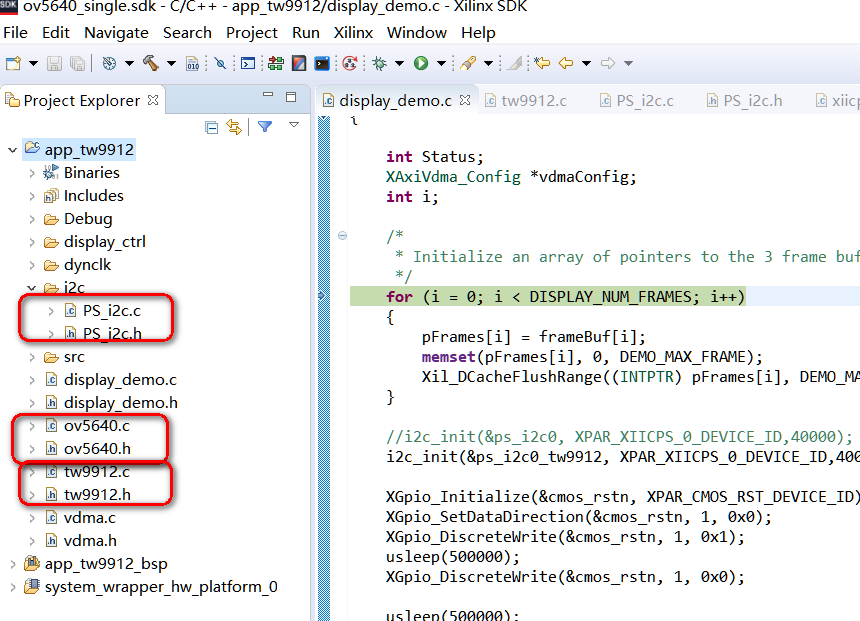

SDK中需要對IIC接口進行初始化在黑金和米聯的例程里為了方便用戶使用,對IIC和外設設備分別創建了相應的文件方便用戶開發。

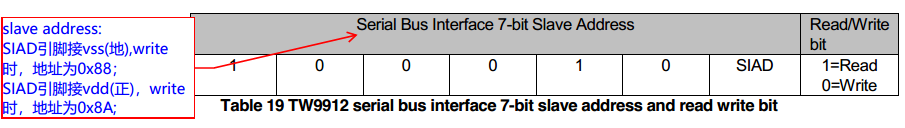

特別注意每個外設設備都會有自己的slave address;而xilinx官方給出的IIC驅動中給出的從設備的地址是7bit模式(IIC總線上的器件一般為8位地址位,去掉低位一位廣播位,最多可掛載127個設備),在IIC進行寫操作時注意要將設備原有的salve address轉化成7bit模式;否則從設備將無法給予應答。

例如tw9912

在SDK中IIC進行寫操作時。從設備地址slave address就應設置為0x44/0x45;

IIC總線數據傳輸速率(波特率)快速模式下可達到400kbit/s;

審核編輯 黃昊宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

IIC接口

+關注

關注

0文章

23瀏覽量

12049 -

Zynq-7000

+關注

關注

3文章

144瀏覽量

38099

發布評論請先 登錄

相關推薦

熱點推薦

XC7Z020-2CLG484I 雙核異構架構 全能型 SoC

Zynq-7000 系列的核心型號,創新性地將雙核 ARM Cortex-A9 處理器與 7 系列 FPGA 可編程邏輯深度集成,構建起 “軟件可編程 + 硬件可定制” 的異構計算架構,為多領域智能設備提供了一體化

發表于 02-28 23:37

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

在之前文章中,我們介紹了如何使用 XSCT 工具通過 JTAG 在 Zynq SoC 上啟動嵌入式 Linux 鏡像(從 JTAG 啟動 Zynq-7000 嵌入式 Linux:使用 XSCT 全

雙Zynq MPSoC PS側PCIe高速DMA互連解決方案

在涉及Xilinx Zynq UltraScale+ MPSoC的項目中,實現設備間高速、低延遲的數據傳輸往往是核心需求之一。PCIe(尤其PS側)結合DMA(直接內存訪問)正是滿足這類需求的理想技術方案。

Zynq7100 BSP移植,MSH終端不能正確顯示是為什么?

由于新版本的RT Thread的BSP不再提供Zynq7000的支持。所以同事從RT Thread(4.0.3)中的Zynq7000移植了一份Zynq 7100的BSP。但是MSH終端和串口輸出

發表于 09-19 06:26

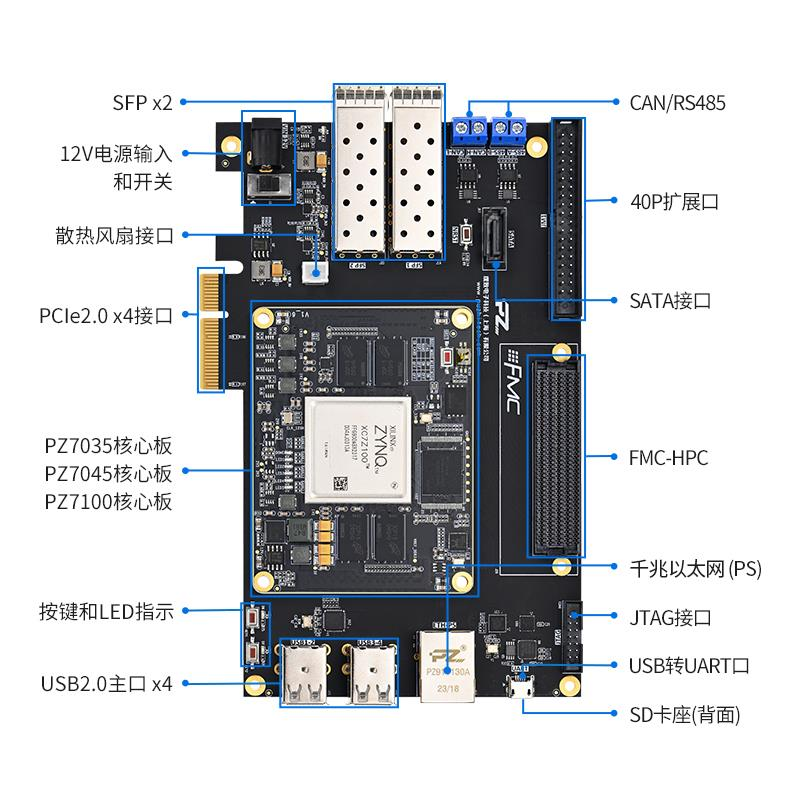

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

本文介紹了Xilinx Zynq-7000系列可擴展處理平臺及其開發板應用。Zynq-7000采用雙核ARM Cortex-A9處理器與28nm FPGA架構,支持高性能嵌入式開發。開發板采用核心板

Zynq-7000 SoC與7系列設備內存接口解決方案數據手冊

關于 AMD/Xilinx 7系列FPGA存儲器接口解決方案(UG586) 的用戶指南,其主要內容和技術要點可概括如下:1. 文檔定位與核心內容定位:該文檔是7系列FPGA中存儲接口控制器的官方

發表于 07-28 16:17

?3次下載

用IIC接口的IIC_SCL和IIC_SDA引腳做普通GPIO,程序啟動不起來怎么解決?

想用IIC接口的IIC_SCL和IIC_SDA引腳做普通GPIO,兩個引腳對應的是GPIO58和GPIO59,更改代碼將設置為普通GPIO引腳模式后,程序啟動不起來。問:這種情況如何解

發表于 05-06 08:59

Zynq-7000 PS端IIC接口使用筆記

Zynq-7000 PS端IIC接口使用筆記

評論