作者:Hello,Panda

這次分享一個在Xilinx FPGA實現MIPI DPHY接口的案例(包括CIS協議層)。截止目前為止,Xilinx僅在Ultrascale+及其以上版本的FPGA IO可直接支持MIPI 電平輸入,其他的,都需要轉換成LVDS來接收。在軟件支持上,Xilinx在高版本的Vivado(Vitis)上開放了MIPI DPHY IP,但是這個IP可能用起來有諸多的限制,比如說,不可以動態切換Lane速率、比如說必須是Gated的時鐘、比如說所有時鐘通道和數據Lane的LP信號都必須接進來占用很多IO等等。所以,熊貓君在這里分享手動擼代碼的途徑,根據自己的需求想做成啥樣就啥樣,哪管它格式千奇百怪,另外給大家分享的是,擼這個代碼不用怕,真的很簡單,熟練一些的三天就成,不太熟練的也就一個星期,畢竟咱們不需要把協議棧的每個邊邊角角都整出來,夠咱用就可以了。好了,不說廢話了,咱們以MIPI DPHY CSI為例預備開始,搭建一個MIPI RX攝像頭數據的案例!

一、 硬件上的考慮

之前咱不是介紹過,Xilinx低版本的FPGA上并不能直接支持MIPI DPHY電平標準,因此不能直接就把攝像頭接到FPGA的Select IO上,咱得想辦法把它變成可以認識的LVDS電平。

1. 速率的考慮

為什么說要考慮速率呢?這里一個是和FPGA內部的資源相關,另外一個是和信號完整性相關。

FPGA內部的資源是怎么個說法呢?因為是要用到Select IO的Iserdes,因此受IO時鐘速率的影響,可以布線到IO的最高時鐘在7系列器件里面是BUIO,可以達到800MH(Spartan-6的BUFPLL可能低一些,記得好像是600MHz來著的,有需要的可以自行查證),那么就意味著在7系列FPGA上接MIPI進來最大的Lane速率只能到1600Mbps。

另外,信號完整性是怎么一個說法呢?咱們這個畢竟是高速信號,對眼圖采樣窗口什么很看重的,這方面Xilinx很有經驗,它給畫了一條線:800Mbps,lane速率低于800Mbps的,可以通過電阻網絡用很低的成本就把事兒給辦了;但是速度高了可不行,采樣可能就不正確了,那怎么辦呢?就得用專門的level shift芯片將MIPI信號轉成LVDS了。

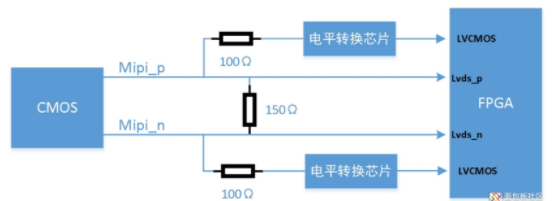

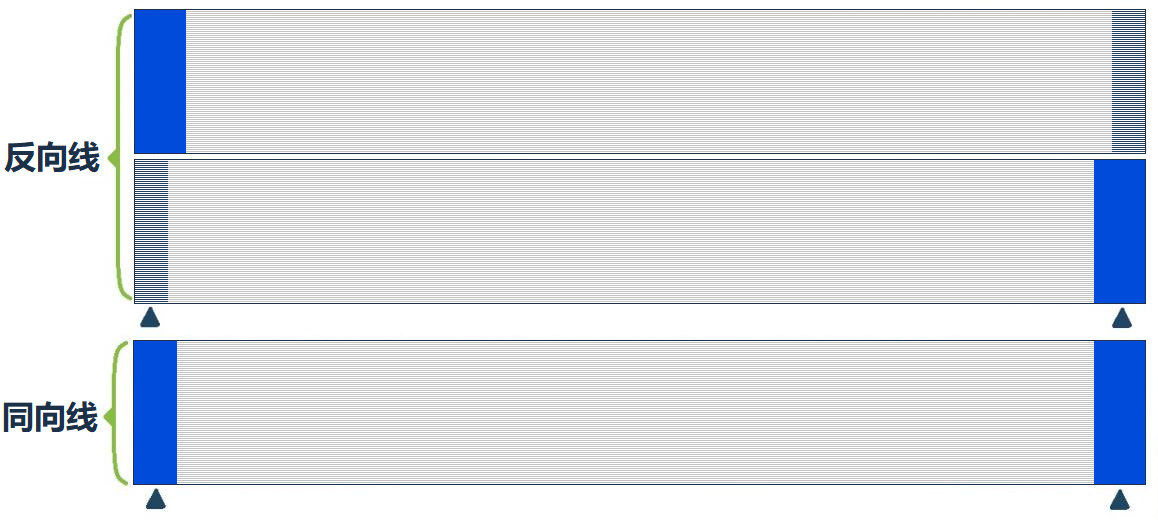

2. 使用電阻網絡

這種方法尤其簡單,說白了,對接收端來說尤其簡單,說白了,就是說你MIPI電平的擺幅很低,那好啊,我把終端電阻加大(150Ω,需要注意的是內部的DIFF_TERM要False掉)一點兒,可以確保差分終端電阻兩端的電壓夠LVDS的裁決門限就行了,這個Xilinx還專門有一個xapp的參考設計,具體編號沒有記,有需要可以自行去找DoCNav要。至于低速LP信號,分出來以后要是BANK富裕可以專門搞一個1.2V的bank,如果不富裕,也可以加一個輸入阻抗很大的電平轉換芯片(比如74LVC1T45)把它轉成任意你想要的電平標準,比如1.8V、2.5V或3.3V。那么,整個輸入的網絡結構就變成了圖1這個樣子的了。

圖1 電阻網絡結構圖

至于哪些信號要接進來,如果引腳足夠多,那么所有LP信號和HS信號都可以接進來,如果不富裕且不需要用到嵌入的低速數據的話,因為咱們的Lane已知,除了HS信號外,將lane0的LP信號接進來用于狀態判斷就行了。

低速的適用于大多數分辨率/幀率在1080P60及以下的,比如幾乎所有的內窺鏡用Sensor,如最常用OV9734;大部分的Sony和安森美的2M監控芯片。

3. 使用專門的電平Level shift芯片

因為基本上MIPI還是用于手機和監控類居多,一般的SoC都支持MIPI直接輸入。這方面的電平轉換不多,一個是使用專用芯片,比如說國外的MC20901之類的芯片,另外國內的龍迅也有類似的。

另外一種就是采用高速的信號buffer/repeater芯片轉成LVDS信號,TI有很多種這樣的芯片,比如說性能頂尖的DS25BR100(足以滿足2.5Gbps MIPI,帶均衡和加重的),當然這個性能好意味著高價格,對于速度沒有那么高的應用,選稍次一檔的也很香,電路結構和圖1類似,就是把150Ω電阻的位置換成這個buffer/repeater芯片,輸出就直接是LVDS到FPGA了,標標準準的。

這種方案適合800Mbps~1600Mbps應用場景,除了一些極大靶面或者極高幀率的Sensor外,大多數的一般sensor都包含在內了。

4. 超過1.6Gbps怎么辦

還有一種情況,就是必須要用到lane速率超過1.6Gbps,這種情況怎么辦呢?那就得用到高速serdes了GTP、GTH、GTY了,針對這種情況,Xilinx專門出了一個應用指南,這個比較特殊,熊貓君記得編號是XAPP1339,名字叫做“Implementing 2.5G MIPI D-PHY Controllers”,前提是FPGA需要帶高速Serdes,成本要高一些,Xilinx官網有參考設計,在安富利可以買到評估板,如下圖2所示,本文按下不表。

圖2 安富利使用高速Serdes的參考板

二、 軟件設計

這里的軟件設計只考慮介紹手擼的,對Xilinx官方IP和參考設計不做表述。這里面主要的關鍵點是考慮使用什么樣的時鐘網絡拓撲。

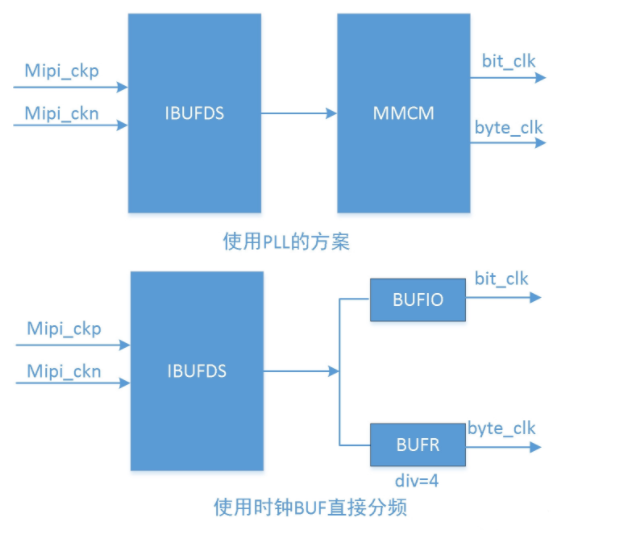

1. 兩種時鐘拓撲的考量

這里面有種時鐘架構可供選擇,各有優缺點,根據實際情況選擇之。

第一種是使用鎖相環(PLL):這種方案的有點是時鐘穩定、抖動小,外部偶爾有個小毛刺可能影響不大,缺點一個是需要考慮失鎖的問題,這個對連續時鐘輸出的沒啥影響,但是對Gated時鐘就比價致命,如果低功耗間隔太長,重新轉到高速模式時間又太短,很有可能鎖相環就失鎖了,導致丟掉了HS幀前面的一部分數據找不到同步頭接收失敗;另一個是只能支持一種固定速率。因此,在選用這種方案的時候要特別注意。

第二種方案是直接使用時鐘BUFER:這種方案無需知道進來的時鐘速率是多少,所以可以很方便的通過配置sensor的寄存器來切換MIPI通道lane速率(這種對大靶面的傳感器應用尤為常見,拍照和視頻流采用不同的輸出速率)。缺點是容易受外界干擾,對信號完整性和干擾屏蔽處理要求較高。

這個兩種時鐘方案的結構如下圖3所示。

圖3 兩種時鐘拓撲結構

對MIPI而言,數據并串轉換的最小單位是字節,DDR采樣方式,因此byte_clk頻率是bit_clk的1/4。

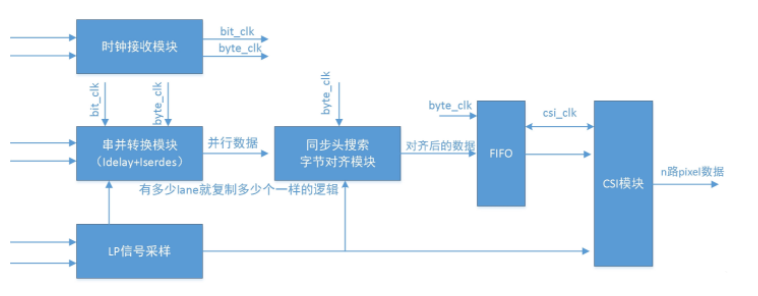

2. 物理層的接收

咱們一般而言不考慮雙向通信和ESCAPE信號處理,那么MIPI D-PHY物理層的主要工作就是采樣LP狀態信號和將高速串行數據恢復成按字節排序的并行數據,不管多少個Lane,方法都一個樣。這個工作被稱作解串,只需要用到IDELAY和ISERDES原語就行。MIPI標準默認是時鐘相對數據的相位是90°,DDR采樣方式,也就是說,時鐘的上升沿和下降沿剛好在數據的中間,因此在PCB Layout的時鐘,時鐘和數據最好是需要等長的,這樣保證到達時間是一樣的。IDELAY的作用是將PCB布線和內部路徑的延時找回來使之滿足最佳采樣要求,這在直接使用時鐘BUFER的時鐘拓撲設計中尤為重要,另外,因每次布局布線后都會存在一些路徑差異,最好是約束Fixed布線路徑。ISERDES的作用是串轉并,將數據轉為并行的,這里的串并比設為1:8就好,至于這倆源語怎么用,可以參照Xilinx的Select IO手冊或者參照我上一篇分享文章《Zynq高速串行CMOS接口設計與實現》。

恢復成字節數據的第二步就是找同步頭B8’H,這里千萬不要用Iserdes自帶的bitslip功能,因為同步字每一個HS幀就一個字節,而且每一個HS幀都要搜索同步字節。一次這里需要手擼一小段代碼自己來截取為最好。

3. CSI層的實現

CSI層主要就是將1lane,或多lane的數據按照協議規定解析出來并將圖像數據拼接輸出,有的可能會存在多個虛擬通道,需要注意一下。MIPI 一般會分為長短幀,長幀為數據幀,一幀一般就是一行數據;短幀為標志幀,用于指示幀行的開始結束,這個我們可以根據自己的Sensor實現一種就行了,沒有必要像標準那樣把所有的數據類型都囊括進來。

這里需要注意一下的是,MIPI DPHY和CPHY的長幀的幀頭排列方式不一樣,CPHY是固定的每個通道都有6個word的的幀頭信息。但是DPHY的幀頭信息排布和數據一樣,都是根據實際的通道數分散到各通道。

CSI層的工作時鐘可以使用FPGA內部的一個合適時鐘,不和MIPI的像素時鐘掛鉤,從CSI層出來的數據就是直接的一個一個的像素數據了。

針對特定的Sensor實現CSI層,整個MIPI的接收邏輯框圖如下圖4所示,整個接收邏輯所占用的Slice資源一般不會大于1K。

圖4 MIPI DPHY接收邏輯設計框圖

編輯:hfy

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638506 -

信號完整性

+關注

關注

68文章

1490瀏覽量

98210

發布評論請先 登錄

基于智多晶FPGA的DVP轉MIPI CSI-2視頻傳輸方案

SNx5DPHY440SS MIPI? CSI - 2/DSI DPHY重定時器:設計與應用解析

SNx5DPHY440SS:MIPI? CSI - 2/DSI DPHY重定時器的深度解析

0.4 至 2.7 GHz LTE 分集接收模塊,帶 MIPI RFFE 接口 skyworksinc

如何在智多晶FPGA上使用MIPI接口

嵌入式接口通識知識之MIPI接口

0.4 至 2.7 GHz LTE 分集接收模塊,帶 MIPI? RFFE 接口 skyworksinc

正點原子AU15開發板資料發布!板載40G QSFP、PCIe3.0x8和FMC LPC等接口,性能強悍!

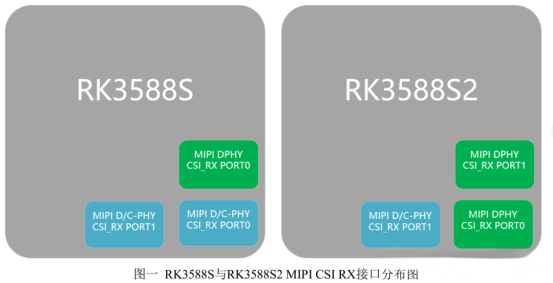

RK3588S和RK3588S2差異說明

基于RK3576開發板的MIPI-DSI使用

基于高云Arora-V 60K FPGA實現的MIPI CPHY轉MIPI DPHY透傳模塊

基于Xilinx FPGA實現MIPI DPHY接口案例分析

基于Xilinx FPGA實現MIPI DPHY接口案例分析

評論