SNx5DPHY440SS:MIPI? CSI - 2/DSI DPHY重定時器的深度解析

在電子設備飛速發展的今天,高速數據傳輸的穩定性和可靠性愈發重要。MIPI? CSI - 2/DSI接口在移動設備、攝像頭等領域得到了廣泛應用,而SNx5DPHY440SS作為一款MIPI? CSI - 2/DSI DPHY重定時器,為數據傳輸提供了有力保障。今天,我們就來深入探討一下這款器件。

文件下載:sn65dphy440ss.pdf

一、特性亮點

1. 標準兼容性與速率支持

SNx5DPHY440SS符合MIPI? DPHY 1.1規范,這意味著它能夠很好地融入現有的MIPI生態系統。在速率方面,它在1.5Gbps速率下最多支持4條通道,CSI - 2/DSI時鐘速率范圍為100MHz至750MHz,能夠滿足大多數應用場景的需求。

2. 低功耗設計

在關斷狀態下,其功耗低于1mW,這對于追求低功耗的移動設備來說至關重要。同時,它支持MIPI? DSI雙向LP模式以及ULPS和LP功耗狀態,進一步降低了系統的整體功耗。

3. 信號調節能力

該器件具備可調輸出電壓擺幅、可選TX預加重電平以及可調RX EQ等功能。可調輸出電壓擺幅可以根據實際需求調整信號的強度,可選TX預加重電平有助于補償信號在傳輸過程中的衰減,可調RX EQ則能有效補償ISI損耗,確保信號的質量。

4. 其他特性

可配置邊沿速率控制能夠優化信號的上升和下降時間,動態數據和時鐘偏移補償則保證了數據和時鐘的同步性。此外,它還具備3kV的ESD HBM保護,能夠在復雜的電磁環境中穩定工作。在溫度范圍方面,SN65DPHY440SS支持工業溫度范圍(–40°C至85°C),SN75DPHY440SS支持商用溫度范圍(0°C至70°C),由1.8V單電源供電,使用起來非常方便。

二、應用場景

SNx5DPHY440SS的應用范圍十分廣泛,主要包括筆記本電腦、掀合式電腦、平板電腦以及攝像頭等設備。在這些設備中,它能夠有效改善MIPI? CSI - 2/DSI信號的傳輸質量,提高系統的穩定性和性能。

三、器件說明

1. 功能概述

DPHY440是一款1至4通道時鐘MIPI? DPHY重定時器,用于重新生成DPHY信令。它符合MIPI? DPHY 1.1標準,可用于數據速率高達1.5Gbps的MIPI? CSI - 2或MIPI? DSI應用。該器件能夠補償PCB、連接器和電纜相關的頻率損耗和開關相關損耗,在CSI - 2/DSI源設備和接收設備之間提供最佳的DP電氣性能。

2. 輸入輸出特性

DPHY440的DPHY輸入端具有可配置的均衡器,能夠根據實際情況調整信號的補償程度。輸出引腳會自動補償在器件輸入端口上接收的時鐘和數據間的不一致偏移,確保輸出信號的準確性。其輸出電壓擺幅和邊沿速率可分別通過更改VSADJ_CFG0引腳和ERC引腳的狀態進行調節,為工程師提供了靈活的配置選項。

3. 低功耗優化

DPHY440針對移動應用進行了優化,在DPHY鏈路接口上裝有活動檢測電路。當檢測到ULPS和LP狀態時,它會切換到低功耗模式,進一步降低功耗。

4. 溫度范圍

SN65DPHY440SS可在–40°C至85°C的工業級溫度范圍內運行,SN75DPHY440SS可在0°C至70°C的商業級溫度范圍內運行,能夠適應不同的工作環境。

四、引腳配置與功能

1. 輸入引腳

該器件有多個輸入引腳,如CSI - 2/DSI Lane 0至3的差分正、負輸入引腳(DA0P、DA0N等)以及CSI - 2/DSI差分時鐘正、負輸入引腳(DACP、DACN)。這些引腳支持DSI LP Backchannel,若未使用,應將其接地。

2. 輸出引腳

輸出引腳包括CSI - 2/DSI Lane 0至3的差分正、負輸出引腳(DB0P、DB0N等)以及CSI - 2/DSI差分時鐘負輸出引腳(DBCN)。若未使用,這些引腳應保持不連接。

3. 控制引腳

VCC為1.8V(±10%)的電源引腳,VREG_OUT為1.2V的穩壓器輸出引腳,需要連接一個0.1μF的電容到地。EQ/SCL引腳用于控制HS RX均衡,ERC/SDA引腳用于控制HS TX邊沿速率。PRE_CFG1引腳控制DPHY TX HS預加重電平和LP TX上升、下降時間,VSADJ_CFG0引腳控制輸出電壓擺幅和LP TX上升、下降時間。RSTN為復位引腳,低電平有效,當為低電平時,所有內部CSR復位到默認值,DPHY440進入低功耗狀態。

五、規格參數

1. 絕對最大額定值

包括電源電壓范圍、DPHY Lane I/O差分電壓、RSTN電壓等參數的最大和最小值。例如,電源電壓范圍VCC為–0.3V至2.175V,最大結溫TJ為105°C,存儲溫度Tstg為–65°C至150°C。超過這些額定值可能會對器件造成永久性損壞。

2. ESD額定值

人體模型(HBM)為±3000V,帶電設備模型(CDM)為±1000V,表明該器件具有較好的靜電防護能力。

3. 推薦工作條件

推薦的VCC電源電壓為1.62V至1.98V,SN65DPHY440SS的工作溫度范圍為–40°C至85°C,SN75DPHY440SS的工作溫度范圍為0°C至70°C。

4. 熱信息

包括結到環境的熱阻RθJA、結到外殼(頂部)的熱阻RθJC(top)等參數,這些參數對于散熱設計非常重要。

5. 電氣特性

涵蓋了電源功耗、輸入輸出電壓、電流等方面的特性。例如,在正常工作時,4數據通道 + 時鐘的功耗PACTIVE1 SS為150mW,2數據通道 + 時鐘的功耗PACTIVE2 SS為115mW。

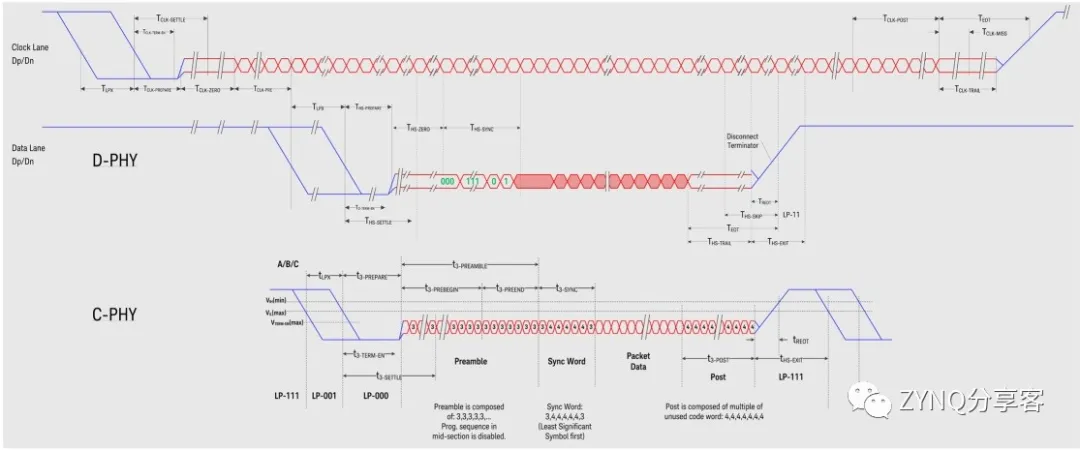

6. 時序要求

包括I2C和MIPI DPHY HS接口的各種時序參數,如I2C的時鐘頻率fCLK為0至100kHz,MIPI DPHY HS接口的傳播延遲tHSPD為4 + 12ns至4 + 40ns UI等。

六、詳細描述

1. 功能框圖

DPHY440的功能框圖展示了其內部的各個模塊,包括輸入輸出模塊、均衡器模塊、動態去斜模塊等,有助于我們理解其工作原理。

2. 特性描述

(1)HS接收均衡

支持三個級別的接收均衡,分別為0dB、2.5dB和5dB(750MHz時),通過EQ/SCL引腳的狀態來確定使用的均衡級別,也可通過本地I2C接口寫入RXEQ寄存器進行設置。

(2)HS TX邊沿速率控制

支持控制DB[3:0]P/N和DBCP/N高速(HS)發射機的上升和下降時間,通過ERC/SDA引腳的采樣狀態來確定HS邊沿速率設置,也可通過本地I2C接口寫入HS_ERC寄存器進行調整。同時,還支持LP接口的邊沿速率控制。

(3)TX電壓擺幅和預加重控制

提供兩個級別的預加重(0dB和2.5dB),通過PRE_CFG[1:0]引腳的采樣狀態來確定TX預加重設置,也可通過本地I2C接口寫入HSTX_PRE寄存器進行調整。但該功能僅在HS預加重位(過渡位)被通道衰減時使用,否則可能會對系統性能產生負面影響。

(4)動態去斜

實現了動態去斜功能,能夠連續對DA[3:0]P/N接口上接收到的HS數據進行去斜處理,并在DB[3:0]P/N接口上提供重新定時的版本。該功能僅在HS模式下啟用,會導致數據從DA到DB有2個時鐘(4 UI)的延遲。

3. 器件功能模式

(1)關機模式

通過將RSTN引腳置為低電平,同時保持穩定的VCC和VDD電源供應,可將DPHY440置于低功耗狀態。在關機狀態下,DB[3:0]P/N和DBCP/N引腳被驅動到LP00狀態,器件忽略DA[3:0]P/N和DACP/N引腳上的所有活動。當RSTN引腳置為高電平時,退出關機模式,進入LP模式。

(2)LP模式

在該模式下,DPHY440在DA[3:0]P/N和DB[3:0]P/N之間傳遞LP信號,HS接收器和HS發射機的內部終端被禁用。MIPI DSI規范定義了主機和外設之間的雙向通信,DPHY440僅支持通過通道0(DB0P/N到DA0P/N)進行這種通信,其余通道不能用于從外設到主機的LP通信。

(3)ULPS模式

DPHY440會持續監測DPHY LP協議,當進入ULPS狀態時,保持LP信令所需的邏輯(LP rx、LPtx、LP狀態機等)處于活動狀態,禁用HS操作所需的所有邏輯,從而實現更低的功耗狀態。需要注意的是,ULPS模式只能從LP模式進入。

(4)HS模式

當LP狀態機檢測到所需的LP信號序列時,進入HS模式。在該模式下,HS接收器和HS發射機的內部終端啟用,動態去斜功能也被啟用。

4. 寄存器映射

DPHY440的本地I2C接口在RSTN輸入為高電平時啟用,支持在超低功耗狀態(ULPS)下訪問CSR寄存器。EQ/SCL和ERC/SDA端子分別用于I2C時鐘和I2C數據,I2C接口符合I2C總線規范2.1版本,支持最高100kHz的速率。器件地址字節為控制器設備發送START條件后接收到的第一個字節,7位器件地址為1101100。通過特定的讀寫操作流程,可以對DPHY440的I2C寄存器進行讀寫操作。

七、應用與實現

1. 應用信息

DPHY440支持最多4個DSI DPHY通道和一個時鐘通道,其中通道0用于GPU和DSI面板之間的反向通道通信,因此DPHY440的通道0必須始終連接到GPU和面板的通道0。對于所有DSI實現,必須保持DSI源和DSI接收器之間的極性一致,DPHY440不支持極性反轉。

2. 典型應用 - CSI - 2實現

DPHY440支持4個CSI - 2 DPHY通道加一個時鐘通道,與DSI不同,CSI - 2沒有反向通道路徑,因此對通道順序沒有要求,有更多的組合可以實現。對于所有CSI - 2實現,同樣需要保持CSI - 2源和CSI - 2接收器之間的極性一致。

3. 設計要求

在CSI - 2應用中,從相機(源)到DPHY440設備的系統走線長度通常與從DPHY440到APU(接收器)的走線長度不同,因此需要在器件的接收器和發射機側分別設置不同的預加重和均衡設置。

4. 詳細設計過程

根據源(相機)和DPHY440之間以及DPHY440和接收器(APU)之間的板級走線長度,配置DPHY440的VSADJ、PRE、EQ和ERC配置引腳。實際的配置設置可能會因板級布局、信號路徑中使用的連接器等因素而有所不同。

5. 復位實現

DPHY440的RSTN輸入用于控制設備復位并將設備置于低功耗模式。在VCC電源穩定后,必須對DPHY440的數字邏輯進行復位,可通過將RSTN輸入從低電平轉換為高電平來實現。可以通過系統提供的控制信號或連接外部電容來延遲RSTN信號在電源上電時的變化。

6. 應用曲線

應用曲線展示了不同頻率下的損耗特性,有助于我們了解信號在傳輸過程中的損耗情況,從而合理設置EQ等參數。

7. 電源供應建議

德州儀器建議在每個電源引腳上使用0.1μF的電容,以確保電源的穩定性。

8. 布局

(1)布局指南

DAxP/N和DB*P/N對應采用受控的100 - Ω差分阻抗(±15%)或50 - Ω單端阻抗(±15%)進行布線,盡量遠離其他高速信號,保持走線長度相差在5mils以內,長度匹配應盡量靠近不匹配的位置。每對走線之間應至少間隔3倍的信號走線寬度,差分走線中的彎曲應盡量減少,彎曲時左右彎曲的數量應盡量相等,彎曲角度應≥135度。所有差分對應在同一層布線,盡量減少過孔數量,建議過孔數量不超過2個,走線應靠近接地平面,避免差分對跨越任何平面分割。如果使用測試點,應將其串聯且對稱放置,避免在差分對上形成短截線。

(2)布局示例

給出了一個布局示例,直觀地展示了如何進行合理的布局,幫助工程師更好地進行實際設計。

八、總結

SNx5DPHY440SS作為一款優秀的MIPI? CSI - 2/DSI DPHY重定時器,具有豐富的特性和廣泛的應用場景。在設計過程中,我們需要根據具體的應用需求,合理配置其引腳和寄存器,同時注意電源供應、布局等方面的問題,以充分發揮其性能優勢。希望本文能夠為廣大電子工程師在使用SNx5DPHY440SS進行設計時提供一些參考和幫助。大家在實際應用中遇到過哪些問題呢?歡迎在評論區留言討論。

發布評論請先 登錄

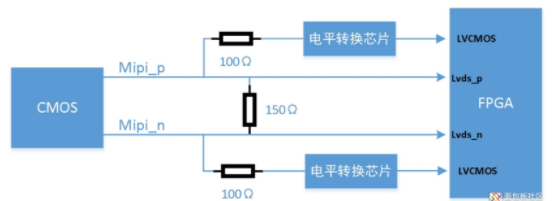

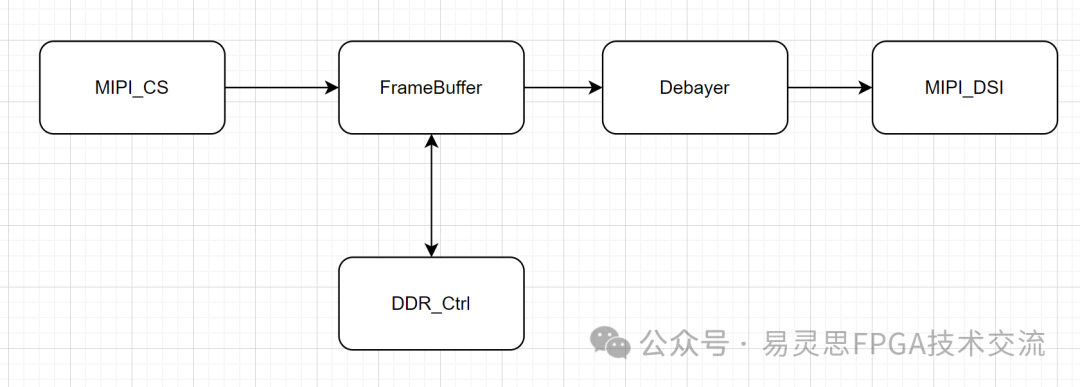

基于Xilinx FPGA實現MIPI DPHY接口案例分析

MIPI2.5G DPHY CSI2DSI demo移植 -v1

SN65DPHY440SS 4組數據輸入輸出的內部結構是否一樣?

請問SN65DPHY440SS最大能支持多長的FPC?

關于SN65DPHY440SS這顆芯片的使用

RK3566/RK3568平臺上的Camera使用指南

請問RK3568 MIPI RX DPHY接收MIPI協議的是否同時支持CSI與DSI兩種協議?

SN75DPHY440SS MIPI? CSI-2/DSI DPHY 重定時器

SN65DPHY440SS SN65DPHY440SS CSI-2/DSI DPHY 重定時器

SNx5DPHY440SS CSI-2/DSI DPHY 重計時器數據表

基于高云Arora-V 60K FPGA實現的MIPI CPHY轉MIPI DPHY透傳模塊

SNx5DPHY440SS:MIPI? CSI - 2/DSI DPHY重定時器的深度解析

SNx5DPHY440SS:MIPI? CSI - 2/DSI DPHY重定時器的深度解析

評論