sparc v8架構的異常處理

1.前言

2.異常簡介

3.異常的使用場合

4.sparc v8異常處理流程

5.總結

1.前言

對于研究芯片處理器架構,是件非常有意思的事情。剛開始的接觸時候也是一頭霧水,不知所云,看著厚厚的架構手冊,不知道從哪里下手。比如《ARMv8-A Architecture reference manual》一共是6666頁純英文文檔,如果沒真正看過,估計一上來就開始打退堂鼓了。后面接觸的芯片的體系架構多了,自然也明白很多東西其實是有一些共性的,雖然架構不同,但是指令集、流水線以及系統運行的模式也能猜測7到8分準確。本文主要介紹一下sparc v8體系架構下的異常處理,同時簡單的對比一下armv8體系架構的異常。

2.異常簡介

Exception,中文翻譯一般是異常,龍芯的手冊上翻譯為例外。就是系統在運行的過程中發生了異常事件,比如除0溢出、數組越界、文件找不到等。這種錯誤一般都是可以預測到的,所以芯片設計的時候,也會預留一些陷阱,當在特定的情況下,進入這個陷阱,說明發生了特定的事情。當然在語言處理層面,也會引入異常的這個概念,也就是比如java中,遇到異常可以throw拋棄也能夠catch捕獲異常。對于芯片架構來說,這種處理過程更加有意思。

在armv8中,會指定一個異常向量表,將這個異常向量表的首地址交給一個寄存器,當異常發生的時候,則會跳轉到相應偏移的處理程序中。

system_vectors: .align11 .setVBAR,system_vectors .orgVBAR //ExceptionfromCurrentEL(EL1)withSP_EL0(SPSEL=1) .org(VBAR+0x00+0) Bvector_error//Synchronous .org(VBAR+0x80+0) Bvector_irq//IRQ/vIRQ .org(VBAR+0x100+0) Bvector_fiq//FIQ/vFIQ .org(VBAR+0x180+0) Bvector_error//Error/vError //ExceptionfromCurrentEL(EL1)withSP_ELn .org(VBAR+0x200+0) Bvector_error//Synchronous .org(VBAR+0x280+0) Bvector_irq//IRQ/vIRQ .org(VBAR+0x300+0) Bvector_fiq//FIQ/vFIQ .org(VBAR+0x380+0) Bvector_error //ExceptionfromlowerEL,aarch64 .org(VBAR+0x400+0) Bvector_error .org(VBAR+0x480+0) Bvector_error .org(VBAR+0x500+0) Bvector_error .org(VBAR+0x580+0) Bvector_error //ExceptionfromlowerEL,aarch32 .org(VBAR+0x600+0) Bvector_error .org(VBAR+0x680+0) Bvector_error .org(VBAR+0x700+0) Bvector_error .org(VBAR+0x780+0) Bvector_error .org(VBAR+0x800+0) Bvector_error

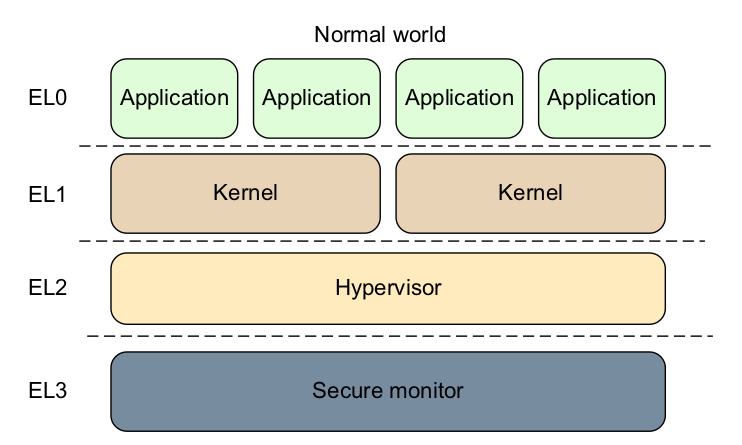

在armv8架構中,處理器所處的模式一共有四種,EL0EL1EL2EL3。同一時刻只能處于一種ELx,所以在每個EL層級,異常的處理都會有Synchronous、IRQ、FIQ、Error四種。這也是armv8的特殊之處。

而對于sparc v8架構而言,處理器的模式只有兩種,supervisor 和 user mode。只需要設置寄存器即可。相比較而言sparc v8的異常更好理解。就是系統在user模式下權限比較低,可以做不破壞系統狀態的事情,比如不能改變系統運行狀態,不能修改寄存器值,不能修改PC指針等等。但是在supervisor下就能夠做這些事情。

所以這時候問題就來了,兩種模式如何切換,這時就需要借助Exception。一般來說,sparc v8的啟動入口就是異常向量的入口,所以第一次進來的就是reset異常。當系統處于異常處理程序的時候,這時候的模式為supervisor,可以做很多事情,比如修改pc指針,修改處理器模式等等。最后退出異常處理,進入用戶模式進行處理。

在sparc中,預留了一些可以配置的軟件中斷,使用ta n來觸發系統進入特定的陷阱,其中n表示軟件中斷標號,這些都是設計者為芯片使用者留下的工具。

3.異常的使用場合

說起異常,很多人都覺得這是一個致命的錯誤,所以避而遠之。其實不然,異常使用得當,將會大大提高系統的運行效率。比如在rtos porting的過程中,我們常常需要改變處理器的運行狀態,或者利用異常進入到特定的處理函數中,例如system call等等。

異常也提供了安全機制,比如在芯片使用上,我們往往不會賦予我們的執行程序在芯片的最高權限下去使用這個芯片。比如armv8,我們不會去el3上運行一個系統,這樣一不小心就會出現不可逆轉的錯誤。一般的rtos或者linux都會選擇el1作為系統運行的層級。需要在el3上做的事情比較少,這時候就可以通過異常轉換層級,達到我們的目的。在sparc v8上也是這樣,一般程序運行在user mode,只有需要的時候,才會切換到supervisor mode。

另外就是系統進入中斷的時候,本質上來說,中斷其實就是異常的一種,因為異常分為同步和異步,其中異步異常就是中斷。在中斷里做的事情一般都是比較緊急的事情。

當系統進入trap的時候,就是出現了同步異常的時候,這時候需要告知使用者,當前出現了除零錯誤地址訪問異常等等。這些都是trap必須設置的,如果芯片沒有這些保護機制,任程序繼續執行下去,那將會造成不可預知的后果。

4.sparc v8異常處理流程

在sparc異常的處理中,默認情況下會在程序執行的入口處設定異常向量表。然后首先通過一個reset的異常進入第一行啟動代碼。系統運行起來后,會初始化狀態寄存器,初始化C語言執行需要的環境,比如清除bss段、設置sp棧指針等等。

然后程序進入C語言執行,其中匯編語言中的ret1會主動將pc值填充,然后跳轉。系統運行時,若遇到中斷需要處理,則進入中斷處理程序。如果系統在user mode下運行,需要修改pc值,那么只能通過trap指令進行,其中sparc v8的ta指令就是進入同步異常,然后去處理supervisor模式才能做的事情。

對于一個rtos來說,線程壓棧的時候,會把當前的pc、和一些狀態寄存器、通用寄存器的值讀出來,保存在當前的線程棧中,也就是一塊內存中,接著會將另外的一個線程棧的內容從內存中取出來,然后設置pc值、狀態寄存器值、以及通用寄存器值等等,這時在sparc v8上就需要執行ta 3指令了,其中ta n中的n是自己設定的,需要自己實現相關的處理函數,這里只是預留了一個陷阱,至于陷阱怎么處理,那是需要自己來設定的。

5.總結

本文主要介紹了一下異常這部分的處理邏輯,只有在研究芯片體系架構的時候,才會需要非常深刻的了解這一塊。使用好異常,將會讓程序設計變得更加的合理,也能夠非常清晰的了解操作系統的底層運行邏輯。

原文標題:sparc v8架構的異常處理

-

SPARC

+關注

關注

0文章

16瀏覽量

10169

原文標題:sparc v8架構的異常處理

文章出處:【微信號:Embeded_IoT,微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用PLCSIM Advanced V8仿真測試S7-1200 G2的Modbus TCP通信

深入剖析ARM64異常處理:開發者必須掌握的底層核心邏輯

元服務上架自檢

基于蜂鳥E203架構的指令集K擴展

迅為Hi3403V610開發板海思Cortex-A55架構核心板卡

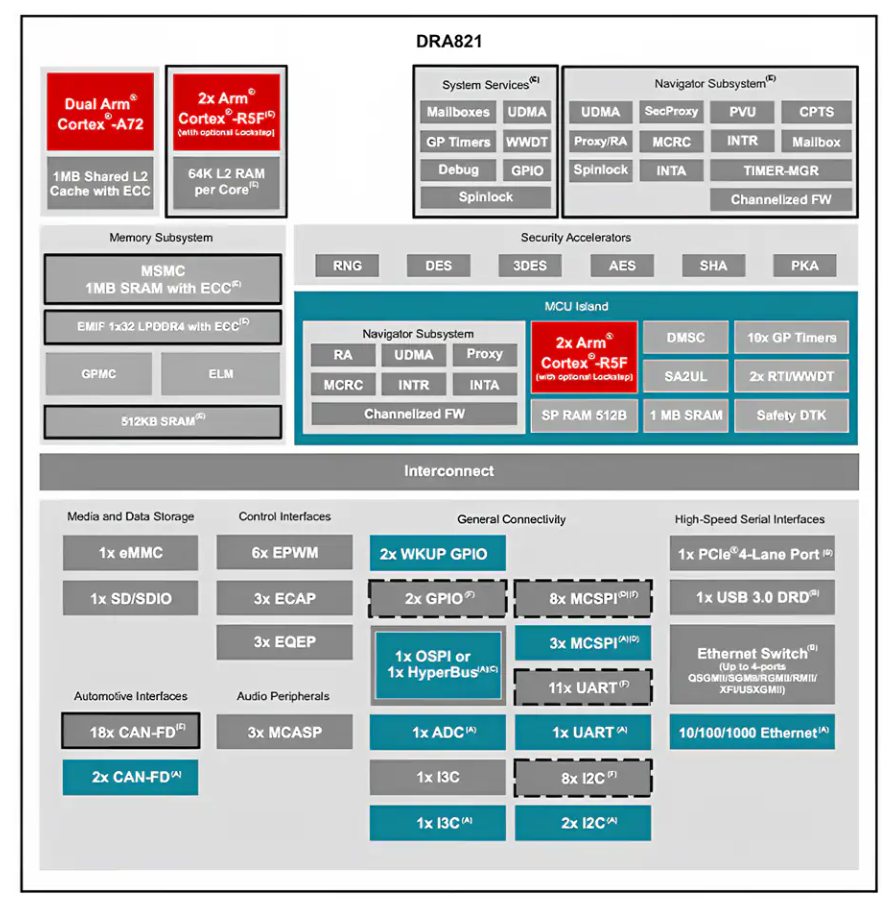

Texas Instruments DRA821x Jacinto? 64位處理器技術解析

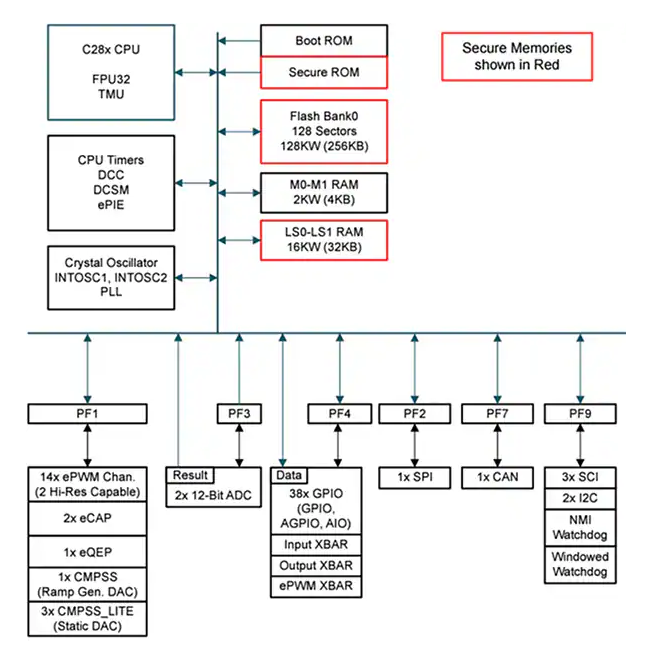

德州儀器AM68x Jacinto 8處理器技術解析

sparc v8架構的異常處理

sparc v8架構的異常處理

評論