Texas Instruments DRA821x Jacinto? 64位處理器基于ARM?v8架構,并為帶有云連接性的網關系統進行了優化。片上系統 (SoC) 設計通過集成降低了系統級成本和復雜性—尤其是系統MCU、功能安全和安保功能以及用于高速通信的以太網交換機。集成的診斷和功能安全特性是針對ASIL-D和SIL 3認證要求而設計的。PCIe控制器和支持TSN的千兆位以太網交換機可實現實時控制和低延遲通信。

數據手冊:*附件:Texas Instruments DRA821x Jacinto? 64位處理器數據手冊.pdf

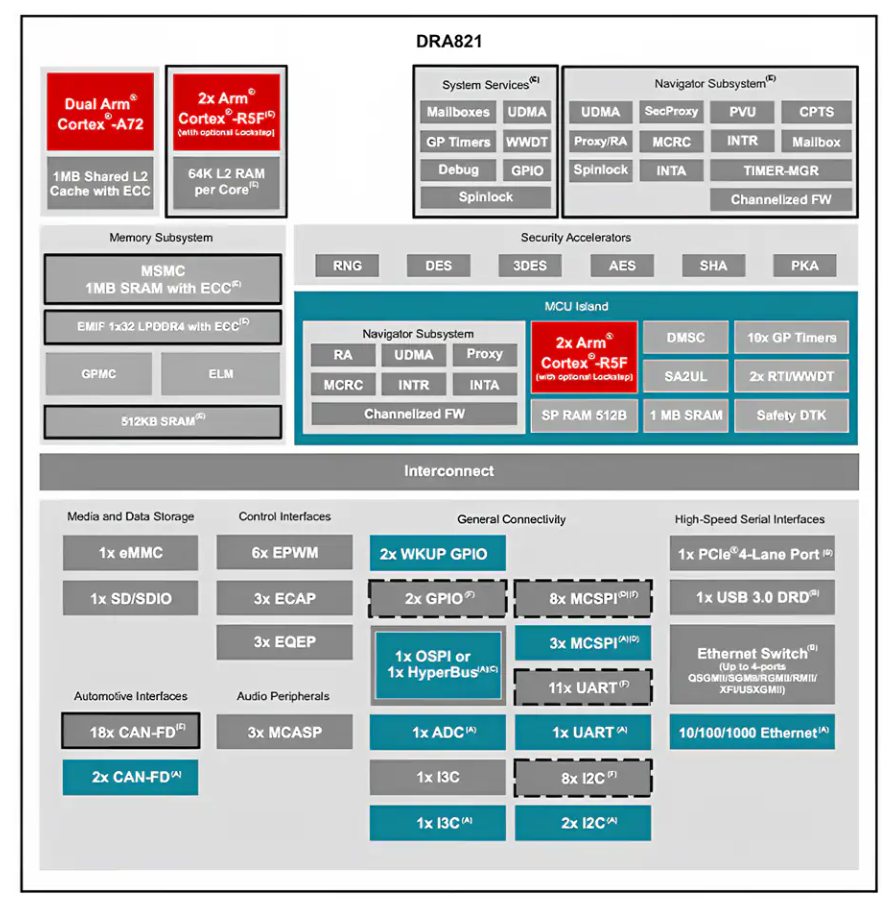

多達四個通用ARM^?^ Cortex?-R5F子系統,可以處理低級、時序關鍵型處理任務,從而使 ARM Cortex-A72內核不受高級和基于云的應用程序的阻礙。Jacinto DRA821x 處理器包括擴展MCU (eMCU) 域概念。該域是主域上處理器和外設的子集,旨在實現更高的功能安全性,例如ASIL-D/SIL-3。功能框圖突出顯示了eMCU中包含哪些IP。

特性

- 處理器內核:

- 雙64 位ARM Cortex-A72微處理器子系統,最高可達2.0GHz、 24K DMIPS

- 每個雙核Cortex-A72集群1MB L2共享緩存

- 每個A72內核具有32KB L1數據緩存和48KB L1指令緩存

- 4個ARM Cortex-R5F MCU,運行頻率高達1.0GHz,可選擇鎖步操作,整數運算能力為8K DMIPS

- 32K指令緩存、32K數據緩存、64K L2 TCM

- 兩個Arm Cortex-R5F MCU,隔離式MCU子系統中

- 通用計算分區中的2個ARM Cortex-R5F MCU

- 雙64 位ARM Cortex-A72微處理器子系統,最高可達2.0GHz、 24K DMIPS

- 內存子系統:

- 虛擬化

- ARM Cortex-A72中的Hypervisor支持

- 采用Arm Cortex-A72、Arm Cortex-R5F(具有隔離式安全MCU島)的獨立處理子系統

- IO虛擬化支持

- 外設虛擬化單元 (PVU),用于低延遲高帶寬外設流量

- 支持多區域防火墻,用于內存和外設隔離

- 以太網、PCIe和DMA虛擬化支持

- 設備安全(在部分零件編號上)

- 功能安全:

- 針對符合功能安全標準(針對部分零件編號):

- 開發用于功能安全應用

- 可提供文檔,協助ISO 26262和IEC 61508功能安全系統設計(高達ASIL-D/SIL-3)

- 針對系統能力高達ASIL-D/SIL-3

- 為MCU域針對的硬件完整性高達ASIL-D/SIL-3

- 硬件完整性高達ASIL-D/SIL-3,用于主域的擴展MCU (EMCU) 部分

- 為主域的剩余部分針對的硬件完整性高達ASIL-B/SIL-2

- EMCU和主域其余部分之間提供FFI隔離

- 安全相關認證

- 符合ISO 26262和IEC 61508標準(已計劃)

- 以Q1結尾的零件系列已符合AEC-Q100認證

- 針對符合功能安全標準(針對部分零件編號):

- 高速接口:

- 一個PCI-Express Gen3控制器:

- 支持Gen1、 Gen2和 Gen3的操作,并具有自動協商功能

- 4個通道

- 一個USB 3.1 Gen1雙重角色設備子系統:

- 支持Type-C切換

- 可獨立配置為USB主機、USB外設或USB雙角色器件

- 汽車接口

- 音頻接口:

- 3個多通道音頻串行端口 (MCASP) 模塊

- 閃存接口:

- 嵌入式多媒體卡 (eMMC? 5.1) 接口

- 支持高達HS400速度

- 嵌入式多媒體卡 (eMMC? 5.1) 接口

- 一個安全數字3.0/安全數字輸入輸出3.0 (SD3.0/SDIO3.0) 接口

- 1個八通道SPI/Xccela?/HyperBus 內存控制器 (HBMC) 接口

- 16nm FinFET技術

- 17.2mm x 17.2mm、0.8mm腳距、IPC 3類PCB

功能框圖

Texas Instruments DRA821x Jacinto? 64位處理器技術解析

一、處理器概述

Texas Instruments的DRA821x Jacinto?處理器是基于Armv8 64位架構的汽車級處理器,專為需要云連接的網關系統優化設計。該SoC通過高度集成降低了系統級成本和復雜度,特別適合汽車網關、車身控制模塊、V2X/V2V等應用場景。

二、關鍵特性

1. 處理器核心配置

- ?雙核Cortex-A72?:主頻最高2.0GHz,提供24K DMIPS性能

- ?四核Cortex-R5F?:主頻最高1.0GHz,支持鎖步模式

- ?內存子系統?:

- 1MB L3 RAM帶ECC和一致性支持

- LPDDR4內存接口,支持3200 MT/s速率

- 512KB片上SRAM(MAIN域)

2. 安全與功能安全

- 支持硬件虛擬化(Hypervisor)

- 獨立安全MCU島設計

- 功能安全目標達ASIL-D/SIL-3認證要求

- 安全啟動與運行時支持,支持客戶可編程根密鑰

3. 高速接口

- 集成以太網TSN/AVB交換機(支持4/2個外部端口)

- PCIe Gen3控制器(4通道)

- USB 3.1 Gen1雙角色設備子系統

- 20個CAN-FD接口

三、應用領域

DRA821x系列處理器特別適合以下應用場景:

四、封裝與功耗

- 采用16nm FinFET工藝

- 17.2mm x 17.2mm FCBGA封裝,0.8mm間距

- 支持多級電壓域管理,包括:

- 核心電壓:0.76-0.84V

- DDR接口電壓:1.05-1.15V

- I/O電壓:1.71-3.46V(根據接口類型)

-

處理器

+關注

關注

68文章

20298瀏覽量

253641 -

mcu

+關注

關注

147文章

19021瀏覽量

400900 -

ARM

+關注

關注

135文章

9573瀏覽量

392913 -

片上系統

+關注

關注

0文章

203瀏覽量

27714

發布評論請先 登錄

新戰局,解析64位處理器以及未來發展趨勢

32位嵌入式處理器與8位處理器應用開發的區別

詳細解析32位嵌入式處理器與8位處理器應用開發的不同之處

32位處理器的開發與8位處理器的開發有哪些明顯的不同?

Mobile Athlon 64位處理器詳解

Intel 32位處理器 ,Intel 32位處理器結構原理

Intel 64位處理器,Intel 64位處理器結構原理

AMD 32位處理器,AMD 32位處理器有哪些系列?

到底64位處理器和32位處理器有什么區別呢?資料下載

Texas Instruments DRA821x Jacinto? 64位處理器技術解析

Texas Instruments DRA821x Jacinto? 64位處理器技術解析

評論