RISC-V 作為開源、模塊化的精簡指令集架構,其異常中斷機制是保障系統可靠運行、響應外部事件與處理內部錯誤的核心支撐。不同于 x86、ARM 等閉源架構的復雜設計,RISC-V 異常中斷機制遵循“精簡、靈活、可擴展”的設計理念,通過模塊化特權級、標準化控制寄存器與可配置的處理流程,適配從嵌入式微控制器到高性能服務器的全場景需求。本文將從核心概念、分類體系、處理流程、關鍵寄存器及實際應用等維度,對 RISC-V 異常中斷機制進行全面解析。

一、核心概念:異常與中斷的定義及本質區別

在 RISC-V 架構中,“異常(Exception)”與“中斷(Interrupt)”均屬于“異常事件”的范疇,本質是打破處理器正常指令執行流的特殊事件,但二者的觸發源、觸發時機與處理目標存在明確差異,這是理解 RISC-V 異常中斷機制的基礎。

1.1 異常(Exception)

異常是由處理器內部執行過程觸發的事件,通常與當前執行的指令直接相關,屬于“同步事件”(與指令執行時鐘同步)。其核心特征是“執行錯誤或特殊需求”,需要處理器暫停當前任務,轉入異常處理程序修正錯誤或完成特殊操作后,再返回原執行流(或終止執行)。

常見異常類型包括:非法指令異常(執行未定義指令)、訪存錯誤異常(訪問未授權內存、對齊錯誤)、斷點異常(執行 EBREAK 指令,用于調試)、系統調用異常(執行 ECALL 指令,用戶態向特權態切換)、頁故障異常(虛擬內存地址未映射)等。

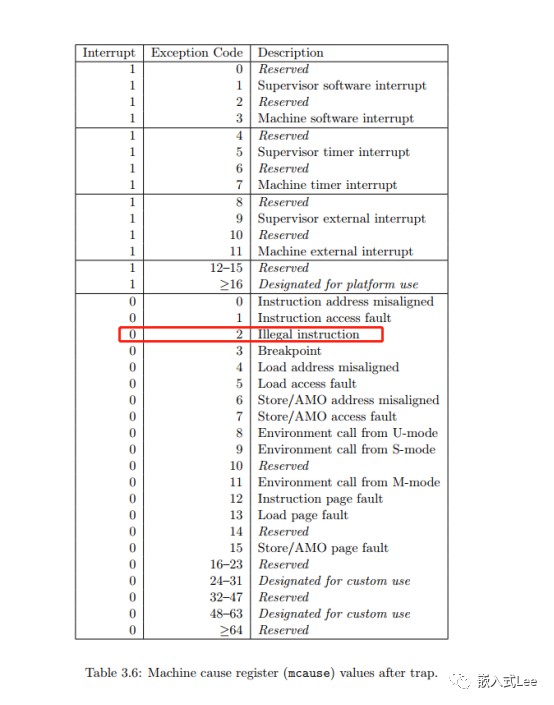

二、RISC-V 異常中斷的分類體系

RISC-V 對異常中斷的分類采用“原因碼(Cause Code)”標準化定義,通過核心控制寄存器 mcause(機器模式原因寄存器)、scause(監督模式原因寄存器)等存儲事件類型,不同特權級對應獨立的原因碼空間。分類體系可從“特權級維度”和“事件類型維度”雙重劃分。

2.1 特權級維度分類

RISC-V 支持 4 種特權級(從高到低:M 模式、S 模式、H 模式、U 模式),其中 H 模式(Hypervisor 虛擬化模式)為擴展特權級,嵌入式場景常用 M 模式(機器模式)和 S 模式(監督模式)。異常中斷的處理特權級由事件類型和系統配置決定:

- M 模式專屬事件 :涉及處理器核心硬件的關鍵事件,如復位異常、硬件錯誤異常、M 模式定時器中斷等,只能在 M 模式下處理(最高特權級,不可剝奪)。

- S 模式專屬事件 :涉及操作系統層面的事件,如虛擬內存頁故障、S 模式系統調用、外設中斷(由 M 模式委托給 S 模式)等,由操作系統內核處理。

- U 模式觸發事件 :用戶態程序觸發的事件(如 U 模式系統調用、非法指令),需陷入更高特權級(S 或 M 模式)處理。

核心規則:低特權級事件可通過“委托機制”(Delegation)交由高特權級處理,高特權級事件不可委托給低特權級。

2.2 事件類型維度分類(標準原因碼)

RISC-V 標準定義了 32 位原因碼(部分位為擴展預留),其中最高位(第 31 位)用于區分“中斷”與“異常”: 最高位為 1 表示中斷,為 0 表示異常 ;低 31 位為具體事件的原因碼編號。以下是常用標準原因碼:

| 原因碼(低31位) | 事件類型(最高位=0:異常;=1:中斷) | 說明 |

|---|---|---|

| 0 | 異常:指令地址對齊錯誤 | 訪問指令地址非指令長度對齊(如32位指令地址未對齊 4 字節) |

| 2 | 異常:非法指令 | 執行未定義的RISC-V指令 |

| 3 | 異常:斷點 | 執行EBREAK調試指令觸發 |

| 8 | 異常:環境調用(ECALL)- U 模式 | 用戶態程序執行ECALL觸發系統調用 |

| 9 | 異常:環境調用(ECALL)- S 模式 | 監督態程序執行ECALL觸發更高特權級調用 |

| 11 | 異常:環境調用(ECALL)- M 模式 | 機器態程序執行ECALL觸發(通常保留) |

| 12 | 異常:頁故障(指令訪問) | 虛擬指令地址未映射或權限不足 |

| 13 | 異常:頁故障(數據寫訪問) | 虛擬數據地址寫訪問未映射或權限不足 |

| 14 | 異常:頁故障(數據讀訪問) | 虛擬數據地址讀訪問未映射或權限不足 |

| 16 | 中斷:外部中斷(M模式) | 外部設備觸發的機器態中斷 |

| 17 | 中斷:軟件中斷(M模式) | 軟件觸發的機器態中斷(如多核心通信) |

| 18 | 中斷:定時器中斷(M模式) | 機器態定時器(mtime)溢出觸發 |

| 20 | 中斷:外部中斷(S模式) | 外部設備觸發的監督態中斷(由M模式委托) |

三、RISC-V 異常中斷的核心處理流程

RISC-V 異常中斷處理流程遵循“標準化、可配置”的設計思路,核心流程分為 5 個階段: 事件觸發與識別 → 上下文保存 → 異常入口跳轉 → 事件處理 → 上下文恢復與返回 。不同特權級的處理流程基本一致,差異主要體現在控制寄存器的使用和權限檢查上。以下以最常用的 M 模式(機器模式)為例,詳細拆解處理流程。

3.1 階段 1:事件觸發與識別

當異常(如非法指令)或中斷(如定時器溢出)發生時,處理器首先完成當前指令的執行(異常為同步觸發,中斷為異步觸發,需等待當前指令執行完畢),隨后進行事件識別:

- 處理器自動檢測事件類型,將“中斷/異常標識”(最高位)和“原因碼”寫入mcause 寄存器;

- 記錄當前指令的下一條指令地址(異常時為出錯指令地址,中斷時為當前執行完畢指令的下一條地址)到 mepc(機器模式異常程序計數器)寄存器,用于后續返回;

- 檢查事件對應的特權級和使能狀態:通過 mie(機器模式中斷使能寄存器)檢查中斷是否被使能,通過 mstatus(機器模式狀態寄存器)的 MIE 位(全局中斷使能)檢查全局中斷開關,若未使能則忽略該事件。

3.2 階段 2:上下文保存

為了在事件處理完成后能夠恢復原任務的執行狀態,處理器需要保存當前的“上下文”(即處理器核心寄存器狀態)。RISC-V 架構 未規定硬件自動保存上下文 ,而是將上下文保存交由軟件實現(靈活性更高,適配不同場景的資源需求):

- 保存的核心上下文包括:通用寄存器(x0~x31,x0 恒為 0 可省略)、程序計數器(PC,已由硬件保存到 mepc)、狀態寄存器(mstatus)等;

- 保存位置:通常為當前特權級的棧空間(如 M 模式棧),或專用的上下文保存緩沖區(嵌入式場景常用,減少棧操作開銷);

- 注意事項:上下文保存需保證“原子性”,避免在保存過程中被更高優先級事件打斷(可通過關閉全局中斷實現,即清除 mstatus.MIE 位)。

3.3 階段 3:異常入口跳轉

上下文保存完成后,處理器需要跳轉到對應的異常處理程序入口。RISC-V 通過 mtvec(機器模式異常向量表基地址寄存器)配置入口地址和跳轉模式,支持兩種跳轉模式:

- 直接模式(Direct Mode) :mtvec 寄存器低 2 位為 00,所有異常中斷都跳轉到 mtvec 高 30 位指定的基地址。該模式適用于簡單系統(如嵌入式微控制器),處理流程統一,實現簡單,但靈活性低;

- 向量模式(Vectored Mode) :mtvec 寄存器低 2 位為 01,不同類型的異常中斷跳轉到不同的入口地址。入口地址計算規則為:mtvec 基地址 + 4 × 原因碼。該模式適用于復雜系統(如操作系統),可針對不同事件快速跳轉到專用處理函數,提升處理效率。

跳轉完成后,處理器自動將當前特權級切換到 M 模式(若當前為低特權級),并關閉全局中斷(mstatus.MIE 清 0),避免處理過程中被打斷。

3.4 階段 4:事件處理(核心業務邏輯)

跳轉至異常處理程序后,軟件根據 mcause 寄存器的原因碼,執行對應的處理邏輯。不同事件的處理邏輯差異較大,典型場景如下:

- 非法指令異常 :打印錯誤日志,終止當前任務或復位系統;

- 系統調用異常 :根據系統調用號(通常存儲在 a7 寄存器),執行對應的內核服務(如文件讀寫、進程調度);

- 定時器中斷 :更新系統時鐘,觸發任務調度(RTOS 核心邏輯);

- 外設中斷 :讀取外設狀態寄存器,處理數據(如 UART 接收數據存入緩沖區),清除中斷標志位。

處理過程中需注意:若存在中斷嵌套需求,可在處理低優先級事件時,重新開啟全局中斷(設置 mstatus.MIE 為 1),允許更高優先級中斷打斷當前處理。

3.5 階段 5:上下文恢復與返回

事件處理完成后,需要恢復之前保存的上下文,并返回原任務繼續執行:

- 從棧或緩沖區中恢復通用寄存器、mstatus 等上下文信息;

- 執行 mret 指令(機器模式返回指令):處理器自動將mepc 寄存器中的地址加載到 PC,跳回原任務的下一條指令;同時恢復之前的全局中斷使能狀態(mstatus.MPIE 位的值傳遞給 mstatus.MIE)。

至此,整個異常中斷處理流程完成,處理器恢復原任務的正常執行流。

四、關鍵控制寄存器解析

RISC-V 異常中斷機制的核心是一系列特權級控制寄存器,用于配置使能、記錄事件信息、存儲上下文地址等。以下是 M 模式和 S 模式下最關鍵的寄存器,以及其核心功能:

4.1 狀態寄存器:mstatus / sstatus

用于記錄和控制處理器的特權級狀態、中斷使能狀態等,核心位定義如下(以 mstatus 為例):

- MIE(位 3):機器模式全局中斷使能位,1=使能,0=禁用;

- MPIE(位 7):機器模式中斷使能保存位,用于在異常發生時保存 MIE 的值,恢復時通過 mret 指令恢復;

- MPP(位 11~12):機器模式之前特權級,記錄異常發生前的特權級(00=U 模式,01=S 模式,11=M 模式),用于返回時恢復特權級;

- SIE(位 1)、SPIE(位 5)、SPP(位 8~9):對應 S 模式的中斷使能位、保存位、之前特權級,功能與 M 模式類似。

4.2異常入口寄存器:mtvec / stvec

用于配置異常中斷的入口地址和跳轉模式,格式為:

- 低 2 位:跳轉模式(00=直接模式,01=向量模式,10/11=預留);

- 高 30 位:異常向量表基地址。

4.3 原因與程序計數器寄存器:mcause / scause、mepc / sepc

- mcause / scause:存儲異常中斷的原因碼,最高位區分中斷(1)與異常(0),低 31 位為具體原因碼;

- mepc / sepc:存儲異常中斷發生時的下一條指令地址,用于返回原執行流。

4.4 讀取方式:

例:

五、實際應用場景與注意事項

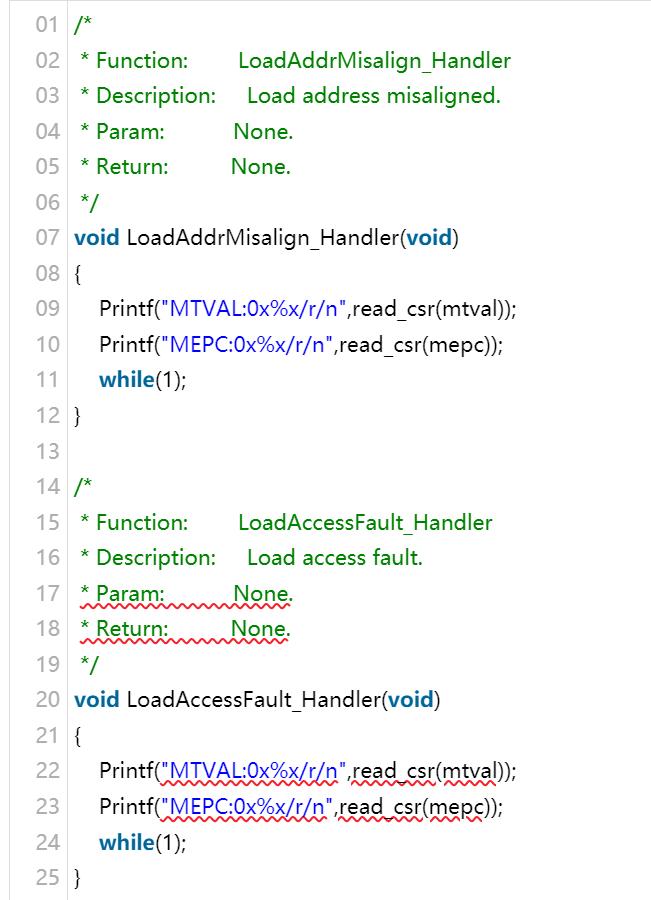

**5.1 **程序中全局數組地址為奇數地址,未四字節對齊

打印內容:

"MTVAL:0xeeeeeeee/r/n MEPC :0xeeeeeeee/r/n"

修改方式:

typedef** attribute ((aligned(4))) uint16_t AlignedUint16_IAR;**

void****MapADCTempResultsToArray( AlignedUint16_IAR Set_74HC4067_Channel[TEMP_SENSOR_COUNT])

**5.2 **內存訪問異常場景

// 數組越界觸發硬件異常的測試函數

voidtest_array_out_of_bounds(void) {

int****arr[3] = {1, 2, 3};

// 合法訪問:索引2

printf("合法訪問arr[2]:%dn", arr[2]);

// 越界訪問:

int****arr[3] = val; // 讀越界,觸發加載訪問故障

(void)val;

}

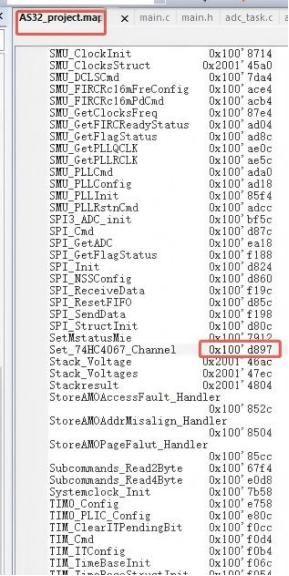

打印內容

"MTVAL:0x10084dc/r/n MEPC :0x100f46/r/n"

MTVAL顯示 “LoadAccessFault_Handler”對應的地址;MEPC: 0x100f46 顯示出錯的非對齊地址

六、總結

RISC-V 異常中斷機制以“精簡、靈活、可擴展”為核心設計理念,通過標準化的原因碼、可配置的處理流程和特權級隔離,實現了對各類異常和中斷事件的高效管理。其核心優勢在于:模塊化的特權級設計適配全場景需求,軟件可控的上下文保存提升靈活性,標準化的控制寄存器降低開發復雜度。

理解 RISC-V 異常中斷機制的關鍵在于厘清“異常與中斷的本質區別”、掌握“標準化處理流程”和“核心控制寄存器的功能”,并結合具體應用場景(嵌入式/操作系統)優化配置。隨著 RISC-V 架構的不斷普及,深入掌握其異常中斷機制將成為嵌入式開發、處理器架構設計等領域的核心能力。

-

嵌入式

+關注

關注

5203文章

20549瀏覽量

335756 -

RISC-V

+關注

關注

49文章

2924瀏覽量

53301 -

異常中斷

+關注

關注

0文章

10瀏覽量

1403

發布評論請先 登錄

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

RISC-V的異常處理機制復雜嗎?

ARM微處理器編程模型之異常中斷處理分析

Thumb指令集之異常中斷產生指令解析

ARM S3C4510B系統的異常中斷機制解析

RISC-V異常中斷機制全解析

RISC-V異常中斷機制全解析

評論