連接器

電子發燒友網連接器技術專欄,內容有連接器、光纖連接器、工業連接器、汽車連接器、電線電纜、接插件以及連接器技術的其它應用方案等;是電子工程師學習連接器技術的好欄目。FIFO的電路設計與仿真驗證

在計算機中,先入先出隊列是一種傳統的按序執行方法,先進入的指令先完成并引退,跟著才執行第二條指令(指令就是計算機在響應用戶操作的程序代碼,對用戶而言是透明的)。...

FPGA之流水線練習4:實現4輸入的乘法運算

流水線是人和機器的有效組合,最充分體現設備的靈活性,它將輸送系統、隨行夾具和在線專機、檢測設備有機的組合,以滿足多品種產品的輸送要求。輸送線的傳輸方式有同步傳輸的/(強制...

實現包文對比模塊的設計練習

FIFO是隊列機制中最簡單的,每個接口上都存在FIFO隊列,表面上看FIFO隊列并沒有提供什么QoS(Quality of Service,服務質量)保證,甚至很多人認為FIFO嚴格意義上不算做一種隊列技術,實則不然,...

FPGA之流水線練習5:實現4輸入的乘法運算

流水線工作方式可節約工廠生產成本,可一定程度上節約生產工人數量,實現一定程度的自動化生產,前期投入不大,回報 率高。...

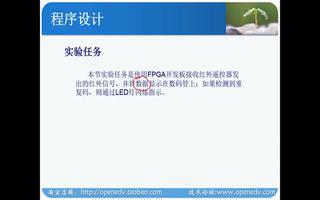

CPU與FPGA通過異步接口信號實現通信

FPGA 的基本結構包括可編程輸入輸出單元,可配置邏輯塊,數字時鐘管理模塊,嵌入式塊RAM,布線資源,內嵌專用硬核,底層內嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,...

FPGA之FIFO的原理概述

FIFO隊列不對報文進行分類,當報文進入接口的速度大于接口能發送的速度時,FIFO按報文到達接口的先后順序讓報文進入隊列,同時,FIFO在隊列的出口讓報文按進隊的順序出隊,先進的報文將先...

FPGA之流水線練習(2):設計思路

流水線安裝時工作地的排列要符合工藝路線,當工序具有兩個以上工作地時,要考慮同一工序工作地的排列方法。一般當有兩個或兩個以上偶數個同類工作地時,要考慮采用雙列布置,將它們分...

FPGA之流水線練習5:設計思路

流水線的工作方式就象工業生產上的裝配流水線。在CPU中由5—6個不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5—6步后再由這些電路單元分別執行,這樣就能實現在一...

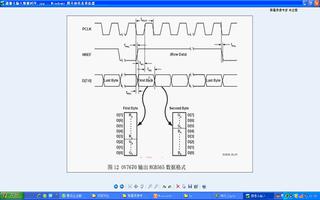

FPGA之異步練習2:接口時序參數

異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起。...

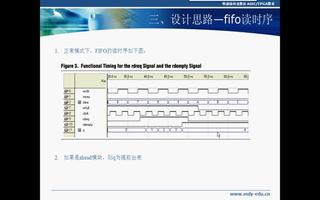

FPGA之FIFO練習3:設計思路

根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。...

FPGA之FIFO練習

FIFO隊列具有處理簡單,開銷小的優點。但FIFO不區分報文類型,采用盡力而為的轉發模式,使對時間敏感的實時應用(如VoIP)的延遲得不到保證,關鍵業務的帶寬也不能得到保證。...

FPGA之FIFO練習1:設計思路

FIFO隊列具有處理簡單,開銷小的優點。但FIFO不區分報文類型,采用盡力而為的轉發模式,使對時間敏感的實時應用(如VoIP)的延遲得不到保證,關鍵業務的帶寬也不能得到保證。...

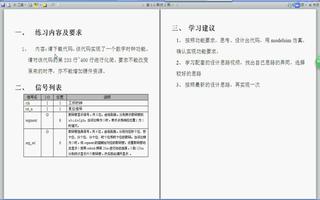

用代碼實現數字時鐘功能及進行modelsim仿真

ModelSim是業界最優秀的HDL語言仿真軟件,它能提供友好的仿真環境,是業界唯一的單內核支持VHDL和Verilog混合仿真的仿真器。它采用直接優化的編譯技術、Tcl/Tk技術、和單一內核仿真技術,編譯...

FPGA之異步練習2:設計思路

異步雙方不需要共同的時鐘,也就是接收方不知道發送方什么時候發送,所以在發送的信息中就要有提示接收方開始接收的信息,如開始位,同時在結束時有停止位。...

FPGA之軟核演練篇:緊耦合指令或數據存儲端口

緊耦合就是模塊或者系統之間關系太緊密,存在相互調用。緊耦合系統的缺點在于更新一個模塊的結果導致其它模塊的結果變化,難以重用特定的關聯模塊。...

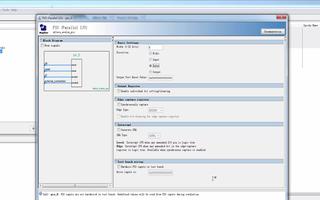

FPGA之軟核演練篇:Nios II用戶程序上電自啟動

Nios Ⅱ處理器具有完善的軟件開發套件,包括編譯器、集成開發環境(IDE)、JTAG調試器、實時操作系統(RTOS)和TCP/IP協議棧。設計者能夠用Altera Quartus Ⅱ開發軟件中的SOPC Builder系統開發工具很...

FPGA之軟核演練篇:PIO內核配置選項

PIO即可自由組裝成一體電腦的新型準電腦,它把顯示器、機箱、電源、光驅和鍵鼠融為一體,需自由購買CPU 、主板、硬盤、內存等組裝成一體電腦的硬件系統開放平臺。...

FPGA之軟核演練篇:影子寄存器組

ARM核是一個非常緊湊的設計,影子寄存器的引入就是這種設計的表現。通過引入影子寄存器,指令可以重復使用相同的寄存器編碼,但是在不同模式下,這些編碼對應不同的物理寄存器。比如...

FPGA之軟核演練篇:Nios II程序

Nios Ⅱ處理器支持 Nios Ⅱ處理器支持頁面提供了對Nios Ⅱ 設計者有幫助的多種信息,其中包括使用許可、下載、參考設計、文檔資料、在線展示及常見問題。...

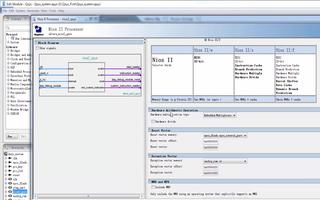

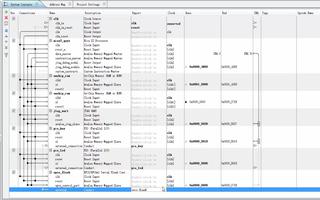

FPGA之軟核演練篇:構建Qsys系統的硬件部分

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置IP,以及Avalon總線接口規范,...

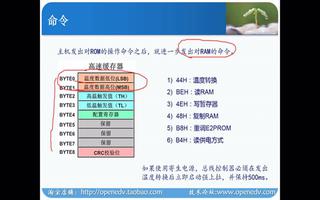

FPGA之軟核演練篇:內置IP核之EPCS的理論實戰講解

EPCS是串行存儲器,NiosII 不能直接從EPCS中執行程序,它實際上是執行EPCS控制器的片內ROM中的代碼(即Bootloader),把EPCS中的程序搬到RAM中執行。...

FPGA之軟核演練篇:PIO應用實例

PIO即可自由組裝成一體電腦的新型準電腦,它把顯示器、機箱、電源、光驅和鍵鼠融為一體,需自由購買CPU 、主板、硬盤、內存等組裝成一體電腦的硬件系統開放平臺。...

FPGA之軟核演練篇:如何在Qsys系統中內置IP

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置IP,以及Avalon總線接口規范,...

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |