連接器

電子發燒友網連接器技術專欄,內容有連接器、光纖連接器、工業連接器、汽車連接器、電線電纜、接插件以及連接器技術的其它應用方案等;是電子工程師學習連接器技術的好欄目。時序約束:不需要檢查的路徑

時序表示動態規模或過程的時間演化。它們用于識別、建模和預測在離散時間間隔內采樣的數據中的模式和行為。考慮使用時間表而不是 timeseries 對象,以便將時間戳數據存儲為列向數據變量。...

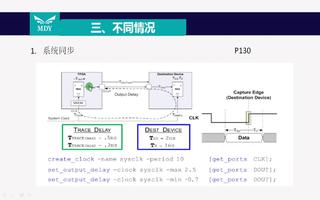

時序約束步驟:系統同步與源同步

針對普通時鐘系統存在著限制時鐘頻率的弊端,人們設計了一種新的時序系統,稱之為源同步時序系統。它最大的優點就是大大提升了總線的速度,在理論上信號的傳送可以不受傳輸延遲的影響...

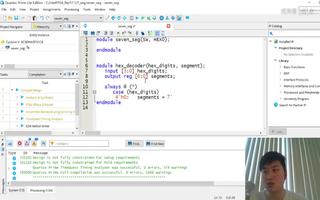

FPGA Verilog實現4位數碼管動態顯示

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。...

FPGA的組成結構和優缺點講解

這期視頻Dave Jones講解了FPGA的大致組成結構,列舉了它的優點和缺點,最后給初學者提了一些簡單的建議。...

FPGA簡單入門和邏輯塊與相對于處理器的并行操作

4分鐘的FPGA簡單入門介紹,主要介紹了邏輯塊、相對于處理器的并行操作。搬運于YouTube,字幕自制。...

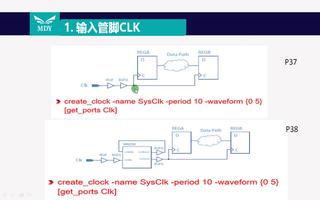

時序約束步驟:生成時鐘約束

差分時鐘是將數據從源傳送到目的地有兩種常用的電氣方法。一種方法使用“單端”發信號概念,它在發射機和接收機之間使用兩個導體。...

基于FPGA的軟核處理器設計實現

本課程從數字IC設計工程師應具備的基本技能講起。首先介紹數字芯片設計流程,主流EDA工具的使用,包括Design Compiler、Prime Time、Formality、VCS+verdi等。并介紹Verilog基本語法,使用verilog編寫簡單...

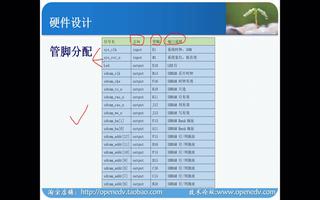

基于STEP-MXO2-C核心板設計機器人競賽通用軟硬件平臺

本設計采用STEP-MXO2-C核心板為控制板,設計了一款適用于各類機器人比賽的通用軟硬件平臺,30路的舵機脈沖輸出,可用于雙足機器人的舵機控制板;10路以上的電機脈沖輸出,可用于智能車和四...

FPGA產生任意頻率正弦波,AM、FM、ASK、PSK

正弦信號發生器(Sinusoidal signal generator)是在電子電路設計、自動控制系統和儀表測量校正調試中應用很多的一種信號發生裝置和信號源,屬于數字信號發生器。而正弦信號是一種頻率成分最為...

利用VHDL語言的FPGA試驗箱設計洗衣機模擬程序

本設計利用vhdl硬件描述語言在FPGA試驗箱設計洗衣機模擬程序。◆利用3個LED表示待機、正轉、反轉三種工作狀態。◆自行設定洗衣機循環次數(最大為16次)。◆具有緊急情況處理功能,發生緊急情...

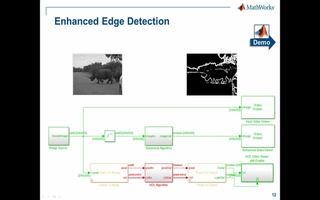

如何在MATLAB中開發基于像素的視頻和圖像處理算法

此講座將結合新產品的特性,重點介紹如何在MATLAB?中開發基于像素流的視頻和圖像處理的算法,并通過HDL代碼產生的技術快速在FPGA上實現。你將了解到:如何在MATLAB中開發基于像素的視頻和圖...

時序約束的四大步驟的具體介紹

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在...

至簡設計法:運算符(2)

使用至簡設計法,即可省略掉常規設計中的繁復思考過程。比如計數器的設計,只需要填入設置條件“什么情況下加一”和“數多少下”。...

如何采用FPGA技術實現深度卷積網絡(2)

卷積神經網絡是一類包含卷積計算且具有深度結構的前饋神經網絡,是深度學習的代表算法之一 。卷積神經網絡具有表征學習能力,能夠按其階層結構對輸入信息進行平移不變分類,因此也被...

至簡設計法:運算符(3)

明德揚至簡設計法,提取大量的實際項目,采用科學的手段統計分析,找出其內在通用性部分,并建立相關的體系,實現了“填空式”設計!首先,把復雜的代碼劃分成幾種類型的模塊,然后以...

FPGA之為什么要進行流水線的設計

流水線又稱為裝配線,一種工業上的生產方式,指每一個生產單位只專注處理某一個片段的工作。以提高工作效率及產量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速...

FPGA時序:用quartus分析時序

Altera Quartus II 作為一種可編程邏輯的設計環境, 由于其強大的設計能力和直觀易用的接口,越來越受到數字系統設計者的歡迎。當前官方提供下載的最新版本是v17.0。...

FPGA之流水線練習(3):設計思路

流水線的平面設計應當保證零件的運輸路線最短,生產工人操作方便,輔助服務部門工作便利,最有效地利用生產面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置...

如何實現一個四輸入乘法器的設計

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。...

基于ZYNQ FPGA與PC的IP設計與驗證方案(3)

Zynq-7000系列的可編程邏輯完全基于賽靈思最新7系列FPGA架構來設計,可確保28nm系列器件的IP核、工具和性能100%兼容。...

程序設計:設計不同的語法

C語言是僅產生少量的機器語言以及不需要任何運行環境支持便能運行的高效率程序設計語言。盡管C語言提供了許多低級處理的功能,但仍然保持著跨平臺的特性,以一個標準規格寫出的C語言程...

至簡設計法:程序設計(2)

由潘文明先生開創的IC/FPGA至簡設計法,具備劃時代的意義。這種設計方法不僅將IC/FPGA學習難度降到了最低,同時將設計過程變得簡單,并規范了代碼避免了混亂,將出錯幾率降到最低。...

基于ZYNQ FPGA與PC的IP設計與驗證方案(4)

Zynq-7000嵌入式處理平臺系列的每款產品均采用帶有NEON及雙精度浮點引擎的雙核ARMCortex-A9MPCore處理系統,該系統通過硬連線完成了包括L1,L2緩存、存儲器控制器以及常用外設在內的全面集成。...

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |