10EDA20 - DIODE - 1A 200V TJ = 150C - Nihon Inter Electronics Corporation

2022-11-04 17:22:44

10EDA40 - Low Forward Voltage drop Diode - Nihon Inter Electronics Corporation

2022-11-04 17:22:44

10EDA60 - DIODE - 1A 600V TJ = 150C - Nihon Inter Electronics Corporation

2022-11-04 17:22:44

EDA是干什么的,可以給以個(gè)答復(fù)嗎?

2013-11-02 12:52:15

獻(xiàn)上EDA,電子鐘一個(gè)哈哈哈{:12:}

2013-11-14 16:05:15

EDA60-15 - AC - DC ENCLOSED SWITCHING POWER SUPPLY - Chinfa Electronics Ind. Co., Ltd.

2022-11-04 17:22:44

EDA實(shí)用教程

2012-08-20 11:18:48

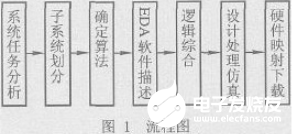

描述的高層次綜合技術(shù)不斷涌現(xiàn)。---作為現(xiàn)代集成電路設(shè)計(jì)的重點(diǎn)與熱點(diǎn),fpga設(shè)計(jì)一般采用自頂向下、由粗到細(xì)、逐步求精的方法。設(shè)計(jì)最頂層是指系統(tǒng)的整體要求,最下層是指具體的邏輯電路實(shí)現(xiàn)。自頂向下是將數(shù)字

2013-09-02 15:19:20

編譯和編程下載,這被稱為數(shù)字邏輯電路的高層次設(shè)計(jì)方法。 作為現(xiàn)代電子系統(tǒng)設(shè)計(jì)的主導(dǎo)技術(shù),EDA具有兩個(gè)明顯特征:即并行工程(Concurrent Engineering)設(shè)計(jì)和自頂向下

2008-06-26 16:16:11

級(jí)描述轉(zhuǎn)化為RTL描述的高層次綜合技術(shù)不斷涌現(xiàn)。---作為現(xiàn)代集成電路設(shè)計(jì)的重點(diǎn)與熱點(diǎn),F(xiàn)PGA設(shè)計(jì)一般采用自頂向下、由粗到細(xì)、逐步求精的方法。設(shè)計(jì)最頂層是指系統(tǒng)的整體要求,最下層是指具體的邏輯電路

2008-06-27 10:26:34

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-18 07:33:04

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-27 08:01:28

。EDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,設(shè)計(jì)人員按照“自頂向下”(Top唱down)的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵電路用一片或幾片專用集成電路(ASIC)實(shí)現(xiàn),然后采用

2019-02-21 09:41:58

功能設(shè)計(jì)和結(jié)構(gòu)設(shè)計(jì),并通過電氣連接網(wǎng)表將兩者結(jié)合在一起,以實(shí)現(xiàn)工程設(shè)計(jì)。90年代為ESDA階段, ESDA的基本特征是設(shè)計(jì)人員按“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵部分用一片

2008-06-26 10:13:58

和結(jié)構(gòu)設(shè)計(jì),并通過電氣連接網(wǎng)表將兩者結(jié)合在一起,以實(shí)現(xiàn)工程設(shè)計(jì)。90年代為ESDA階段, ESDA的基本特征是設(shè)計(jì)人員按“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵部分用一片或

2008-06-24 13:47:25

和結(jié)構(gòu)設(shè)計(jì),并通過電氣連接網(wǎng)表將兩者結(jié)合在一起,以實(shí)現(xiàn)工程設(shè)計(jì)。90年代為ESDA階段, ESDA的基本特征是設(shè)計(jì)人員按“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵部分用一片或

2008-06-12 10:01:04

EDA技術(shù)是什么?EDA常用軟件有哪些?電子電路設(shè)計(jì)與仿真工具包括哪些呢?

2022-01-24 06:34:54

EDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,它的基本特征是:設(shè)計(jì)人員按照“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵電路用一片或幾片專用集成電路(ASIC)實(shí)現(xiàn),然后采用硬件

2019-10-08 14:25:32

EDA技術(shù)的發(fā)展ESDA技術(shù)的基本特征是什么?EDA技術(shù)的基本設(shè)計(jì)方法有哪些?

2021-04-21 07:21:25

請(qǐng)問什么是EDA?那么FPGA是EDA的一種,為什么要有EDA這么一個(gè)總的概念?

2014-07-09 18:13:42

`現(xiàn)在最新的EDA軟件是什么軟件?還有proteus軟件和protel等等一系列的軟件區(qū)別大嗎?哪個(gè)EDA軟件比較適用廣泛?請(qǐng)大神幫助解決這些疑問!謝謝了!`

2013-03-21 12:41:17

求eda軟件,哪位大俠發(fā)下呢{:1:}

2014-04-17 23:18:07

誰能幫忙整一個(gè)EDA的12路搶答器和EDA的溫度計(jì)啊?跪求了~~~~~~~

2008-12-28 21:30:06

EDA鼠標(biāo)增強(qiáng)工具EDAHelper,布線輔助、鼠標(biāo)快捷工具,很好用的。通用工具,PROTEL,cadence都能用。 本軟件是多種EDA軟件的鼠標(biāo)增強(qiáng)工具,綠色單文件,支持Win9x/NT

2019-04-08 14:41:33

剛學(xué)習(xí)eda。用什么軟件學(xué)習(xí)比較好 最好是中文版的

2013-02-08 14:29:50

有哪位大神知道eda里的QUARTURE II軟件下的VHDL語言設(shè)計(jì)能生成電路圖嗎?

2016-05-12 18:35:50

M38064EDA-XXXSP - SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER - Renesas Technology Corp

2022-11-04 17:22:44

M38065EDA-XXXSP - SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER - Renesas Technology Corp

2022-11-04 17:22:44

M38066EDA-XXXSP - SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER - Renesas Technology Corp

2022-11-04 17:22:44

M38068EDA-XXXSP - SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER - Renesas Technology Corp

2022-11-04 17:22:44

M38069EDA-XXXSP - SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER - Renesas Technology Corp

2022-11-04 17:22:44

SMLZ13EDA - High brightness - Rohm

2022-11-04 17:22:44

WS4612EDA-5/TR

2023-03-29 22:43:42

業(yè)內(nèi)現(xiàn)有多少種EDA設(shè)計(jì)軟件?具體是哪些?其每一種EDA軟件分別導(dǎo)出的文件格式是什么類型?

2013-08-15 20:43:11

什么是EDA技術(shù)?EDA是電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation)縮寫,是90年代初從CAD(計(jì)算機(jī)輔助設(shè)計(jì))、CAM(計(jì)算機(jī)輔助制造)、CAT(計(jì)算機(jī)輔助測(cè)試

2019-07-30 06:20:05

微波系統(tǒng)的設(shè)計(jì)越來越復(fù)雜,對(duì)電路的指標(biāo)要求越來越高,電路的功能越來越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿足系統(tǒng)設(shè)計(jì)的需要,使用微波EDA軟件工具進(jìn)行微波元器件

2019-07-30 07:27:53

對(duì)傳統(tǒng)電子系統(tǒng)設(shè)計(jì)方法與現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法進(jìn)行了比較,引出了基于EDA技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)電路,提出現(xiàn)場(chǎng)可編程門陣列(FPGA) 是近年來迅速發(fā)展的大規(guī)模可編程專用集成電路(ASIC

2019-11-01 07:24:42

(Electronic Design Automation)具有一定的代表性。EDA技術(shù)是一種基于芯片的現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法。它的優(yōu)勢(shì)主要集中在能用HDL語言進(jìn)行輸入、進(jìn)行PEn(可編程器件)的設(shè)計(jì)與仿真等系統(tǒng)

2019-10-08 08:02:17

對(duì)傳統(tǒng)電子系統(tǒng)設(shè)計(jì)方法與現(xiàn)代電子系統(tǒng)設(shè)計(jì)方法進(jìn)行了比較,引出了基于EDA技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)電路,提出現(xiàn)場(chǎng)可編程門陣列(FPGA)是近年來迅速發(fā)展的大規(guī)模可編程專用集成電路(ASIC

2019-09-03 06:17:15

【作者】:劉雪冬【來源】:《華南理工大學(xué)》2009年【摘要】:自頂向下的設(shè)計(jì)方法及裝配建模技術(shù)是在消費(fèi)品行業(yè)應(yīng)用比較成熟的一種設(shè)計(jì)方法和理論;但是有鑒于通用機(jī)械設(shè)計(jì)的復(fù)雜性、多樣性和關(guān)聯(lián)性等特點(diǎn)

2010-04-24 09:20:57

頂向下、由粗到細(xì),逐步分解的設(shè)計(jì)方法,最頂層電路是指系統(tǒng)的整體要求,最下層是具體的邏輯電路的實(shí)現(xiàn)。自頂向下的設(shè)計(jì)方法將一個(gè)復(fù)雜的系統(tǒng)逐漸分解成若干功能模塊,從而進(jìn)行設(shè)計(jì)描述,并且應(yīng)用EDA 軟件平臺(tái)

2008-06-24 13:48:14

能力和高度的靈活性。其主要優(yōu)點(diǎn):與結(jié)構(gòu)無關(guān)、多平臺(tái)、豐富的設(shè)計(jì)庫、開放的界面、全集成化、支持多種硬件描述語言( HDL) 等。設(shè)計(jì)流程 數(shù)字系統(tǒng)的設(shè)計(jì)采用自頂向下、由粗到細(xì),逐步分解的設(shè)計(jì)方法,最頂層

2008-06-16 08:47:47

如何實(shí)現(xiàn)擴(kuò)頻通信調(diào)制器自頂向下的設(shè)計(jì)?如何實(shí)現(xiàn)擴(kuò)頻通信調(diào)制器的仿真測(cè)試?

2021-04-29 06:46:04

本文利用先進(jìn)的EDA軟件,用VHDL硬件描述語言采用自頂向下的模塊化設(shè)計(jì)方法,完成了具有相序自適應(yīng)功能的雙脈沖數(shù)字移相觸發(fā)器的IP軟核設(shè)計(jì)。

2021-04-28 06:39:00

學(xué)習(xí)EDA多哦那個(gè)什么軟件啊,現(xiàn)在。

2011-10-11 19:12:40

微波系統(tǒng)的設(shè)計(jì)越來越復(fù)雜,對(duì)電路的指標(biāo)要求越來越高,電路的功能越來越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿足系統(tǒng)設(shè)計(jì)的需要,使用微波EDA軟件工具進(jìn)行微波元器件

2019-06-19 07:13:37

求高人幫忙推薦一篇基于EDA實(shí)習(xí)LCD顯示器的方法!求高人幫忙推薦一篇基于EDA實(shí)習(xí)LCD顯示器的方法!求高人幫忙推薦一篇基于EDA實(shí)習(xí)LCD顯示器的方法!馬上就做畢業(yè)設(shè)計(jì)了一頭霧水求高人指點(diǎn)

2012-10-21 12:25:14

。設(shè)計(jì)方法也因此發(fā)生了根本性的變化。 由傳統(tǒng)的“自底向上”的設(shè)計(jì)方法轉(zhuǎn)變?yōu)橐环N新的“自頂向下”的設(shè)計(jì)方法。 “自頂向下”的設(shè)計(jì)方法的設(shè)計(jì)流程如下:第一步進(jìn)行行為設(shè)計(jì),確定該電子系統(tǒng)或 ASIC 芯片

2019-02-27 14:00:22

用Labview程序控制板子,向下發(fā)送命令用什么方法呀?

2015-06-06 10:17:22

小弟剛剛開始接觸EDA。要做一個(gè)關(guān)于EDA常用仿真軟件的project,但是我看EDA仿真軟件不要太多啊,還分什么“電路設(shè)計(jì)與仿真工具、PCB設(shè)計(jì)軟件、IC設(shè)計(jì)軟件、PLD設(shè)計(jì)工具及其它EDA軟件

2014-05-15 20:57:06

第1章 緒論 1.1 關(guān)于EDA 1.2 關(guān)于VHDL 1.3 關(guān)于自頂向下的系統(tǒng)設(shè)計(jì)方法 1.4 關(guān)于應(yīng)用 VHDL的 EDA過程 1.5 關(guān)于在系統(tǒng)編程技術(shù) 1.6 關(guān)于FPGA/CPLD的優(yōu)勢(shì) 1.7

2008-06-04 10:24:06 1682

1682 北京革新創(chuàng)展科技有限公司研制的B-ICE-EDA/SOPC FPGA平臺(tái)集多功能于一體,充分滿足EDA、SOPC、ARM、DSP、單片機(jī)相互結(jié)合的實(shí)驗(yàn)教學(xué),是電子系統(tǒng)設(shè)計(jì)創(chuàng)新實(shí)驗(yàn)室、嵌入式系統(tǒng)實(shí)驗(yàn)室

2022-03-09 11:18:52

基于單芯片系統(tǒng)是電子技術(shù)發(fā)展的主流,可改變傳統(tǒng)的系統(tǒng)軟、硬件設(shè)計(jì)方法,介紹了單芯片系統(tǒng)的支撐技術(shù)——自頂向下設(shè)計(jì)方法的思想,討論了其相關(guān)的信號(hào)處理系統(tǒng)設(shè)計(jì)自

2009-02-22 01:22:11 26

26 EDA技術(shù)概述EDA技術(shù)的特點(diǎn):采用HDL作為設(shè)計(jì)輸入庫的支持簡(jiǎn)化設(shè)計(jì)文檔管理強(qiáng)大的系統(tǒng)建模、電路仿真功能具有自

2009-12-07 14:08:00 0

0 介紹EDA技術(shù)的特點(diǎn)以及設(shè)計(jì)流程,強(qiáng)調(diào)EDA仿真技術(shù)在現(xiàn)代電子系統(tǒng)的重要地位及作用。以modelsim和quartus 2為平臺(tái),采用自頂向下分層次、模塊化的設(shè)計(jì)方法,設(shè)計(jì)了一個(gè)帶整點(diǎn)報(bào)時(shí)和星期

2010-02-24 16:03:40 57

57 EDA(電子設(shè)計(jì)自動(dòng)化)代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,它的基本特征是:設(shè)計(jì)人員按照“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵

2010-07-19 16:53:33 29

29 首先關(guān)于層次圖的創(chuàng)建有兩種方法:1.自頂而向下設(shè)計(jì);2.自低向上設(shè)計(jì);不管那種設(shè)

2006-04-16 20:43:43 1559

1559

基于CPLD和Embedded System的LED點(diǎn)陣顯示系統(tǒng)實(shí)現(xiàn)

摘要:采用自頂向下的設(shè)計(jì)思想,綜合運(yùn)用EDA 技術(shù)、CPLD技術(shù)和共享式雙口RAM,解決了大屏幕LED點(diǎn)陣顯示屏無閃爍

2008-11-01 15:36:08 882

882

現(xiàn)代數(shù)字系統(tǒng)的設(shè)計(jì)一般都采用自頂向下的模塊化設(shè)計(jì)方法。即從整個(gè)系統(tǒng)的功能出發(fā),將系統(tǒng)分割成若干功能模塊。在自頂向下劃分的過程中,最重要的是將系統(tǒng)或子系統(tǒng)按計(jì)算機(jī)組

2011-05-28 13:44:59 10848

10848

FPGA的常用設(shè)計(jì)方法包括自頂向下和自下而上,目前大規(guī)模FPGA設(shè)計(jì)一般選擇自頂向下的設(shè)計(jì)方法。 所謂自頂向下設(shè)計(jì)方法, 簡(jiǎn)單地說,就是采用可完全獨(dú)立于芯片廠商及其產(chǎn)品結(jié)構(gòu)的描述語

2011-09-06 15:08:50 363

363 EDA 技術(shù)的基本特征是采用具有系統(tǒng)仿真和綜合能力的高級(jí)語言描述。它一般采用自頂向下的模塊化設(shè)計(jì)方法。但是由于所設(shè)計(jì)的數(shù)字系統(tǒng)的規(guī)模大小不一,且系統(tǒng)內(nèi)部邏輯關(guān)系復(fù)雜,如何

2011-09-16 21:27:10 2287

2287

通過模塊之間的調(diào)用實(shí)現(xiàn)自頂向下的設(shè)計(jì)目的:學(xué)習(xí)狀態(tài)機(jī)的嵌套使用實(shí)現(xiàn)層次化、結(jié)構(gòu)化設(shè)計(jì)。

2017-02-11 05:53:38 2658

2658

本文開始詳細(xì)的闡述了eda是什么技術(shù)以及eda的設(shè)計(jì)方法,其次闡述了eda的設(shè)計(jì)技巧,詳細(xì)的分析了eda為什么又叫單片機(jī)的原因,最后介紹了EDA的應(yīng)用及發(fā)展趨勢(shì)。

2018-03-12 11:40:53 21853

21853

由于電子技術(shù)的飛速發(fā)展,使得基于EDA技術(shù)的電子系統(tǒng)設(shè)計(jì)方法得以廣泛應(yīng)用。EDA技術(shù)已成為現(xiàn)代系統(tǒng)設(shè)計(jì)和電子產(chǎn)品研發(fā)的有效工具,成為電子工程師應(yīng)具備的基本能力。本文首先介紹了EDA技術(shù)主要特征及精髓,其次介紹了EDA技術(shù)的因公及發(fā)展趨勢(shì),最后闡述了如何高效的學(xué)習(xí)EDA技術(shù)。

2018-04-27 09:21:55 39262

39262 DxDesigner是業(yè)界功能最強(qiáng)大的原理圖設(shè)計(jì)輸入工具,支持自頂向下以及自底向上的設(shè)計(jì)方式,支持層次化的設(shè)計(jì)輸入與設(shè)計(jì)管理,也支持平面方式以及混合方式的原理圖輸入方式,支持分頁設(shè)計(jì)。Mentor功能強(qiáng)大,但使用并不復(fù)雜,很多功能通過菜單或者快捷鍵、筆畫方式可以很快的運(yùn)行。

2019-02-14 15:09:58 1125

1125

ESDA代表了當(dāng)今電子設(shè)計(jì)技術(shù)的最新發(fā)展方向,其基本特征是:設(shè)計(jì)人員按照“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵電路用一片或幾片專用集成電路(ASIC)實(shí)現(xiàn),然后采用硬件

2019-02-15 15:16:05 5334

5334

1. 用EDA 技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的目標(biāo)是最終完成ASIC 的設(shè)計(jì)與實(shí)現(xiàn)。2. 可編程器件分為CPLD 和FPGA 。3. 隨著EDA 技術(shù)的不斷完善與成熟, 自頂向下的設(shè)計(jì)方法更多的被應(yīng)用于

2019-08-02 17:11:10 5

5 三方面的電子設(shè)計(jì)工作,即集成電路設(shè)計(jì)、電子電路設(shè)計(jì)以及PCB設(shè)計(jì)。總之,EDA技術(shù)的基本特征是采用具有系統(tǒng)仿真和綜合能力的高級(jí)語言描述。它一般采用自頂向下的模塊化設(shè)計(jì)方法。但是由于所設(shè)計(jì)的數(shù)字系統(tǒng)的規(guī)模大小不一,且系統(tǒng)內(nèi)部邏輯關(guān)系復(fù)雜,如何劃分邏輯功能模塊便成為設(shè)計(jì)數(shù)字系統(tǒng)的最重要的任務(wù)。

2020-01-21 16:50:00 9552

9552

本設(shè)計(jì)采用EDA技術(shù),以硬件描述語言VHDL為系統(tǒng)邏輯描述手段設(shè)計(jì)文件,在QUARTUSII工具軟件環(huán)境下, 采用自頂向下的設(shè)計(jì)方法, 由各個(gè)基本模塊共同構(gòu)建了一個(gè)基于FPGA的數(shù)字鐘。

2020-08-28 09:36:00 30

30 通過設(shè)計(jì)實(shí)例,深入理解自頂向下設(shè)計(jì)方法,系統(tǒng)設(shè)計(jì)規(guī)范、系統(tǒng)設(shè)計(jì)、模塊設(shè)計(jì)和系統(tǒng)仿真與實(shí)現(xiàn)各階段的設(shè)計(jì)內(nèi)容,初步掌握規(guī)范的數(shù)字系統(tǒng)設(shè)計(jì)方法并實(shí)踐。

2021-01-19 17:21:03 11

11 硬件的設(shè)計(jì)使用軟件的方式來進(jìn)行,盡管目標(biāo)系統(tǒng)是硬件,但整個(gè)設(shè)計(jì)和修改過程如同完成軟件設(shè)計(jì)一樣方便和高效。 2. 自頂向下(top-down)的設(shè)計(jì)方法 傳統(tǒng)的電路設(shè)計(jì)方法基本上都自向上的,即首先確定可用的,然后根據(jù)這些器件進(jìn)行邏輯設(shè)計(jì),完

2021-09-28 17:19:51 13801

13801 Robei EDA注冊(cè)方法

2022-02-12 17:15:44 1374

1374 近日,英諾達(dá)(成都)電子科技有限公司自研EDA軟件新獲三項(xiàng)國(guó)家發(fā)明專利授權(quán)。 近日,英諾達(dá)(成都)電子科技有限公司自研EDA軟件新獲三項(xiàng)國(guó)家發(fā)明專利授權(quán)。它們分別是: ? ?· 消息處理方法、裝置

2022-10-27 14:20:07 1123

1123 本文檔包含Jim Kurose和Keith Ross編寫的《計(jì)算機(jī)網(wǎng)絡(luò):自頂向下方法(第7版)》復(fù)習(xí)題和問題的參考答案。這些答案只對(duì)指導(dǎo)老師有效。請(qǐng)不要復(fù)制或者分發(fā)給其他人(即使是其他指導(dǎo)老師)。請(qǐng)

2023-03-13 14:23:08 0

0 eda

2023-04-06 09:17:52 0

0 目標(biāo)檢測(cè)(Object Detection)是計(jì)算機(jī)視覺領(lǐng)域中的重要任務(wù),用于在圖像或視頻中定位和識(shí)別出多個(gè)感興趣的對(duì)象。EDA(Enhancement, Detection, and Augmentation)方法是一種綜合的目標(biāo)檢測(cè)方法

2023-07-20 14:43:06 2688

2688 EDA工具的技術(shù)來源主要包括描述統(tǒng)計(jì)學(xué)、可視化技術(shù)、探索性數(shù)據(jù)分析方法、數(shù)據(jù)挖掘技術(shù),以及可交互性與用戶界面設(shè)計(jì)。這些技術(shù)和方法的應(yīng)用使得EDA工具成為數(shù)據(jù)分析和發(fā)現(xiàn)中不可或缺的工具之一。

2023-07-21 15:09:44 1314

1314 EDA技術(shù)和VHDL是緊密相連的。在EDA設(shè)計(jì)中,VHDL通常用于描述數(shù)字電路的功能和行為,并通過邏輯分析器、仿真器等工具進(jìn)行仿真、分析和驗(yàn)證。EDA技術(shù)則提供通用的集成設(shè)計(jì)平臺(tái)和工具來支持VHDL的設(shè)計(jì)、仿真、綜合和布局等流程。

2023-08-09 12:41:00 2908

2908 本研究院自2023年1月5日起正式投入運(yùn)營(yíng),項(xiàng)目總投資額達(dá)3億元人民幣,下設(shè)三個(gè)研發(fā)機(jī)構(gòu),分別致力于高性能EDA技術(shù)、中國(guó)EDA產(chǎn)業(yè)標(biāo)準(zhǔn)以及半導(dǎo)體量測(cè)技術(shù)研究及其產(chǎn)業(yè)化。

2023-12-14 09:25:21 1813

1813 EDA(即Ethylene diamine,乙二胺)是一種無色透明的液體,分子式為C2H8N2。它是一種有機(jī)化合物,常用作化學(xué)試劑。下面將詳細(xì)介紹EDA的性質(zhì)、制備方法、應(yīng)用場(chǎng)景以及相關(guān)的注意事項(xiàng)等

2024-02-18 16:24:24 7596

7596 EDA,是指電子設(shè)計(jì)自勱化( Electronic Design Automation)用于芯片設(shè)計(jì)時(shí)的重要工具,設(shè)計(jì)時(shí)工程師會(huì)用程式碼規(guī)劃芯片功能,再透過EDA 工具讓程式碼轉(zhuǎn)換成實(shí)際的電路設(shè)計(jì)圖。

2024-02-27 13:54:11 2794

2794

電子發(fā)燒友網(wǎng)站提供《具有向下/向上模式控制的同步向上/向下計(jì)數(shù)器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-05-14 09:41:37 1

1 在電子設(shè)計(jì)領(lǐng)域,隨著技術(shù)的發(fā)展,EDA(電子設(shè)計(jì)自動(dòng)化)工具已經(jīng)成為工程師們不可或缺的助手。與傳統(tǒng)的設(shè)計(jì)方法相比,EDA工具提供了更為高效、精確的設(shè)計(jì)流程。 1. 設(shè)計(jì)流程的自動(dòng)化程度 EDA

2024-11-08 13:47:13 1996

1996 EDA設(shè)計(jì)效率的有效方法: 一、選擇合適的EDA工具 根據(jù)需求選擇工具 :不同的EDA工具適用于不同的硬件設(shè)計(jì)任務(wù),如數(shù)字電路設(shè)計(jì)、模擬電路設(shè)計(jì)、電路板設(shè)計(jì)等。在選擇EDA工具時(shí),應(yīng)根據(jù)具體的設(shè)計(jì)需求和項(xiàng)目要求來確定。 考慮工具的功能和性能 :選擇具備所需功能和性能的EDA工具

2024-11-08 14:23:51 1699

1699

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論