新微型化嵌入式并行光纖模塊

Avago Technologies(安華高科技)宣布,公司已經(jīng)開發(fā)完成業(yè)內(nèi)最緊湊并且創(chuàng)新的低成本高帶寬并行光纖解決方案之一,

2010-03-25 17:35:51 662

662 ? “EDA工具” 可能很多人都不清楚什么是EDA,EDA(Electronics Design Automation)是電子設(shè)計(jì)自動(dòng)化的縮寫。 跟CAD,CAM一樣,都是輔助設(shè)計(jì)工具,而EDA則用

2021-01-05 14:20:08 7599

7599

短板,構(gòu)建覆蓋芯片設(shè)計(jì)全流程的自主工具鏈。 ? 聚焦存儲(chǔ)芯片EDA,實(shí)現(xiàn)全流程國產(chǎn)化突破 ? 后摩爾時(shí)代,芯片性能提升轉(zhuǎn)向“尺寸微縮、新原理器件、集成芯片”三路徑并行,推動(dòng)EDA技術(shù)演進(jìn)為貫通“物理極限—架構(gòu)創(chuàng)新—系統(tǒng)協(xié)同”的使能

2025-12-21 07:51:00 10347

10347 EDA是干什么的,可以給以個(gè)答復(fù)嗎?

2013-11-02 12:52:15

闡述了EDA技術(shù)與FPGA設(shè)計(jì)應(yīng)用。關(guān)鍵詞:電子設(shè)計(jì)自動(dòng)化;現(xiàn)場可編程門陣列;復(fù)雜可編程邏輯器件;專用集成電路;知識(shí)產(chǎn)權(quán);甚高速集成電路硬件描述語言

2019-06-18 07:33:04

闡述了EDA技術(shù)與FPGA設(shè)計(jì)應(yīng)用。關(guān)鍵詞:電子設(shè)計(jì)自動(dòng)化;現(xiàn)場可編程門陣列;復(fù)雜可編程邏輯器件;專用集成電路;知識(shí)產(chǎn)權(quán);甚高速集成電路硬件描述語言

2019-06-27 08:01:28

EDA是電子設(shè)計(jì)自動(dòng)化(electrondesignautomation)的縮寫,是在20世紀(jì)90年代初,從CAD(計(jì)算機(jī)輔助設(shè)計(jì))、CAM(計(jì)算機(jī)輔助制造)、CAT(計(jì)算機(jī)輔助測試)和CAE

2019-02-21 09:41:58

EDA技術(shù)是什么?EDA常用軟件有哪些?電子電路設(shè)計(jì)與仿真工具包括哪些呢?

2022-01-24 06:34:54

EDA技術(shù)的發(fā)展ESDA技術(shù)的基本特征是什么?EDA技術(shù)的基本設(shè)計(jì)方法有哪些?

2021-04-21 07:21:25

EDA(Electronic Design Automation,電子設(shè)計(jì)自動(dòng)化)是一種基于計(jì)算機(jī)軟件的電子系統(tǒng)設(shè)計(jì)技術(shù),通過自動(dòng)化工具和算法輔助完成電路設(shè)計(jì)、驗(yàn)證、制造等全流程。以下是EDA的主要

2025-06-23 07:59:40

請(qǐng)問什么是EDA?那么FPGA是EDA的一種,為什么要有EDA這么一個(gè)總的概念?

2014-07-09 18:13:42

`現(xiàn)在最新的EDA軟件是什么軟件?還有proteus軟件和protel等等一系列的軟件區(qū)別大嗎?哪個(gè)EDA軟件比較適用廣泛?請(qǐng)大神幫助解決這些疑問!謝謝了!`

2013-03-21 12:41:17

Eesof EDA先進(jìn)設(shè)計(jì)系統(tǒng)選擇能實(shí)現(xiàn)您夢想的設(shè)計(jì)

2019-09-17 13:58:02

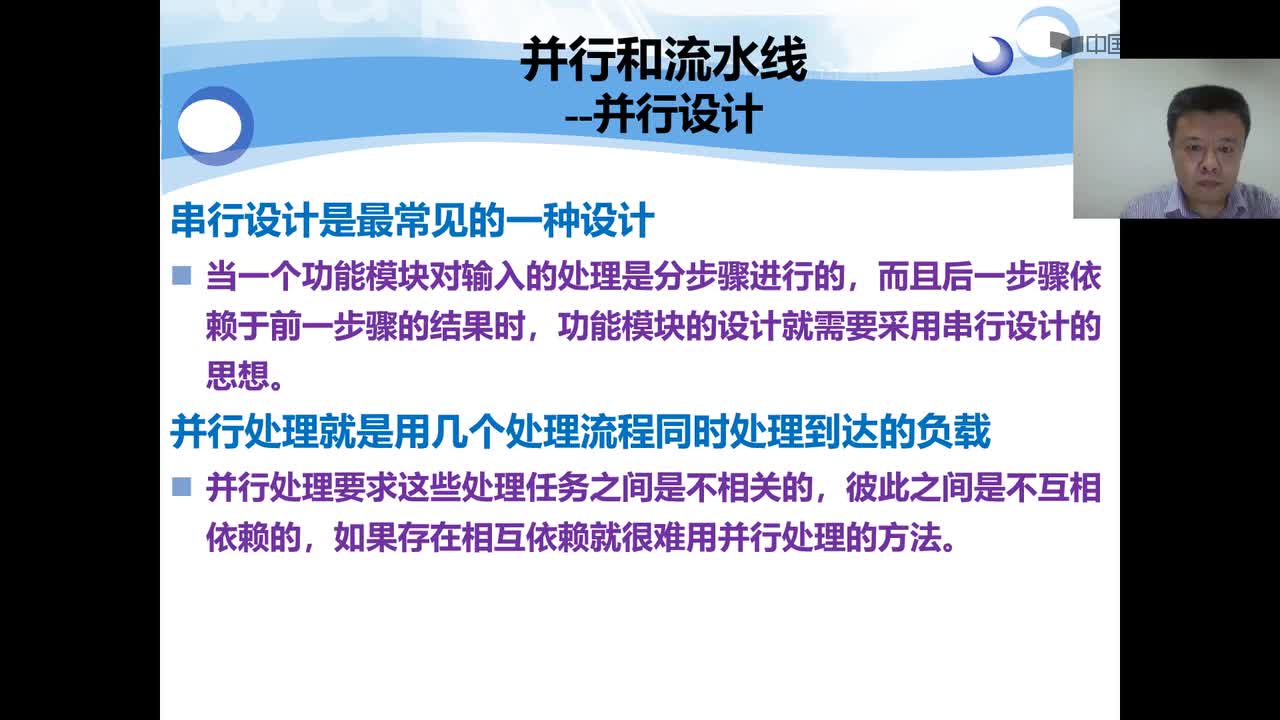

/ FPGA 為物質(zhì)基礎(chǔ)的EDA 技術(shù)誕生了。它具有電子技術(shù)高度智能化、自動(dòng)化的特點(diǎn),打破了軟硬件最后的屏障,使得硬件設(shè)計(jì)如同軟件設(shè)計(jì)一樣簡單。它作為一種創(chuàng)新技術(shù)正在改變著數(shù)字系統(tǒng)的設(shè)計(jì)方法、設(shè)計(jì)過程

2017-06-29 11:35:30

SMLZ13EDA - High brightness - Rohm

2022-11-04 17:22:44

WS4612EDA-5/TR

2023-03-29 22:43:42

什么是EDA技術(shù)?EDA是電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation)縮寫,是90年代初從CAD(計(jì)算機(jī)輔助設(shè)計(jì))、CAM(計(jì)算機(jī)輔助制造)、CAT(計(jì)算機(jī)輔助測試

2019-07-30 06:20:05

,電路的設(shè)計(jì)與工藝研制日益復(fù)雜化,如何進(jìn)一步提高電路性能、降低成本,縮短電路的研制周期,已經(jīng)成為電路設(shè)計(jì)的一個(gè)焦點(diǎn),而EDA技術(shù)是設(shè)計(jì)的關(guān)鍵。EDA技術(shù)的范疇包括電子工程設(shè)計(jì)師進(jìn)行產(chǎn)品開發(fā)的全過程,以及

2019-07-30 07:27:53

非常適合對(duì)FPGA進(jìn)行編程。借助于LabVIEW FPGA Module軟件,用戶可以創(chuàng)建出自定義的測量和控制硬件,而無需了解低級(jí)別的硬件描述語言或板級(jí)設(shè)計(jì)。用戶可以借助于個(gè)性化的并行化硬件來進(jìn)行實(shí)現(xiàn)特殊

2014-12-12 16:02:30

隨著EDA平臺(tái)服務(wù)趨于網(wǎng)絡(luò)化,如何通過對(duì)資源和流程的有效管理,為用戶提供更為方便安全的遠(yuǎn)程EDA平臺(tái)調(diào)用服務(wù),已成為關(guān)鍵問題。在FPGA開發(fā)平臺(tái)上集成了EDA工具環(huán)境,并部署SGD軟件。在實(shí)現(xiàn)遠(yuǎn)程

2019-07-16 21:09:34

物聯(lián)網(wǎng)、人工智能、大數(shù)據(jù)等新興技術(shù)的推動(dòng),集成電路技術(shù)和計(jì)算機(jī)技術(shù)得到蓬勃發(fā)展。電子產(chǎn)品設(shè)計(jì)系統(tǒng)日趨數(shù)字化、復(fù)雜化和大規(guī)模集成化,各種電子系統(tǒng)的設(shè)計(jì)軟件應(yīng)運(yùn)而生。在這些專業(yè)化軟件中,EDA

2019-10-08 08:02:17

如何實(shí)現(xiàn)樹莓派并行控制電機(jī)?

2021-10-28 06:54:11

16QAM調(diào)制原理是什么?16QAM調(diào)制器的FPGA實(shí)現(xiàn)如何利用EDA技術(shù)來實(shí)現(xiàn)16QAM調(diào)制器的設(shè)計(jì)?

2021-04-15 06:00:48

本論文設(shè)計(jì)制作了一種并行網(wǎng)絡(luò)化實(shí)時(shí)彩色分析虛擬儀器。為了實(shí)現(xiàn)高速測試系統(tǒng)互聯(lián),本文采用了100M以太網(wǎng)和TCP/IP網(wǎng)絡(luò)通信協(xié)議。

2021-05-08 07:43:57

,電路的設(shè)計(jì)與工藝研制日益復(fù)雜化,如何進(jìn)一步提高電路性能、降低成本,縮短電路的研制周期,已經(jīng)成為電路設(shè)計(jì)的一個(gè)焦點(diǎn),而EDA技術(shù)是設(shè)計(jì)的關(guān)鍵。EDA技術(shù)的范疇包括電子工程設(shè)計(jì)師進(jìn)行產(chǎn)品開發(fā)的全過程,以及

2019-06-19 07:13:37

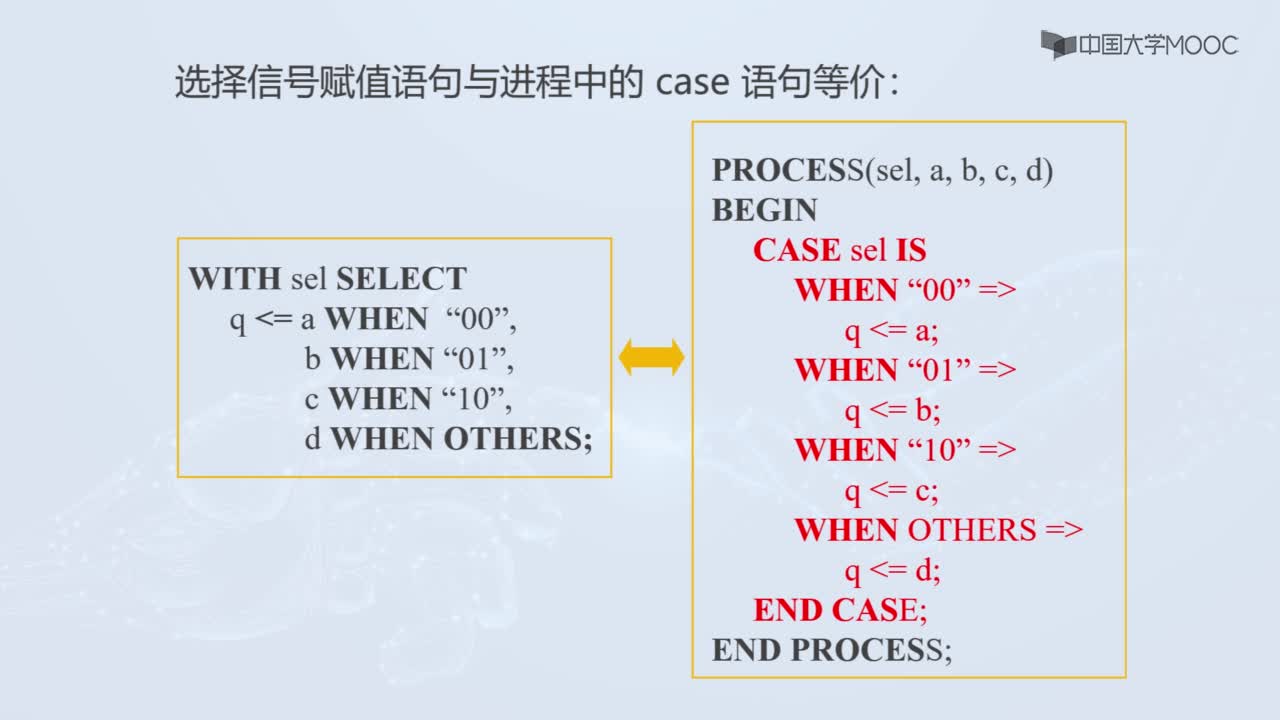

本文介紹一種使用硬件描述語言VHDL來實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對(duì)問題進(jìn)行建模,并對(duì)模型進(jìn)行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對(duì)Petri網(wǎng)

2019-08-16 07:52:03

如果一個(gè)擾碼器現(xiàn)在做并行化,例如要求輸入位寬為32位,那么本原多項(xiàng)式如何確定?在實(shí)現(xiàn)的過程中,如果想使用并行,是不是需要將同移位寄存器長一致的周期后狀態(tài)機(jī)算出來呢?不很明白為什么可以實(shí)現(xiàn)并行化,輸出不是還是一位一位的數(shù)據(jù)的嗎?是不是將對(duì)應(yīng)的周期數(shù)計(jì)算出結(jié)果嗎?

2019-05-07 16:53:54

`電子設(shè)計(jì)自動(dòng)化EDA緒論`

2017-02-24 13:20:20

隨著集成電路技術(shù)的發(fā)展,電子設(shè)計(jì)自動(dòng)化(EDA)逐漸成為重要的設(shè)計(jì)手段,已經(jīng)廣泛應(yīng)用于模擬與數(shù)字電路系統(tǒng)等許多領(lǐng)域。電子設(shè)計(jì)自動(dòng)化是一種實(shí)現(xiàn)電子系統(tǒng)或電子產(chǎn)品自動(dòng)化設(shè)計(jì)的技術(shù),它與電子技術(shù)

2021-07-29 09:24:20

Mali T604 GPU的結(jié)構(gòu)是由哪些部分組成的?Mali T604 GPU的編程特性有哪些?Mali GPU的并行化計(jì)算模型是怎樣構(gòu)建的?基于Mali-T604 GPU的快速浮點(diǎn)矩陣乘法并行化該如何去實(shí)現(xiàn)?

2021-04-19 08:06:26

北京革新創(chuàng)展科技有限公司研制的B-ICE-EDA/SOPC FPGA平臺(tái)集多功能于一體,充分滿足EDA、SOPC、ARM、DSP、單片機(jī)相互結(jié)合的實(shí)驗(yàn)教學(xué),是電子系統(tǒng)設(shè)計(jì)創(chuàng)新實(shí)驗(yàn)室、嵌入式系統(tǒng)實(shí)驗(yàn)室

2022-03-09 11:18:52

基于VxWorks的多DSP并行處理系統(tǒng)的實(shí)現(xiàn)

2009-03-29 12:31:18 17

17 簡介:Robei是一款可視化的跨平臺(tái)EDA設(shè)計(jì)工具,具有超級(jí)簡化的設(shè)計(jì)流程,最新可視化的分層設(shè)計(jì)理念,透明開放的模型庫以及非常友好的用戶界面。Robei軟件將芯片設(shè)計(jì)高度抽象化,并精簡到

2022-07-27 10:24:32

隨著數(shù)字化技術(shù)和系統(tǒng)軟、硬件技術(shù)的不斷提高,“軟件化雷達(dá)”成為雷達(dá)信號(hào)處理領(lǐng)域的最新研究方向。通用并行信號(hào)處理平臺(tái)是“軟件化雷達(dá)”的重要組成部分。本文討論了

2009-05-25 14:11:51 28

28 MPI是目前集群系統(tǒng)中最重要的并行編程工具,它采用消息傳遞的方式實(shí)現(xiàn)并行程序間通信。在MPI 并行程序設(shè)計(jì)中實(shí)現(xiàn)負(fù)載平衡有著重要的意義,可以減少運(yùn)行時(shí)間,提高M(jìn)PI 并行

2009-07-30 10:56:28 35

35 數(shù)字電池EDA入門之VHDL程序實(shí)現(xiàn)集

2009-12-07 14:14:57 0

0 EDA技術(shù)與可編程ASIX的設(shè)計(jì)實(shí)現(xiàn)方案

2009-12-07 14:34:27 6

6 EDA技術(shù)復(fù)習(xí)精華

VHDL部分EDA:電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation)EDA技術(shù)包含4個(gè)基本條件:1.大規(guī)

2010-02-23 16:40:23 0

0 EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn)

集成電路經(jīng)過半個(gè)世紀(jì)的演變,發(fā)展,目前品種已達(dá)5萬種,年產(chǎn)量以億塊計(jì).

2010-06-19 09:50:19 24

24 本文在介紹了等效采樣的原理和方法的基礎(chǔ)上提出了一種基于EDA技術(shù)的實(shí)現(xiàn)方案。借助高速發(fā)展的EDA技術(shù),可以方便地產(chǎn)生采樣信號(hào),大大簡化采樣觸發(fā)電路,解決了傳統(tǒng)等效采樣

2010-08-03 10:48:54 19

19 6.1 Synopsys EDA軟件6.2 Cadence EDA軟件6.3 Tanner EDA軟件6.4 SPICE 基本語句

Synopsys公司(Nasdaq: SNPS)是為全球集成電路設(shè)計(jì)提供電子設(shè)計(jì)自動(dòng)化(EDA)軟件工具的主導(dǎo)企業(yè)。為全球

2010-09-03 20:48:05 164

164 摘要:提出了一種巧妙實(shí)現(xiàn)DSP并行自舉的方法,即采用“兩次下載法”,利用DSP自身對(duì)FLASH編程,以實(shí)現(xiàn)DSP的并行自舉。這種在系統(tǒng)編程的DSP自舉實(shí)現(xiàn)方式無需文件

2006-03-11 17:39:50 1758

1758

提出了一種具有高并行度機(jī)載SAR實(shí)時(shí)并行成像算法實(shí)現(xiàn)方案。對(duì)實(shí)測數(shù)據(jù)進(jìn)行成像處理結(jié)果表明,文中所提方案能夠滿足實(shí)時(shí)成像處理要求,同時(shí)與傳統(tǒng)實(shí)時(shí)成像處理系統(tǒng)相比較,能夠大幅

2011-11-30 17:25:06 55

55 設(shè)計(jì)了一種高可靠并行環(huán)網(wǎng)和冗余處理算法,并可在Linux平臺(tái)下實(shí)現(xiàn)。實(shí)驗(yàn)表明,單網(wǎng)故障時(shí),并行環(huán)網(wǎng)可無縫切換,收發(fā)終端間的丟包率為0。

2011-12-26 11:12:38 9

9 介紹了EDA(電子設(shè)計(jì)自動(dòng)化)技術(shù)的發(fā)展過程和基本特征,然后以EDA技術(shù)作為開發(fā)手段,基于硬件描述語言VHDL,以可編程邏輯器件CPLD為核心,實(shí)現(xiàn)了一個(gè)數(shù)字系統(tǒng)的設(shè)計(jì)。

2012-02-16 16:21:03 33

33 EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn),下來看看。

2016-05-19 15:16:15 0

0 電子設(shè)計(jì)自動(dòng)化EDA緒論

2016-12-11 23:38:39 0

0 虛擬化環(huán)境下多GPU并行計(jì)算研究_閔芳

2017-01-03 15:24:45 0

0 TMS320VC5416DSP并行自舉方案的設(shè)計(jì)與實(shí)現(xiàn)

2017-10-20 09:15:22 12

12 在智能視頻監(jiān)控領(lǐng)域中,運(yùn)動(dòng)目標(biāo)檢測已經(jīng)成為主要研究課題之一,針對(duì)傳統(tǒng)的方向梯度直方圖(HOG)算法并行化程度低等問題,采用了基于嵌入式GPU的并行化改進(jìn)的運(yùn)動(dòng)目標(biāo)檢測方法,通過大數(shù)據(jù)量樣本圖片和實(shí)時(shí)

2017-11-15 11:33:48 7

7 多核處理器、FPGA和PCI Express正在改變現(xiàn)代PC機(jī)的版圖,并幫助LabVIEW圖形化編程根據(jù)工程師應(yīng)用邏輯的數(shù)據(jù)流向,實(shí)現(xiàn)真正的并行化處理和并行化測量。利用NI TestStand軟件

2017-11-16 20:31:57 10951

10951

方面并行性的優(yōu)勢,提出了基于OpenCL的JPEG壓縮算法并行化設(shè)計(jì)方法。將JPEG算法功能分解為多個(gè)內(nèi)核程序,內(nèi)核之間通過事件信息傳遞進(jìn)行順序控制,并在GPU+CPU的異構(gòu)平臺(tái)上完成了并行算法的仿真驗(yàn)證。實(shí)驗(yàn)結(jié)果表明,與CPU串行處理方式

2017-11-21 16:57:15 4

4 在分布式計(jì)算和內(nèi)存為王的時(shí)代,Spark作為基于內(nèi)存計(jì)算的分布式框架技術(shù)得到了前所未有的關(guān)注與應(yīng)用。著重研究BIRCH算法在Spark上并行化的設(shè)計(jì)和實(shí)現(xiàn),經(jīng)過理論性能分析得到并行化過程中時(shí)間消耗

2017-11-23 11:24:44 0

0 界集成電路設(shè)計(jì)占有越來越舉足輕重的作用,EDA技術(shù)的標(biāo)準(zhǔn)化刻不容緩,EDA技術(shù)的國際標(biāo)準(zhǔn)化以及國內(nèi)標(biāo)準(zhǔn)化必將大大促進(jìn)我國集成電路行業(yè)的發(fā)展。 電子設(shè)計(jì)技術(shù)的核心是EDA(electronic design automation,電子設(shè)計(jì)自動(dòng)化)技術(shù),EDA是指以計(jì)算機(jī)為工作平

2017-11-28 11:45:02 0

0 從而實(shí)現(xiàn)數(shù)據(jù)分塊;其次,利用.NET環(huán)境下的Parallel類對(duì)分塊數(shù)據(jù)進(jìn)行并行暈渲處理,得到各個(gè)分塊數(shù)據(jù)的暈渲結(jié)果;最后,對(duì)各個(gè)分塊數(shù)據(jù)的暈渲圖像進(jìn)行拼接,從而得到完整的地貌暈渲圖像。實(shí)驗(yàn)結(jié)果表明:并行化改進(jìn)算法的計(jì)算效率明

2017-11-30 10:30:22 0

0 帶有全球定位系統(tǒng)( GPS)功能設(shè)備的增多,產(chǎn)生大量的時(shí)空軌跡數(shù)據(jù),給數(shù)據(jù)的存儲(chǔ)、傳輸和處理帶來了沉重的負(fù)擔(dān)。為了減輕這種負(fù)擔(dān),各種軌跡壓縮方法也隨之產(chǎn)生。提出了一種基于MapReduce的并行化

2017-12-03 09:51:19 0

0 基于MapReduce計(jì)算框架,采用Gibbs抽樣方法的并行化LDA主題模型的建立方法。利用分布式計(jì)算框架MapReduce研究了LDA主題模型的并行化實(shí)現(xiàn),并且考察了該并行計(jì)算程序的計(jì)算性能。通過對(duì)Hadoop并行計(jì)算與單機(jī)計(jì)算進(jìn)行實(shí)驗(yàn)對(duì)比,發(fā)現(xiàn)該方法在處理大規(guī)

2017-12-05 13:51:04 0

0 針對(duì)當(dāng)前大量遺產(chǎn)代碼無法重復(fù)利用的問題,設(shè)計(jì)一種新的編譯工具將C的串行代碼轉(zhuǎn)換為基于MPI+OpenMP的混合并行編程代碼,降低了并行編程的開發(fā)成本。首先,通過對(duì)JavaCC的優(yōu)化,實(shí)現(xiàn)一種可以解析

2017-12-12 14:53:39 0

0 本文主要介紹了一種基于EDA技術(shù)的出租車計(jì)費(fèi)系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),采用EDA技術(shù)的層次化設(shè)計(jì)方法設(shè)計(jì)出租車計(jì)費(fèi)器,用VHDL編寫各個(gè)功能模塊,實(shí)現(xiàn)底層設(shè)計(jì);用原理圖輸入方式描述各模塊間的關(guān)系,實(shí)現(xiàn)頂層設(shè)計(jì)。

2017-12-25 09:20:54 5049

5049

基于可視化庫( VTK)可視化技術(shù)的特點(diǎn),討論可視化流水線機(jī)制和并行程序的基本結(jié)構(gòu)。針對(duì)計(jì)算流體力學(xué)可視化后處理實(shí)現(xiàn)的問題,介紹和使用VTK顏色映射算法,并編寫對(duì)計(jì)算流體力學(xué)結(jié)果數(shù)據(jù)彩色云圖顯示

2017-12-29 17:04:40 1

1 本文研究了基于Spark的并行數(shù)據(jù)挖掘,并將其應(yīng)用到了流程對(duì)象數(shù)據(jù)分析中。文章通過對(duì)串行的流程 對(duì)象數(shù)據(jù)挖掘算法流的研究,提出了一種基于Spark并行計(jì)算框架的并行化算法流解決方案,并通過編 程實(shí)現(xiàn)、并行效率測試、算法調(diào)優(yōu),最終得出一個(gè)并行效果良好的并行數(shù)據(jù)挖掘方案。該并行方案明顯 提高了計(jì)算效率。

2017-12-30 17:31:04 0

0 基于圖論和共享內(nèi)存編程模型,對(duì)因子分解過程進(jìn)行并行化改造,實(shí)現(xiàn)了潮流修正線性方程的并行求解。最后,對(duì)比智能電網(wǎng)調(diào)度控制系統(tǒng)調(diào)度員潮流軟件,進(jìn)行了分析測試。測試結(jié)果表明,隨著計(jì)算規(guī)模的增大,所提出的實(shí)現(xiàn)方法計(jì)算效

2018-03-19 11:09:51 0

0 神經(jīng)網(wǎng)絡(luò)訓(xùn)練硬件具備越來越強(qiáng)大的數(shù)據(jù)并行化處理能力。基于 GPU 或定制 ASIC 的專門系統(tǒng)輔以高性能互連技術(shù)使得能夠處理的數(shù)據(jù)并行化規(guī)模前所未有地大,而數(shù)據(jù)并行化的成本和收益尚未得到深入研究

2018-12-19 10:39:21 4229

4229

隨著EDA平臺(tái)服務(wù)趨于網(wǎng)絡(luò)化,如何通過對(duì)資源和流程的有效管理,為用戶提供更為方便安全的遠(yuǎn)程EDA平臺(tái)調(diào)用服務(wù),已成為關(guān)鍵問題。在FPGA開發(fā)平臺(tái)上集成了EDA工具環(huán)境,并部署SGD軟件。

2019-01-20 09:34:31 2075

2075

EDA(ElectronicDesignAutomation)即電子設(shè)計(jì)自動(dòng)化軟件,是進(jìn)行芯片自動(dòng)化設(shè)計(jì)的基礎(chǔ),處于集成電路設(shè)計(jì)產(chǎn)業(yè)的上游,是實(shí)現(xiàn)超大規(guī)模集成電路設(shè)計(jì)的前提。

2020-05-29 15:07:03 3477

3477 隨著多核技術(shù)的不斷發(fā)展,并行方法已經(jīng)成為一種處理較大規(guī)模問題的手段,同時(shí)在許多領(lǐng)域取得了成功地應(yīng)用。目前,并行算法的實(shí)現(xiàn)主要基于兩種標(biāo)準(zhǔn): MPI(Message Passing

2020-11-04 10:40:00 0

0 當(dāng)前中國在EDA領(lǐng)域所面臨的國際形式非常嚴(yán)峻,由于EDA工具難度大、壁壘高,想要在短時(shí)間內(nèi),實(shí)現(xiàn)突圍困難重重。國產(chǎn)EDA在數(shù)字仿真、驗(yàn)證等多個(gè)環(huán)節(jié)存在多處的短板,對(duì)國外的依賴大,產(chǎn)業(yè)鏈脆弱。但好在

2020-10-25 09:19:46 2702

2702 Word,他說:EDA的實(shí)現(xiàn)需要EDA軟件,就像打字需要Word一樣,而且芯片設(shè)計(jì)用的EDA軟件比打字更復(fù)雜、更精細(xì)、技術(shù)含量更高,有了EDA工具,芯片的設(shè)計(jì)、布局、布線、仿真、版圖都可以通過自動(dòng)化來實(shí)現(xiàn)。 事實(shí)上,EDA和裝備材料一起被稱為集成電路產(chǎn)業(yè)的

2020-10-25 09:56:13 3080

3080 具體而言,該論文從可編程性、并行化表示、性能優(yōu)化、系統(tǒng)架構(gòu)和自動(dòng)并行化技術(shù)等幾方面對(duì)分布式并行 ML 展開了研究,并認(rèn)為分布式并行機(jī)器學(xué)習(xí)可以同時(shí)實(shí)現(xiàn)簡潔性和高效性。

2020-11-23 11:30:32 2231

2231 的設(shè)計(jì)來例系統(tǒng)地介紹了利用多種EDA工具進(jìn)行 FPGA協(xié)同設(shè)計(jì)的實(shí)現(xiàn)原理及方法近年來,隨著微電子學(xué)的迅速發(fā)展以及SoC(System on Chip ,片上系統(tǒng)) 技術(shù)在設(shè)計(jì)領(lǐng)域引起的深刻變革,EDA(Electornic Design Automatic ,電子設(shè)計(jì)自動(dòng)化) 工具在系統(tǒng)設(shè)計(jì)中的地位愈發(fā)重要

2020-11-27 17:57:34 29

29 華為開始打破不投供應(yīng)商的慣例為加速實(shí)現(xiàn)半導(dǎo)體國產(chǎn)替代,華為正式進(jìn)入EDA領(lǐng)域。

2020-12-29 13:44:52 2000

2000 如果把芯片比喻為設(shè)計(jì)精美的工藝品,電子設(shè)計(jì)自動(dòng)化(EDA)工具就是雕刻它的刻刀。

2021-02-15 09:22:00 1917

1917 出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設(shè)計(jì)并建立了FPGA驗(yàn)證平臺(tái).為了對(duì)多核處理器平臺(tái)性能進(jìn)行評(píng)測,提出了基于OpenMP的3種可行的圖像處理領(lǐng)域的經(jīng)典算法SUSAN算法的并行化方法:直接并行化

2021-02-03 16:26:00 8

8 計(jì)算機(jī)結(jié)構(gòu)并行化程序的替代方法的研究說明。

2021-03-26 14:24:49 10

10 Python 在程序并行化方面多少有些聲名狼藉。撇開技術(shù)上的問題,例如線程的實(shí)現(xiàn)和 GIL,我覺得錯(cuò)誤的教學(xué)指導(dǎo)才是主要問題。

2022-04-19 17:09:02 1524

1524 Python 在程序并行化方面多少有些聲名狼藉。撇開技術(shù)上的問題,例如線程的實(shí)現(xiàn)和 GIL,我覺得錯(cuò)誤的教學(xué)指導(dǎo)才是主要問題。常見的經(jīng)典 Python 多線程、多進(jìn)程教程多顯得偏"重"。而且往往隔靴搔癢,沒有深入探討日常工作中最有用的內(nèi)容。

2022-06-12 16:31:48 2198

2198 實(shí)現(xiàn)國產(chǎn)的EDA全流程工具,一直是大家最關(guān)注的,可以說是所有中國EDA人的重要目標(biāo)。目前華大九天已經(jīng)實(shí)現(xiàn)模擬IC設(shè)計(jì)的全流程,而數(shù)字全流程依舊等待著大家將多個(gè)點(diǎn)工具連接起來。

2022-09-21 11:11:09 1003

1003 與集成電路產(chǎn)業(yè)重點(diǎn)突破和整體提升。其中提到,加快EDA核心技術(shù)攻關(guān)。推動(dòng)模擬、數(shù)字、射頻集成電路等EDA工具軟件實(shí)現(xiàn)全流程國產(chǎn)化。支持開展先進(jìn)工藝制程、新一代智能、超低功耗等EDA技術(shù)的研發(fā)。意見稿

2022-10-11 16:17:00 3468

3468 AN4666_運(yùn)用GPIO和DMA實(shí)現(xiàn)并行同步通信

2022-11-21 17:07:13 2

2 Python 在程序并行化方面多少有些聲名狼藉。撇開技術(shù)上的問題,例如線程的實(shí)現(xiàn)和 GIL,我覺得錯(cuò)誤的教學(xué)指導(dǎo)才是主要問題。常見的經(jīng)典 Python 多線程、多進(jìn)程教程多顯得偏"重"。而且往往隔靴搔癢,沒有深入探討日常工作中最有用的內(nèi)容。

2023-04-06 11:00:10 995

995 此外,當(dāng)前內(nèi)核的外部內(nèi)存訪問效率低下,因此內(nèi)存訪問也是瓶頸。在這種狀態(tài)下,即使進(jìn)行循環(huán)并行化,內(nèi)存訪問最終也會(huì)成為瓶頸。

2023-04-17 09:12:14 1850

1850 中國數(shù)字EDA應(yīng)該利用后發(fā)優(yōu)勢,對(duì)現(xiàn)有國際標(biāo)準(zhǔn)取其精華、去其糟粕,建立自己的技術(shù)體系和行業(yè)標(biāo)準(zhǔn),以此作為技術(shù)創(chuàng)新和產(chǎn)品研發(fā)的基礎(chǔ),推動(dòng)形成穩(wěn)定的國產(chǎn)EDA全流程工具鏈,進(jìn)而快速實(shí)現(xiàn)普遍的工業(yè)部署。

2023-04-18 14:32:37 832

832 EDA技術(shù)的核心是將電子設(shè)計(jì)自動(dòng)化,實(shí)現(xiàn)快速、準(zhǔn)確、方便的電路設(shè)計(jì)和仿真,以提高電路設(shè)計(jì)的效率和可靠性。通過提高EDA技術(shù)的運(yùn)用水平,可以縮短電路設(shè)計(jì)周期,降低設(shè)計(jì)成本,提高電路設(shè)計(jì)的成功率,并且推動(dòng)整個(gè)電子產(chǎn)品行業(yè)的發(fā)展。

2023-04-19 15:38:40 13841

13841 板級(jí)EDA軟件(PCB EDA軟件)也是一種電子設(shè)計(jì)自動(dòng)化(EDA)軟件,它是用于電子電路設(shè)計(jì)中電路板布局、布線、驗(yàn)證、生產(chǎn)等工作的一款軟件程序。該軟件允許工程師創(chuàng)建電路原理圖,以及通過軟件輔助完成電路布局和布線的設(shè)計(jì)工作。

2023-05-03 05:42:00 8334

8334 以上工藝所需EDA工具,基本實(shí)現(xiàn)了14nm以上EDA工具國產(chǎn)化!在2023年將完成對(duì)14nm以上EDA工具的全面驗(yàn)證! 近來不僅是華為,國產(chǎn)EDA龍頭華大九天也是好消息不斷! 好消息!華大九天部分?jǐn)?shù)字工具支持5nm并且已經(jīng)開始商業(yè)化。可以在文末翻看筆者之前分享的文

2023-04-20 03:00:57 7632

7632 EDA技術(shù)的核心并不是仿真,仿真只是EDA技術(shù)的一個(gè)重要環(huán)節(jié)。EDA技術(shù)的核心是利用計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具,將電路設(shè)計(jì)自動(dòng)化,實(shí)現(xiàn)從電路設(shè)計(jì)到制造的全流程自動(dòng)化。仿真只是在這一流程中的重要一環(huán),用于驗(yàn)證設(shè)計(jì)的正確性、可靠性和穩(wěn)定性等方面。

2023-04-24 18:22:15 3720

3720 國內(nèi)芯片EDA的國產(chǎn)化率也有顯著提高,從2018年的6.24%增加到2020年的11.48%。

2024-01-22 16:28:44 3396

3396 電子發(fā)燒友網(wǎng)站提供《并行CRC實(shí)現(xiàn).pdf》資料免費(fèi)下載

2025-05-20 17:26:15 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論