1、 應用背景

基于ARM+FPGA的高速同步數據采集方案,解決了數據采集的同步性問題,與以往

2010-07-22 16:36:17 1633

1633 本文設計的高速數據采集系統是應用于芯片現場測試的實時數據采集系統,該數據采集系統的數據采集率是2 Gbps。

2012-04-19 10:05:11 3613

3613

本文介紹了一種高速實時數據采集系統的設計方案。本方案先簡要介紹了CYUSB3014 芯片的特點和固件程序,對傳感器輸出信號進行放大濾波處理,然后將其轉換為數字信號。在FIFO 緩存后,使用USB

2014-02-18 15:25:25 6965

6965

本文提出了一種基于FPGA+ARM的高速數據采集板的設計方案。該方案采用FPGA完成高速數據采集,通過ARM對FPGA進行控制管理。利用DMA技術實現了FPGA與ARM之間的數據采集接口設計方案,并

2014-03-04 09:04:38 2557

2557 本文設計了一種高速實時數據采集系統。該系統首先對傳感器輸出信號進行放大濾波處理,然后將其轉換為數字信號。經FIFO緩存后,使用USB的猝發傳輸模式傳輸到計算機,文中給出了硬件電路,并簡要介紹了CYUSB3014芯片的特點和固件程序。##系統硬件設計與上位機軟件設計。

2014-03-26 12:05:49 12788

12788 當前,越來越多的設計應用領域要求具有高精度的A/D轉換和實時處理功能。在實時數據采集處理系統設計中,一般需要考慮數據采集以及對采集數據的處理。而對于大數據量的實時數據采集處理系統來說,保持數據高速傳輸也是該系統性能的關鍵因素。

2018-12-17 09:10:00 7393

7393

高速實時頻譜儀是對實時采集的數據進行頻譜分析,要達到這樣的目的,對數據采集系統的采樣精度、采樣率和存儲量等指標提出了更高的要求。而在高速數據采集系統中,ADC在很大程度上決定了系統的整體性能,而它們的性能又受到時鐘質量的影響。

2019-09-02 06:44:39

高速數據采集系統的硬件結構MAX7000系列CPLD及其開發平臺介紹CPLD在高速數據采集系統中的應用

2021-04-08 06:11:56

DSP的FPGA的高速數據采集系統的研究與設計,大家可以看看

2015-04-03 21:23:48

申請理由:本開發板為ARM系類,能移植Linux系統,可以實現快速高效的系統,并且能實現數據云共享。對于高速數據采集系統,開發板的資源可以適用,并且非常實用。項目描述:高速數據采集系統原理:通過高速

2015-07-17 14:43:58

對數據采集與處理系統提出了新的更高的要求,即高速度、高精度和高實時性。對數據采集與處理系統的設計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

介紹了基于AT89C52和ADS774的實時數據采集系統,對系統硬件結構、工作原理和軟件主要模塊功能和流程作了較詳細的論述,同時給出了核心程序。

2011-03-03 14:04:41

。為了實現高速、連續采樣的數據采集系統,本文介紹了一種基于 FPGA +AD7609的數據采集系統的構成及技術實現。采用 FPGA 作為主模塊,AD7609為數據采集模塊,并設計了硬件實現電路。實驗測試

2018-08-09 14:28:00

基于FPGA+DSP的高速數據采集系統設計

2012-06-27 17:23:53

24期摘 要:傳統的數據采集系統大都是由ARM+DSP實現的,雖然DSP的優勢在于數據處理,但是隨著FPGA技術的發展,很多FPGA已經可以取代DSP的作用了。尤其是在高速實時的數據采集領域,采集

2018-05-09 12:09:43

基于FPGA的數據采集系統IEE ... 介紹了數據采集系統中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設計,給出了系統硬件設計和FPGA邏輯設計,討論了IEEE1394總線

2012-08-11 15:43:47

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

基于FPGA的高速實時數據采集系統設計

2012-08-20 20:00:14

目前,在數據采集系統的硬件設計方案中,有采用通用單片機和USB相結合的方案,也有采用DSP和USB相結合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數據采集系統對速度要求;后者雖然可以實現

2019-09-05 07:22:57

數據采集系統中,采用藍牙無線通 信DFBM-CS120 芯片,實現高速實時數據信號采集和無線數據傳輸。與有線數據傳輸相比,更加方便靈活,具有較高的可靠性。在軟件設計上采用Windows CE 實時多任務系統

2021-10-26 06:30:00

率、高精度、多通道同步數據采集方案,可以通過監測者的要求完成多通道數據的同步采集并實現實時的網絡傳輸。 基于ARM+FPGA的高速同步

2010-08-31 09:14:55

方案。這里介紹一種MEMS器件微加速度計的數據采集設計方案,結合當前應用廣泛的處理芯片ARM和FPGA,給出了一種配置靈活、通用性強的數據采集方案。實驗中可準確采集美新加速度計MXR6150G/M

2020-11-25 06:17:24

基于ARM的藍牙實時數據采集系統

2015-03-26 17:41:52

基于LabVIEW和USB_CAN卡的實時數據采集系統及應用

2012-09-04 13:21:33

測量速度和精度。系統總體設計方案 本文提出了一種基于LABVIEW的USB接口高速數據采集系統的設計,充分利用DSP豐富的片上外設以及高性能的數字信號處理能力,將采集的數據經DSP處理后通過高速USB

2019-05-07 09:40:04

本帖最后由 eehome 于 2013-1-5 09:46 編輯

數據采集是對信號處理的重要手段。針對導引頭電壓的檢測需求.提出一種實時數據采集顯示系統設計方法。給出信號預處理電路

2011-03-08 14:24:55

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

高速多通道實時數據采集系統的方案在工業監控、環境監測等方面的應用非常廣泛。隨著科學技術的發展,數據采集技術正向著高精度、高速度、穩定可靠、集成化及實時系統的方向發展。并且通過搭載了最新的FPGA,使得產品的升級換代變得更加容易和便捷。

2019-10-23 08:12:56

各種數據通訊速度不一,刷新速度不一,監控中心的無法匯總形成真正的實時數據庫; 2)數據采集及傳輸穩定性差,數據因采集器故障、無線傳輸受到干擾情況發生頻率較多; 因此,此方案常常應用于市政、企事業單位等

2012-05-29 10:55:55

應用方案:實時數據加密

利用CPLD設計加密電路方便可行,能夠較好地實現加密功能。AG32系列MCU產品,在芯片內部內置了CPLD邏輯,可以有效地滿足各種數據采集需求,降低了客戶的BOM成本。以下方案

2024-01-15 08:57:23

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

怎么設計一款基于NI Scope實時數據采集系統?

2021-05-10 06:45:08

系統的數據采集的方法:方法1:實時數據庫使用OPC協議直接從DCS采集OPC的英文全稱是:OLE for Process Control,即:“面向處理控制的對象鏈接與嵌入”的標準接口技術,它是

2018-10-30 17:51:56

高速數據采集系統的硬件結構MAX7000系列CPLD及其開發平臺介紹CPLD在高速數據采集系統中的應用

2021-04-30 06:43:12

高速數據采集系統的硬件設計高速數據采集系統的軟件設計

2021-06-03 06:04:08

求一種多通道同步數據采集及壓縮系統的設計方案。

2021-04-28 06:13:04

如題。請問需要3通道同時數據采集,每通道200MHZ,計劃使用3片ADS4129或者ADS4128。可以不采用FPGA方案,直接通過DSP接收數據嗎?

研究了C665X系列DSP,UPP的最高速只有75MHZ。能有其他DSP或者ARM滿足要求嗎?

2025-01-23 08:35:45

說明基于USB 技術的實時數據采集系統的硬件、軟件實現;重點介紹PDIUSBD12帶并行總線的USB 接口器件以及基于多線程思想設計應用程序的方法。

2009-04-16 09:07:54 12

12 本文提出了一種基于USB HID 類的實時數據采集系統,詳細地介紹了該實時系統的軟件設計方案和固件、硬件設計方案,并給出了實際的測試結果,操作簡便、采集數據可靠,效

2009-05-27 15:47:48 34

34 提出了一種基于DSP 的高速數據采集系統的設計方案,對其中高速A/D、高速緩存。DSP 控制以及數據通訊接口等內容進行了討論,提出了更為有效的同步控制方式。該設計方案電路

2009-06-12 16:37:58 17

17 介紹了一種基于PCI-1714 的高速數據采集系統設計方案。系統以PCI-1714 高速數據采集卡為硬件平臺,借助研華32 位DLL 驅動程序接口,采用VC++高級語言編程對PCI-1714 進行硬件驅動和控制

2009-06-22 09:57:17 31

31 為滿足核聚變裝置EAST 極向場電源控制系統的實時性要求,設計了基于QNX 的實時數據采集系統。與一般的軟件觸發數據采集方式相比,本文采用的利用QNX 系統時鐘實現的數據實時采

2009-06-22 10:04:11 17

17 基于PCI總線的高速數據采集卡系統設計與實現:本文介紹一種基于PCI總線的高速數據采集卡系統的設計方法,討論了設計高速數據采集系統的關鍵技術,給出了系統整體設計方案和P

2009-06-22 19:04:54 55

55 本文對高速數據采集系統的設計進行了討論,介紹利用高速線性放大器、高速A/D 轉換芯片、ISP 器件制作的DMA 接口,設計以單片機為核心的高速數據采集系統的方法。關鍵詞: I

2009-07-15 11:16:00 22

22 本文介紹了一種簡便實用的高精度實時數據采集系統。該系統基于USB接口,采用MCU控制采樣,采樣精度可達16位。具有成本低、開發特別簡便、方便實用、可擴展性強等特點,可

2009-07-30 16:53:06 15

15 本文提出了一種用于雷達回波信號采集的高速數據采集系統。該系統實現了對數十兆赫的回波信號進行連續的采樣和存儲。系統通過FPGA控制數據連續采集、緩沖,通過PCI9056將緩沖區

2009-08-15 11:45:53 23

23 基于LabVIEW和USB-CAN卡的實時數據采集系統及應用:針對燃料電池電動汽車所用大功率DC/DC 變換器開發了一套基于LabVIEW 和USBCAN卡的實時數據采集和控制系統, 實現了PC 機與CAN 總線間

2009-09-18 09:36:26 366

366 本文介紹了一種基于FPGA 的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA 的實現方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現A/D 轉換器的控制電路、多路

2009-12-19 16:02:33 50

50 設計了一種基于ARM9 與Linux 的嵌入式實時數據采集系統。通過對數據采集實時理論的研究和對系統應用需求的分析選擇設計了系統的軟硬件,其中主要包括基于AD7892的采集模塊硬

2010-01-13 15:45:11 29

29 基于PC 機的多通道實時數據采集系統的設計

提出一種基于軟件的多通道實時數據采集方法并給出了設計方案、并且詳細介紹了動態鏈接庫的使用方法,以及在DEL P

2010-02-22 11:50:13 21

21 基于MAX3420的實時數據采集系統設計

針對TMSC3206000數字信號處理器的特點,設計了基于DSP和MAX3420的實時數據采集系統.

2010-06-11 17:26:23 39

39 摘要:介紹了基于AT89C52和ADS774的實時數據采集系統,對系統硬件結構、工作原理和軟件主要模塊功能和流程作了較詳細的論述,同時給出了核心程序。關鍵詞:單片機;A/D轉換

2010-07-07 13:09:23 53

53 基于USB-6281的高速數據采集系統的設計方案。系統以USB-6281高速數據采集卡為硬件平臺,借助NI-DAQmx驅動軟件,采用VC++高級語言編程對USB-6281進行硬件驅動和控制,實現了數據高速采

2010-11-22 16:26:49 30

30 討論了ARM系統中DMA通道的工作原理,并利用DMA技術設計了基于S3C2410和FPGA的CCD相機采集系統,給出了數據采集接口設計方案,以及Linux操作系統下接口的設備驅動程序。測試結果表明

2010-12-07 14:26:24 56

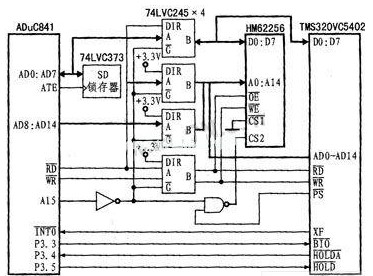

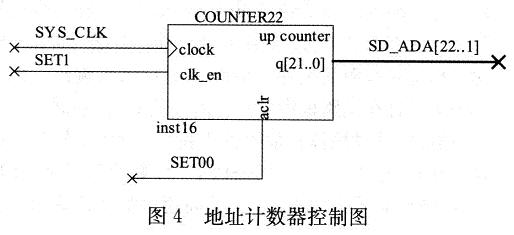

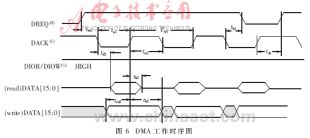

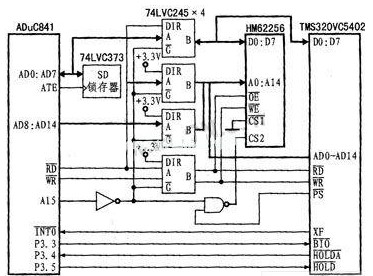

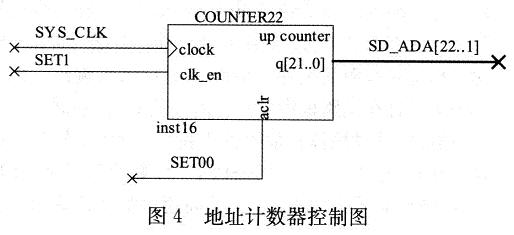

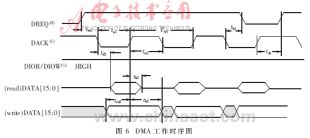

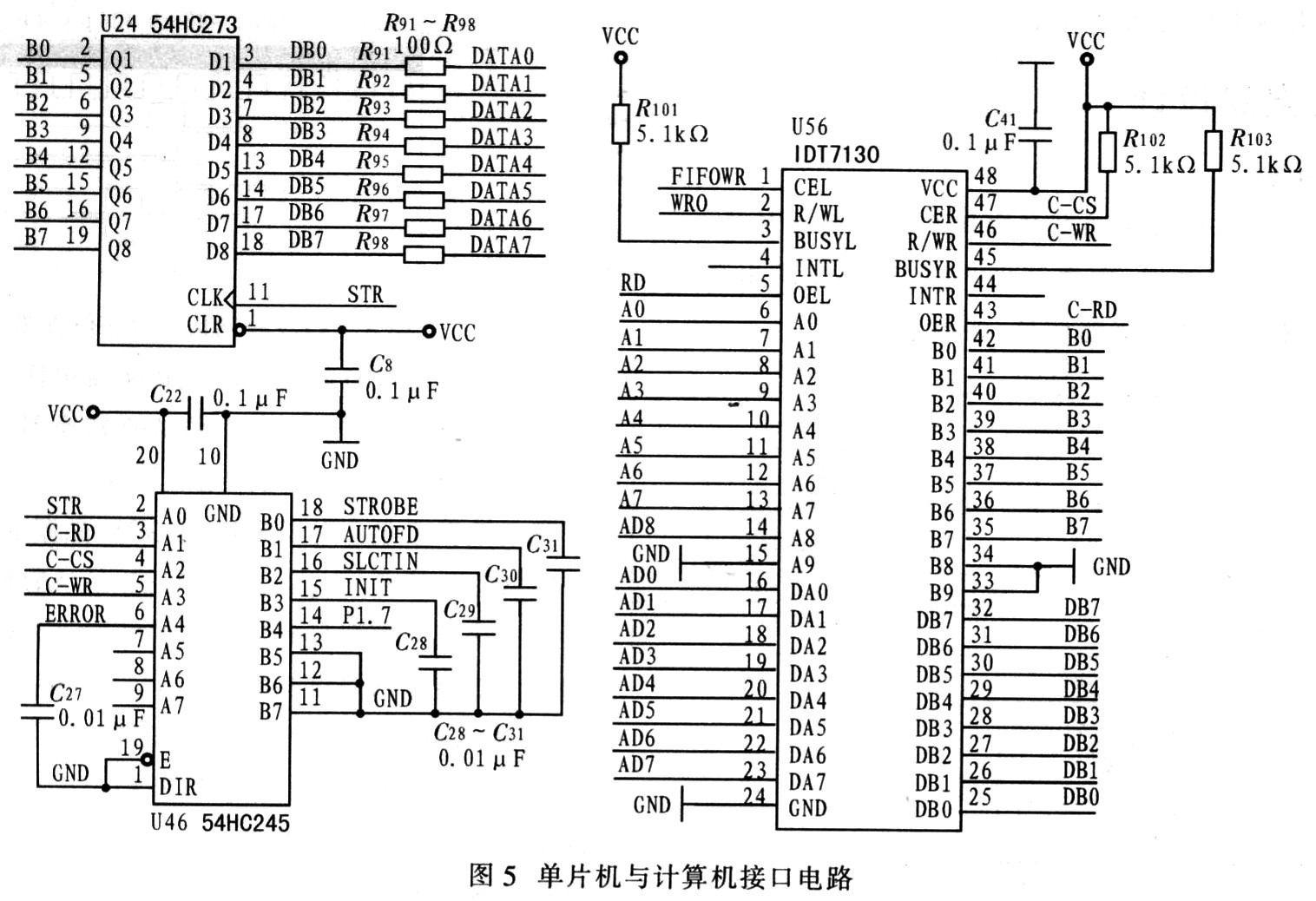

56 提出了一種基于ADuC841和TMS320VC5402的實時數據采集系統的設計方案,雙CPU通過DMA方式實現數據交換。實驗測試,該系統采樣數據精度高、傳輸速率快、性能穩定、數據存儲量大、易于

2010-12-14 16:40:55 70

70 驅動系統綜合測試儀等硬件設備完成數據的高速采集,實時上傳用戶自定義的波形數據和特征值數據。數據采集系統可以同時監控局域網內的1臺或多臺設備的測量數據,并進行數據的

2024-10-08 13:33:21

換體DMA高速數據采集電路的CPLD實現

介紹了換體DMA高速數據采集電路原理及其CPLD實現。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 1008

1008

采用FPGA的高速數據采集系統

隨著科學技術的發展,數據采集技術進入到越來越多的領域。目前,已廣泛應用于通信,圖像處理,軍事應用,消費電子,智能控制等方面

2009-04-20 11:03:13 2320

2320

基于USB2.0與FPGA技術的高速數據采集系統的設計

基于USB2.0與FPGA技術的高速數據采集系統的設計

近年來筆記本電腦迅速普及和更新,其中大部分已經

2009-04-22 19:56:15 1960

1960

基于單片機和CPLD實時數據采集顯示系統設計

1 引言 數據采集是分析模擬信號量數據的有效方法。而實時顯示數據是自動化檢測系統的現實需求。在測

2009-12-22 17:31:02 2170

2170

基于CPLD/FPGA高速數據采集系統的設計

0 引 言 傳統的數據采集系統一般采用單片機,系統大多通過PCI總線完成數據的傳輸。其缺點是數學運算能力差;

2010-01-27 09:35:01 792

792

基于ARM的藍牙實時數據采集系統的設計

摘要:本文提出了一種基于ARM的藍牙無線數據采集系統。結合嵌入式技術與藍牙技術的優勢,解決了傳統工業現場數據采集系統中

2010-02-02 11:27:03 1375

1375

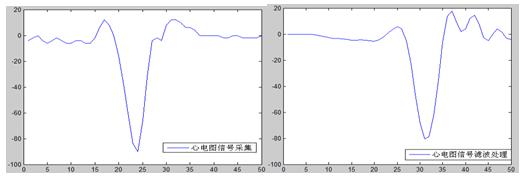

基于MATLAB的實時數據采集與分析研究

1、引言

數據采集系統涉及多學科,所研究的對象是物理或生物等各種非電或電信號。根據各種非

2010-02-22 09:34:49 4572

4572

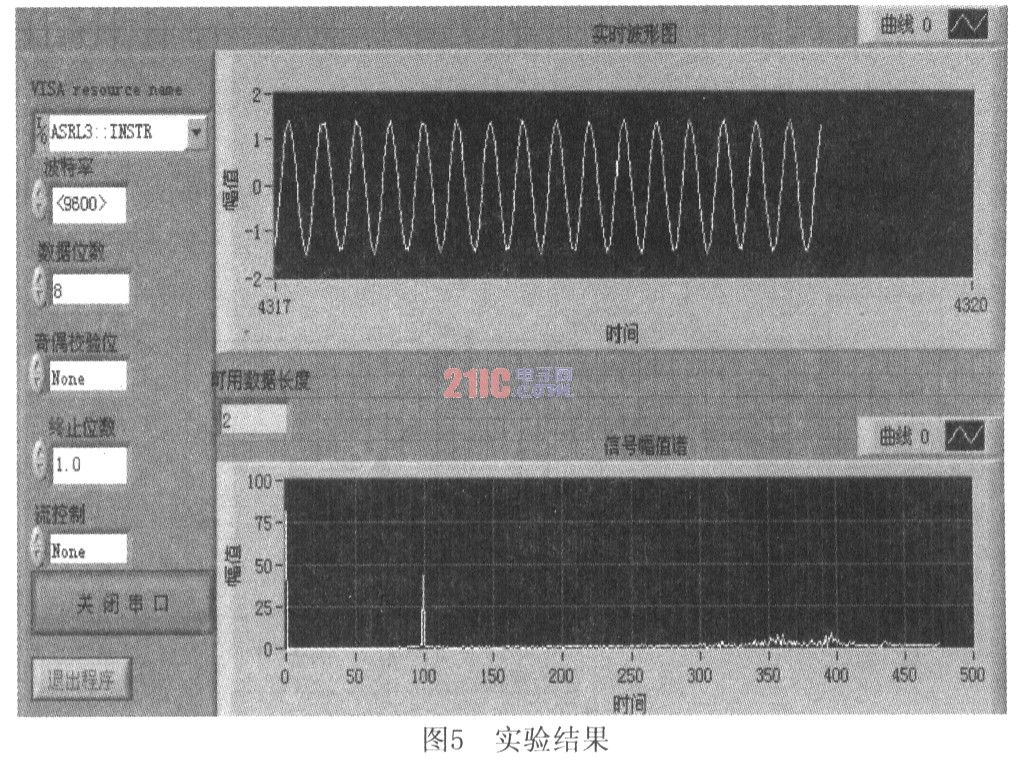

基于LabVIEW與USB接口的實時數據采集系統

摘要:本文設計了一種基于LabVIEW與STC12C5410AD單片機的數據采集系統。單片機采集到的數據通過CH341T芯片的USB轉串口的功能,實

2010-03-10 14:13:31 8247

8247

FPGA芯片在高速數據采集緩存系統中的應用

概 述在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA的時鐘頻率高,內部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

摘要:在介紹電容層析成像系統組成原理的基礎上,重新構建了一套數字化的數據采集系統,它具有較高的采集速度和分辨率真,著重分析了FPGA控制A/D采集和DSP響應中斷進行DMA傳輸的有關問題。 關鍵詞:DSP DMA 中斷服務程序 ECT

2011-02-28 12:36:44 50

50 介紹了一種高速實時數據采集系統的設計。該系統以FPGA作為邏輯控制的核心,以USB2.0作為與上位機數據傳輸的接口,能同時支持單端16路和差分8路模擬信號輸入,最大采樣率為200 kHz,

2011-09-29 17:16:36 63

63 針對數據采集系統有信號形式多樣、實時傳輸和靈活配置的要求,介紹了一種基于FPGA的數據采集和傳輸系統,以及系統數字電路的程序設計。該系統以現場可編程邏輯陣列(FPGA)作為

2011-09-29 17:31:04 54

54 恒頤基于ARM+FPGA的高速同步數據采集方案,解決了數據采集的同步性問題,與以往的數據采集方案相比,具有高精度、高速率、多參數同步測量、實時處理、網絡傳輸不受區域限制等特點

2012-11-27 10:51:24 1670

1670 本文在現有產品的基礎上提出了在高速實時數據采集系統中采 用“數字信號處理芯片嵌入式中央處理器”的設計思路,即將高速實時數據采集系統分成基于三星公司的S3C2410精簡指令處理器的核心板和基于現場

2016-04-18 10:02:17 0

0 在高速實時數據采集系統設計中 我們采用了“數字信號處理芯片 + 嵌入式中央處理器”的設計思路即將高速實時數據采集系統分成基于三星公司的S3C2410精簡指令處理器的核心板和基于現場可編程門陣列的高速

2016-04-18 14:12:30 1

1 高速數據采集系統中的FPGA的設計,下來看看

2016-05-10 11:24:33 15

15 于FPGA的高速多路數據采集系統的設計。

2016-05-10 13:45:28 41

41 基于FPGA的高速數據采集硬件系統設計.

2016-05-10 17:06:40 48

48 基于FPGA的高速數據采集系統接口設計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數據采集系統的設計,下來看看

2016-05-10 17:06:40 21

21 基于FPGA高速數據采集的解決方案,下來看看

2016-05-11 09:46:01 13

13 基于FPGA的高速數據采集系統設計,用ad芯片和sdram構成高速數據采集系統。

2016-05-17 09:49:51 35

35 基于FPGA的新型高速CCD圖像數據采集系統

2016-09-22 13:05:38 22

22 不高等問題。同時,為避免數據傳輸不及時,發生數據丟失,影響系統的可靠性和實時性,需設計開發高速數據采集系統。 設計中針對前端輸出約-25~25 mV,帶寬為20 MHz的信號,采用高帶寬,低噪聲,高數據傳輸率,高分辨率數模轉換

2017-10-30 16:34:44 11

11 ,該數據采集卡只適用于小系統的數據采集;參考文獻[2]介紹了基于AD1674實現的雙通道并行高速數據采集卡,可實現16路信號采集,采用ISA總線計算機接口。而對于更多路信號的采集處理,在實時性方面對數據采集系統提出了更高的要求,傳統的ISA總線接口的低

2017-12-02 10:05:01 1126

1126

介紹了一種基于FPGA的多路同步、實時數據采集新方案,著重對其硬件結構和控制邏輯進行了闡述,并從工程實踐方面給出了電路的實現原則。該方案控制方式靈活可變、具有一定的擴展性和通用性,已被成功地應用于雙模信息融合系統的設計中,實現了對雷達導引頭的多信號實時同步采集。

2018-10-12 16:14:59 17

17 介紹了一種基于FPGA的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA的實現方法,并用v∞L語言設計的狀態杌在Qmr嚙Ⅱ開發軟件中進行仿真。該系統在通用數據采集系統的基礎上,增加數據

2018-10-12 16:15:09 14

14 提出了FPGA之間以及FPGA與外圍A/D和D/A芯片的數據傳輸方案。最后揭示了光纖通信驅動的數據采集與控制過程及總線沖突解決策略。所設計的系統具有成本低、靈活性強的特點,實驗表明該系統能夠滿足可靠性和實時性要求。

2018-10-23 19:32:54 5

5 的TMS320C6713器件.該系統將A/D采樣的數據送往FPGA,經過FPGA預處理后送到DSP,最終通過USB接口送到主控臺,其系統的數據采集的實時速度最高可達到100 MB/s,適用于大部分的高速數據采集場合.

2018-11-07 17:18:24 20

20 設計了以FPGA器件XCSVIXS0為核心處理芯片的高速數據采集存儲系統。在XCSVLXS0內部實現的高速狀態機和相位延遲時鐘作用下,采用4片高速A/D器件流水工作來提高數據采集速度。同時在

2018-12-10 16:47:01 22

22 高速雷達數據采集系統的設計方法。該系統由FPGA芯片完成各芯片之間的邏輯控制,具有設計靈活、結構簡單、實時性高、可靠性高等優點。

2018-12-24 15:20:00 21

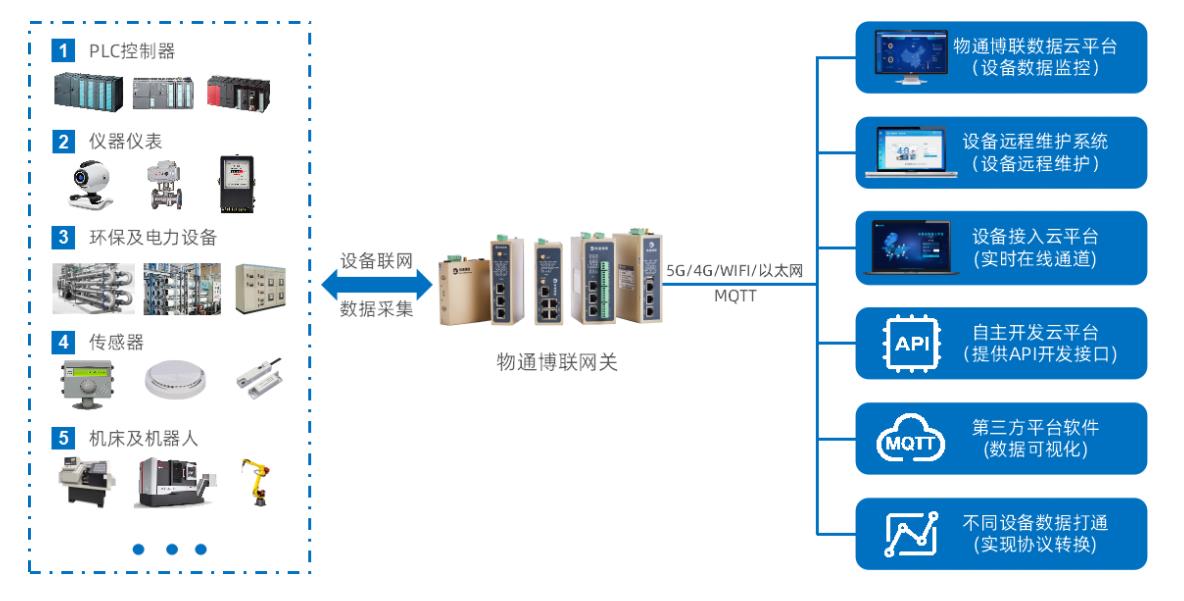

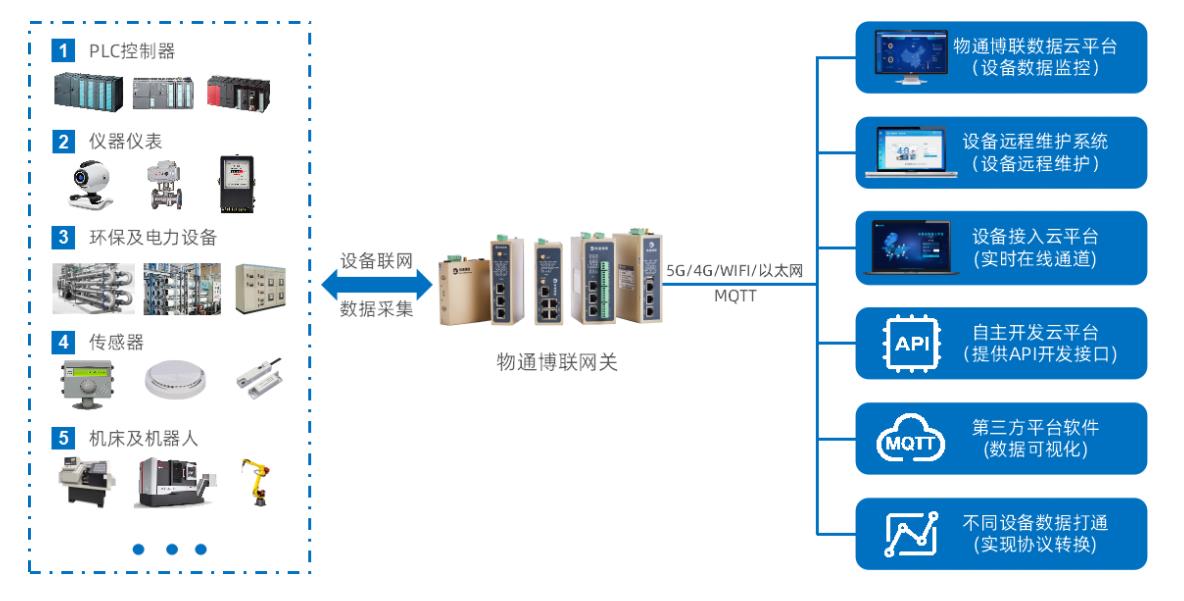

21 數據采集傳輸對于后續企業進行分析和決策是十分重要的,而實時數據采集更能提升整體生產的認識度,從而采取到更加及時高效的措施。因此PLC實時數據采集成為企業的基礎應用,那么如何實現PLC的實時數據采集呢?

2022-11-24 11:09:38 2968

2968 數據采集傳輸對于后續企業進行分析和決策是十分重要的,而實時數據采集更能提升整體生產的認識度,從而采取到更加及時高效的措施。因此PLC實時數據采集成為企業的基礎應用,那么PLC如何實現的實時數據采集呢?

2022-12-08 10:31:29 2067

2067 數據采集傳輸對于后續企業進行分析和決策是十分重要的,而實時數據采集更能提升整體生產的認識度,從而采取到更加及時高效的措施。因此PLC實時數據采集成為企業的基礎應用,那么PLC如何實現的實時數據采集呢?

2023-07-19 11:29:55 1627

1627 為了滿足某大型旋轉機械設備在監測過程中實時性高精度多通道的采集需求,提出了一種基于FPGA的多通道振動信號采集檢測系統的設計方案。系統采用主/從式FPGA架構,在強噪聲環境下實現了采樣頻率為100

2023-08-08 09:25:56 2098

2098

點擊上方 藍字 關注我們 目前,在數據采集系統的硬件設計方案中,有采用通用單片機和USB相結合的方案,也有采用DSP和USB相結合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數據采集系統

2023-10-06 14:55:02 2956

2956

電子發燒友網站提供《嵌入式實時數據采集系統的設計與實現.pdf》資料免費下載

2023-10-24 10:41:22 0

0 某包裝印刷企業為提升生產精度、優化生產流程、降低人工運維成本,推進智能化工廠建設,需對車間多臺高速分切機實現實時數據采集、遠程監控與集中管理。 現場高速分切機涵蓋不同品牌、不同使用年限的設備,部分

2025-11-06 15:41:51 319

319

電子發燒友App

電子發燒友App

評論