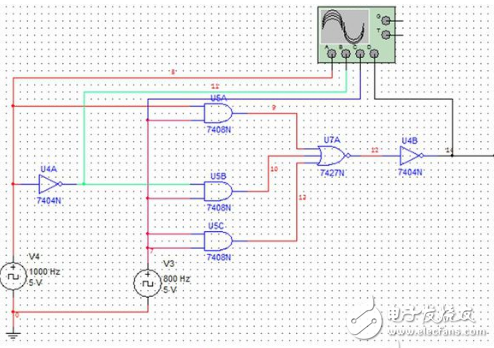

分析組合邏輯電路的目的是,對于一個給定的邏輯電路,確定其邏輯功能。

2020-08-04 15:50:00 37816

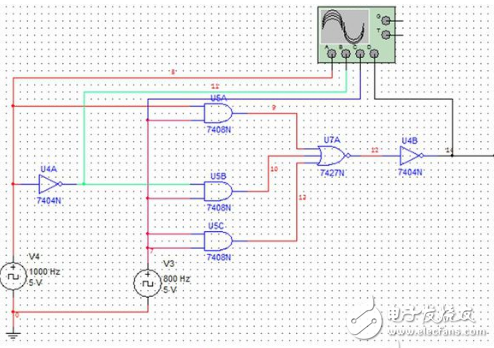

37816 組合電路是最常見的邏輯電路,可以用一些常用的門電路來組合成具有其它功能的門電路。

2023-10-11 17:49:49 26712

26712

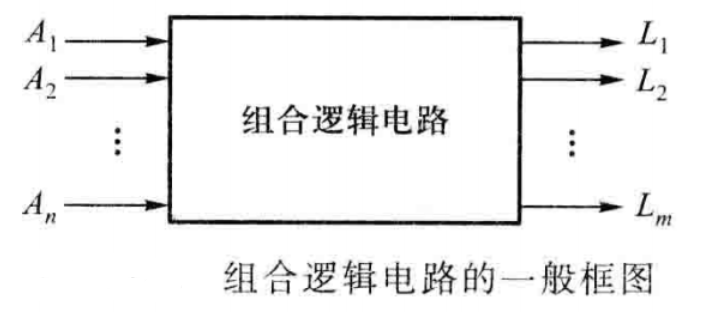

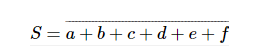

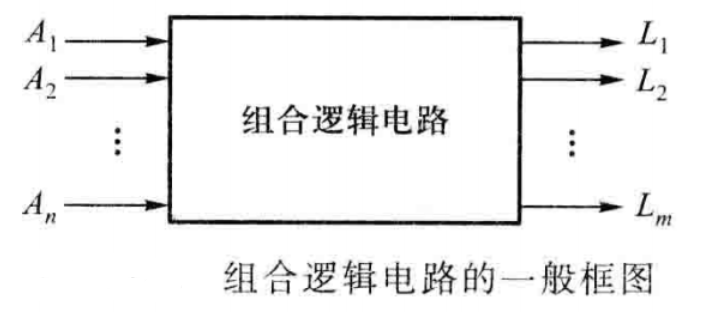

對于一個邏輯電路,其輸出狀態(tài)在任何時刻只取決于同一時刻的輸入狀態(tài),而與電路原來的狀態(tài)無關(guān),這種電路被定義為組合邏輯電路。

2024-02-04 15:33:21 4149

4149

組合邏輯電路PPT電子教案學(xué)習(xí)要點: 組合電路的分析方法和設(shè)計方法 利用數(shù)據(jù)選擇器和譯碼器進(jìn)行邏輯設(shè)計的方法 加法器、編碼器、譯碼器等中

2009-09-16 16:05:29

組合邏輯電路 一、實驗?zāi)康? 1. 加深理解組合邏輯電路

2009-09-16 15:09:13

組合邏輯電路實驗實驗三 組合邏輯電路一、 實驗?zāi)康?、 掌握組合邏輯電路的功能測試2、 驗證半加器和全加器的邏輯功能3、 學(xué)會

2009-03-20 18:11:09

組合邏輯電路是無記憶數(shù)字邏輯電路,其任何時刻的輸出僅取決于其輸入的組合。 與順序邏輯電路不同,順序邏輯電路的輸出取決于它們的當(dāng)前輸入和先前的輸出狀態(tài),從而給它們提供某種形式的存儲器。組合

2020-12-31 17:01:17

組合邏輯電路的分析設(shè)計實驗.ppt

2017-03-21 13:38:58

組合邏輯電路:指任何時刻的輸出僅取決于當(dāng)時刻輸入信號的組合。特點:沒有存儲和記憶作用,沒有反饋回路思維導(dǎo)圖組合邏輯分析根據(jù)已知邏輯電路圖,找出組合邏輯電路的輸入與輸出關(guān)系,確定在什么樣的輸入取值下

2021-07-29 06:35:05

組合邏輯電路的設(shè)計及實驗

2009-10-10 11:44:49

邏輯門及組合邏輯電路實驗實驗?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計和實現(xiàn)方法。4.

2008-09-25 17:28:34

邏輯電路的糾錯技術(shù)是如何實現(xiàn)的?糾錯技術(shù)在邏輯電路中有什么作用?

2021-06-18 09:50:31

微型電子元件,在極小的空間內(nèi)實現(xiàn)了復(fù)雜的邏輯功能。邏輯電路芯片根據(jù)設(shè)計不同,可以分為組合邏輯電路和時序邏輯電路兩大類。

邏輯電路芯片的應(yīng)用幾乎涵蓋了所有電子設(shè)備,包括但不限于:

計算機硬件:CPU

2024-09-30 10:47:47

本帖最后由 gk320830 于 2015-3-5 08:04 編輯

第三章 組合邏輯電路的分析與設(shè)計 在任何時刻,輸出狀態(tài)只決定于同一時刻各輸入狀態(tài)的組合,而與先前狀態(tài)無關(guān)的邏輯電路稱為

2009-04-07 10:54:26

為什么FPGA可以用來實現(xiàn)組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

Verilog程序模塊的結(jié)構(gòu)是由哪些部分組成的?如何去實現(xiàn)時序邏輯電路和組合邏輯電路的設(shè)計呢?

2021-11-03 06:35:57

與順序邏輯電路不同,順序邏輯電路的輸出取決于它們的當(dāng)前輸入和先前的輸出狀態(tài),給它們提供某種形式的存儲器。組合邏輯電路的輸出僅由其當(dāng)前輸入狀態(tài)的邏輯功能(在任何給定的瞬間)確定為邏輯“ 0”或邏輯

2021-01-19 09:29:30

實驗?zāi)康恼莆粘S?b class="flag-6" style="color: red">組合邏輯電路的 EDA 設(shè)計方法;熟練掌握基于 QuartusII 集成開發(fā)環(huán)境的組合邏輯電路設(shè)計流程;加深對 VerilogHDL 語言的理解;熟練掌握 DE2-115 開發(fā)板

2022-01-12 06:35:59

數(shù)字電子技術(shù)-- 組合邏輯電路[hide][/hide]

2017-05-01 22:20:58

數(shù)字電子電路技術(shù)--組合邏輯電路[hide][/hide]

2017-05-01 21:32:09

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進(jìn)行工作的?

2021-09-18 09:19:42

集成邏輯電路、組合邏輯電路實驗?zāi)康?. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態(tài)門的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計和實現(xiàn)方法

2008-12-11 23:36:32

組合邏輯電路 :

2007-12-20 23:02:07 30

30 基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設(shè)計一、實驗?zāi)康?. 熟悉組合邏輯電路的基本設(shè)計方法;2. 練習(xí)用門電路、譯碼器、數(shù)據(jù)選擇器設(shè)計組合邏輯電路。二、實驗設(shè)備1.

2008-09-12 16:41:23 0

0 組合邏輯電路實驗分析一、實驗?zāi)康?nbsp; 1.掌握組合邏輯電路的分析方法與測試方法; 2.了解組合電路的冒險現(xiàn)象及消除方法; 3.驗證半加器、全加器的邏輯功

2009-07-15 18:35:50 0

0 組合邏輯電路(簡稱組合電路)任意時刻的輸出信號僅取決于該時刻的輸入信號,與信號作用前電路原來的狀態(tài)無關(guān)時序邏輯電路(簡稱時序電路)任意時刻的輸出信號不僅取決

2009-07-15 18:45:58 0

0 組合邏輯電路電子教案:數(shù)字邏輯電路可分為兩大類: 一類叫組合邏輯電路;另一類叫時序邏輯電路。本章首先介紹組合邏輯電路的共同特點和描述方法,然后重點介紹組合邏輯電

2009-09-01 08:58:29 0

0 用Protel 99實現(xiàn)邏輯電路設(shè)計:介紹可鳊程邏輯器件(PLD)應(yīng)用和相應(yīng)軟件的發(fā)展;使用EDA 工具Protel 99的PLD設(shè)計簡單邏輯電路的一般方法。關(guān)鍵詞Protel 99 PLD CUPL語言

眾所周知,

2009-11-01 10:13:34 0

0 組合邏輯電路的分析、設(shè)計和調(diào)試(一)一、實驗?zāi)康?.進(jìn)一步熟悉數(shù)字邏輯實驗箱的使用。2.掌握用SSI(小規(guī)模數(shù)字集成電路)構(gòu)成的組合邏輯電路的分析與設(shè)計方法。

2009-11-19 15:01:53 185

185 電子技術(shù)--組合邏輯電路掌握組合邏輯電路的分析方法與設(shè)計方法掌握利用二進(jìn)制譯碼器和數(shù)據(jù)選擇器進(jìn)行邏輯設(shè)計的方法理解加法器、編碼器、譯碼器等中規(guī)模集成電

2010-04-12 17:52:29 0

0 講述組合邏輯電路設(shè)計基礎(chǔ)

2010-05-06 10:29:15 0

0 數(shù)字邏輯電路設(shè)計課程

數(shù)字邏輯電路的設(shè)計包括兩個方面:基本邏輯功能電路設(shè)計和邏輯電路系統(tǒng)設(shè)計。關(guān)于基本邏輯功能電路設(shè)計一般在《數(shù)字電路技術(shù)基礎(chǔ)

2010-05-24 16:05:50 0

0 數(shù)字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數(shù)字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過去的輸入無關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 2.1 分立元件門電路

2.2 集成邏輯門電路

2.3 組合邏輯電路的分析方法

2.4 組合邏輯電的設(shè)計方法

2010-08-12 17:34:19 117

117 一、實驗?zāi)康恼莆?b class="flag-6" style="color: red">組合邏輯電路的設(shè)計與測試方法

2010-09-21 16:52:20 0

0 基本組合邏輯電路

一、 實驗?zāi)康?⒈ 掌握一般組合邏輯電路的分析和設(shè)計方法。?⒉ 熟悉集成優(yōu)先編碼器的邏輯功能及簡單應(yīng)用。

2008-09-24 22:14:03 2886

2886 SSI組合邏輯電路的實驗分析

一、 實驗?zāi)康?

2009-03-28 09:53:21 12057

12057

組合邏輯電路的分析與設(shè)計-邏輯代數(shù)

在任何時刻,輸出狀態(tài)只決定于同一時刻各輸入狀態(tài)的組合,而與先前狀態(tài)無關(guān)的邏輯電路稱為組合邏輯電路。

2009-04-07 10:07:57 3924

3924

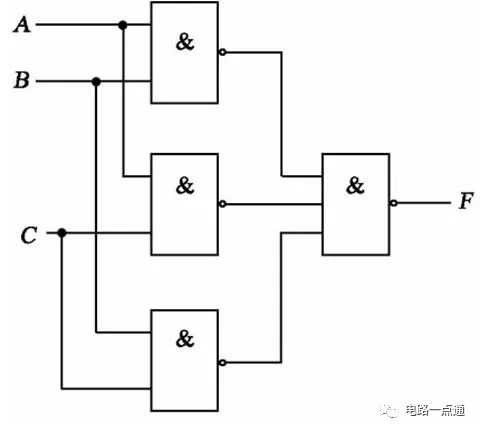

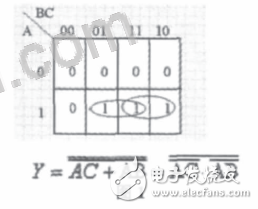

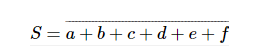

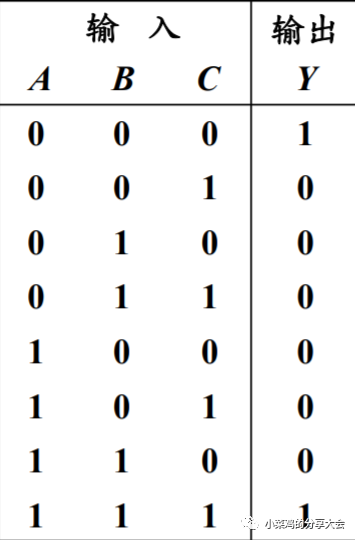

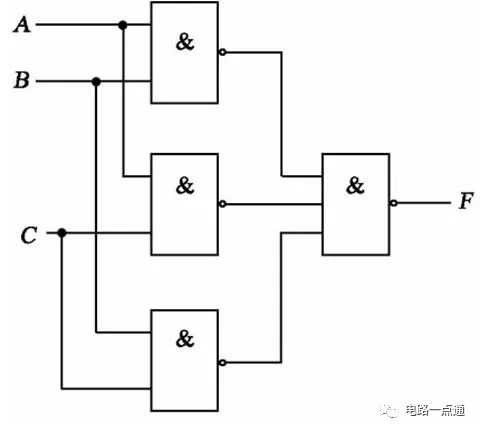

組合邏輯電路的分析

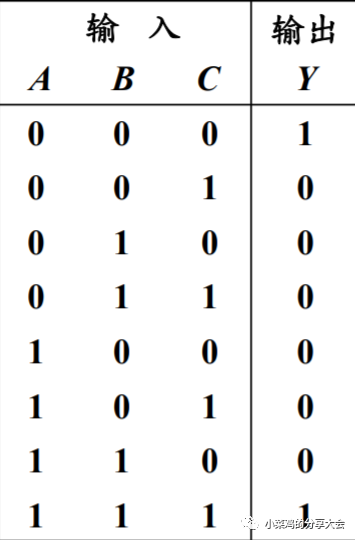

分析組合邏輯電路的目的是為了確定已知電路的邏輯功能,其步驟大致如下: 1.由邏輯圖寫出各輸出端的邏輯表達(dá)式; 2.化簡和變換各

2009-04-07 10:11:55 8346

8346

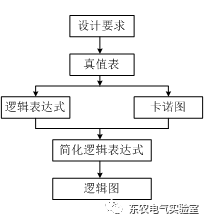

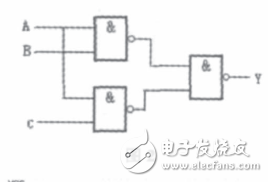

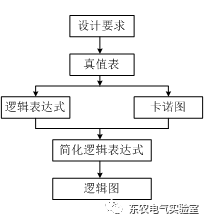

組合邏輯電路的設(shè)計

組合邏輯電路的設(shè)計與分析過程相反,其步驟大致如下: (1)根據(jù)對電路邏輯功能的要求,列出真值表; (2)由真值表寫出邏輯表達(dá)

2009-04-07 10:12:22 14016

14016

組合邏輯電路中的競爭冒險

前面分析組合邏輯電路時,都沒有考慮門電路的延遲時間對電路產(chǎn)生的影響。實際上,從信號輸入到穩(wěn)定輸出需要一定的時間。由于從輸入

2009-04-07 10:13:03 11802

11802

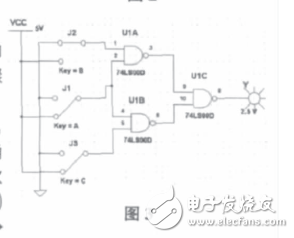

為縮短理論與實踐的距離,提高靈活應(yīng)用數(shù)字元器件的能力,提出了組合邏輯電路設(shè)計的第五步。組合邏輯電路設(shè)計通常有四步,設(shè)計完成畫出符合功能要求的邏輯圖,一般是把其轉(zhuǎn)換

2011-05-03 17:58:26 61

61 基于遺傳算法的組合邏輯電路的自動設(shè)計,依據(jù)給出的真值表,利用遺傳算法自動生成符合要求的組合邏輯電路。由于遺傳算法本身固有的并行性,采用軟件實現(xiàn)的方法在速度上往往受

2012-02-08 11:19:14 32

32 數(shù)字邏輯電路設(shè)計實踐_電工電子實驗中心實驗報告。

2015-10-29 16:25:13 0

0 組合邏輯電路,感興趣的可以下載看看,免費的哦!

2015-10-29 15:08:16 34

34 數(shù)字電路 實驗一 組合邏輯電路的設(shè)計與測試

2015-11-17 18:23:49 2

2 定時控制器邏輯電路設(shè)計定時控制器邏輯電路設(shè)計定時控制器邏輯電路設(shè)計定時控制器邏輯電路設(shè)計定時控制器邏輯電路設(shè)計定時控制器邏輯電路設(shè)計

2015-12-17 18:18:50 0

0 數(shù)字電子鐘邏輯電路設(shè)計,我自己編寫的,里面有橫多實用的東西

2016-06-22 16:12:01 57

57 電子專業(yè)單片機相關(guān)知識學(xué)習(xí)教材資料之組合邏輯電路的分析與設(shè)計

2016-09-02 14:30:26 0

0 數(shù)字電子技術(shù)--組合邏輯電路

2016-12-12 22:07:22 0

0 數(shù)字電子技術(shù)-- 組合邏輯電路

2016-12-12 22:07:22 0

0 組合邏輯電路的分析設(shè)計實驗

2016-12-29 19:00:40 0

0 詳細(xì)介紹了組合邏輯電路的分析方法,包括加法器、譯碼器、編碼器、分配器、選擇器等組合邏輯電路的分析方法

2017-01-22 13:13:01 3

3 1、掌握組合邏輯電路的設(shè)計方法。

2、掌握組合邏輯電路的靜態(tài)測試方法。

3、熟悉CPLD設(shè)計的過程,比較原理圖輸入和文本輸入的優(yōu)劣。

2022-07-10 14:38:36 17

17 邏輯電路按其邏輯功能和結(jié)構(gòu)特點可分為組合邏輯電路和時序邏輯電路。

2017-05-22 15:15:59 77019

77019

數(shù)字電路根據(jù)邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2017-11-29 11:28:01 11216

11216

若一個邏輯電路在任何時刻產(chǎn)生的穩(wěn)定輸出信號僅僅取決于該時刻的輸入信號,而與過去的輸入信號無關(guān),即與輸入信號作用前的電路狀態(tài)無關(guān),則稱該電路為組合邏輯電路。

2018-01-30 16:03:16 53593

53593

數(shù)字電路根據(jù)邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。

2018-01-30 16:24:25 40174

40174

組合邏輯電路的設(shè)計與分析過程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 124121

124121

邏輯電路按其邏輯功能和結(jié)構(gòu)特點可分為組合邏輯電路和時序邏輯電路。單一的與門、或門、與非門、或非門、非門等邏輯門不足以完成復(fù)雜的數(shù)字系統(tǒng)設(shè)計要求。組合邏輯電路是采用兩個或兩個以上基本邏輯門來實現(xiàn)更實用、復(fù)雜的邏輯功能。

2018-01-30 17:05:44 67768

67768

組合邏輯電路和時序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當(dāng)時的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2018-01-30 17:26:04 94951

94951

根據(jù)邏輯功能的不同,可把數(shù)字電路分為組合邏輯電路(Combinational Logic Circuit)和 時序邏輯電路(Sequential Logic Circuit)兩大類。

2018-07-20 08:00:00 0

0 介紹了電子仿真軟件Multisim 在組合邏輯電路設(shè)計的常用元件, 通過設(shè)計一個四變量的樓道路燈控制系統(tǒng)的實例進(jìn)行探討。根據(jù)電路的功能需求得出邏輯表達(dá)式, 在Mu ltis im 中選用與非門搭建

2018-09-21 16:40:15 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路基礎(chǔ)之組合邏輯電路的詳細(xì)資料概述包括了:1.組合邏輯電路的特點2.組合邏輯電路的分析與設(shè)計方法3.常用組合邏輯電路的工作原理及其應(yīng)用 4.加法器、比較器、譯碼器、編碼器、選擇器5.組合邏輯電路中的競爭和冒險現(xiàn)象。

2018-10-17 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路教程之組合邏輯電路課件詳細(xì)資料免費下載主要內(nèi)容包括了:一 概述 二 組合邏輯電路的分析和設(shè)計方法 三 若干常用的組合邏輯電路 四 組合邏輯電路中的競爭冒險

2018-12-28 08:00:00 15

15 組合邏輯電路是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關(guān)。而時序邏輯電路不僅僅取決于當(dāng)前的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關(guān)。

2019-02-26 15:32:30 67228

67228 數(shù)字電路根據(jù)邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 8978

8978

組合邏輯電路是無記憶數(shù)字邏輯電路,其任何時刻的輸出僅取決于其輸入的組合.

2019-06-22 10:53:20 50947

50947

本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路的學(xué)習(xí)教程課件免費下載包括了:1 數(shù)字電路概述,2 邏輯門電路,3 邏輯函數(shù)及其化簡,4 組合邏輯電路的分析與設(shè)計,5 組合邏輯部件

2019-10-11 16:47:00 15

15 組合邏輯電路的設(shè)計的實例引入到EDA中,進(jìn)一步將電子設(shè)計自動化EDA(Electronic Design Automation)應(yīng)用于數(shù)字電子技術(shù)教學(xué)中,而Multisim9軟件是一個專門用于電子線路仿真與設(shè)計的EDA工具軟件,為該課程的教學(xué)和學(xué)習(xí)打下一個良好的基礎(chǔ)。

2020-01-21 16:46:00 3470

3470

邏輯電路在任何時刻產(chǎn)生的穩(wěn)定的輸出信號僅僅取決于該時刻的輸入信號,而與過去的輸入信號無關(guān),即與輸入信號作用前的狀態(tài)無關(guān),這樣的電路稱為組合邏輯電路。

2020-08-08 10:40:00 6454

6454

本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路和時序邏輯電路的學(xué)習(xí)課件免費下載包括了:任務(wù)一 組合邏輯電路,任務(wù)二 編碼器,任務(wù)三 譯碼器,任務(wù)四 集成觸發(fā)器,任務(wù)五 寄存器,任務(wù)六 計數(shù)器。

2020-10-27 15:58:24 31

31 從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 2279

2279 組合邏輯電路的特點是輸入的變化直接反映了輸出的變化,其輸出的狀態(tài)僅取決于輸入的當(dāng)前狀態(tài),與輸入、輸出的原始狀態(tài)無關(guān)。如果從電路結(jié)構(gòu)上來講,組合邏輯電路是沒有觸發(fā)器組件的電路。

2022-10-24 16:02:32 1770

1770 避免常見的邏輯電路設(shè)計問題

2022-11-04 09:50:16 0

0 組合邏輯電路:用各種門電路組成的,用于實現(xiàn)某種功能的復(fù)雜邏輯電路。特點:某一時刻的輸出狀態(tài)僅由該時刻電路的輸入信號決定, 而與該電路在此輸入信號之前所具有的狀態(tài)無關(guān)。

2022-12-05 14:52:54 9

9 本文介紹開發(fā)組合邏輯電路時可能發(fā)生的意外開關(guān)事件,稱為危險。 本文是關(guān)于使用邏輯門進(jìn)行組合電路設(shè)計和仿真的介紹性系列文章的第二部分。在上一篇文章中,我們介紹了 組合邏輯電路 以及如何簡化它們

2023-01-27 14:18:00 2709

2709

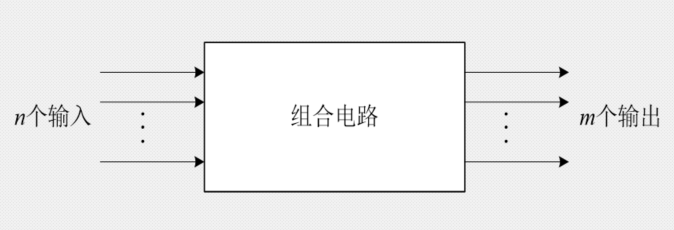

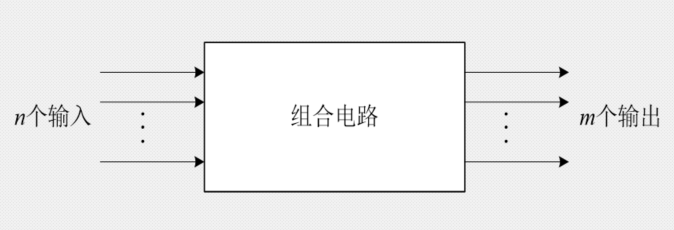

邏輯功能的門級實現(xiàn)受門扇入的限制。本文探討了邏輯分解、分組和電平增加,以在有限的輸入門下實現(xiàn)邏輯功能。 了解如何利用 組合邏輯功能 并簡化組合邏輯電路!為了理解與這些過程相關(guān)的挑戰(zhàn),讓我們首先建立一

2023-01-27 14:24:00 1912

1912

數(shù)字電路中的組合邏輯電路的設(shè)計與分析過程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計步驟,順便回顧一下組合邏輯電路的分析方法。

2023-02-03 09:56:23 8000

8000 所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-03-06 14:37:26 5873

5873 數(shù)字電路根據(jù)邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 8731

8731

組合邏輯電路: 電路在任一時刻的輸出狀態(tài)僅由該時刻的輸入信號決定,與電路在此信號輸入之前的狀態(tài)無關(guān)。

2023-03-21 11:57:00 5098

5098

本篇內(nèi)容主要回顧第三章組合邏輯電路的知識,雖然前面提到過組合邏輯電路是數(shù)字電路中很重要的一部分,但是學(xué)習(xí)起來相對簡單,主要是要學(xué)會掌握方法。

2023-05-24 14:38:59 3096

3096

所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-08-16 09:15:23 11276

11276

電子發(fā)燒友網(wǎng)站提供《組合邏輯電路電子課件.ppt》資料免費下載

2023-11-21 14:25:23 0

0 當(dāng)邏輯電路由多個邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合邏輯電路。

2024-02-04 11:46:36 3338

3338

組合邏輯電路和時序邏輯電路是數(shù)字電路中兩種重要的邏輯電路類型,它們主要區(qū)別在于其輸出信號的依賴關(guān)系和對時間的敏感性。

2024-02-04 16:00:27 7171

7171 時序邏輯電路是一種能夠存儲信息并根據(jù)時鐘信號按照特定順序執(zhí)行操作的電路。它是計算機硬件中非常重要的一部分,用于實現(xiàn)存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據(jù)輸入信號的組合情況,立即

2024-02-06 11:18:34 13635

13635 什么是組合邏輯電路和時序邏輯電路?時序邏輯電路和組合邏輯電路的區(qū)別是什么? 組合邏輯電路和時序邏輯電路是數(shù)字電路中兩種基本類型的電路設(shè)計。 組合邏輯電路是由邏輯門組成的,邏輯門的輸出僅由它的當(dāng)前輸入

2024-03-26 16:12:14 6632

6632 一、引言 組合邏輯電路是數(shù)字電路中的重要組成部分,它僅由邏輯門電路(如與門、或門、非門等)和輸入/輸出端組成,不包含任何存儲元件。組合邏輯電路的輸出僅取決于當(dāng)前的輸入信號,與電路的歷史狀態(tài)無關(guān)。因此

2024-07-30 14:38:04 3067

3067 和可靠性。 需求分析 需求分析是設(shè)計組合邏輯電路的第一步,也是最重要的一步。在這個階段,我們需要明確電路的功能、輸入輸出信號、性能要求等。需求分析的目的是確保電路設(shè)計滿足實際應(yīng)用的需求。 1.1 功能定義 功能定義是

2024-07-30 14:39:55 2312

2312 組合邏輯電路是數(shù)字邏輯電路的一種,其特點是輸出只依賴于當(dāng)前的輸入狀態(tài),而與輸入信號的變化歷史無關(guān)。組合邏輯電路廣泛應(yīng)用于數(shù)字系統(tǒng)中,如計算機、通信設(shè)備、控制設(shè)備等。以下是對常用的組合邏輯電路的介紹

2024-07-30 14:41:37 4788

4788 組合邏輯電路是一種基本的數(shù)字電路,它由邏輯門組成,用于實現(xiàn)各種邏輯功能。組合邏輯電路的結(jié)構(gòu)特點主要包括以下幾個方面: 無記憶功能 :組合邏輯電路的輸出僅取決于當(dāng)前的輸入狀態(tài),與過去的狀態(tài)無關(guān)。這與

2024-08-11 11:14:59 2617

2617 一、引言 組合邏輯電路是數(shù)字電路中的一種基本類型,它由邏輯門、觸發(fā)器等基本元件組成,通過邏輯門的組合實現(xiàn)特定的邏輯功能。組合邏輯電路廣泛應(yīng)用于計算機、通信、控制等領(lǐng)域。在設(shè)計組合邏輯電路時,需要遵循

2024-08-11 11:26:04 2603

2603 組合邏輯電路設(shè)計的關(guān)鍵步驟主要包括以下幾個方面: 1. 邏輯抽象 任務(wù) :根據(jù)實際邏輯問題的因果關(guān)系,確定輸入、輸出變量,并定義邏輯狀態(tài)的含義。 內(nèi)容 :明確問題的邏輯要求,找出自變量(輸入條

2024-08-11 11:28:18 2609

2609

電子發(fā)燒友App

電子發(fā)燒友App

評論