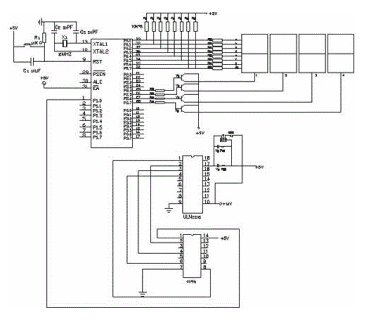

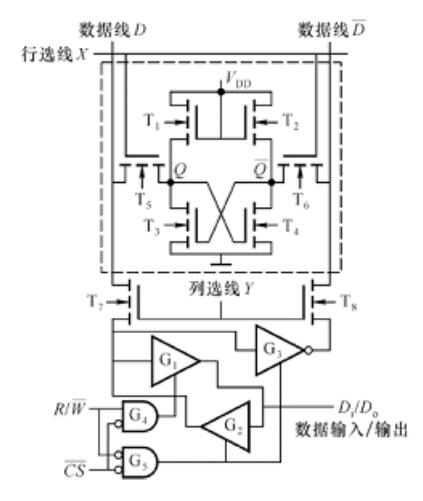

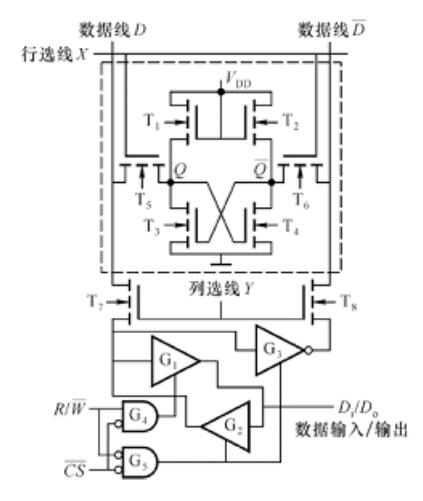

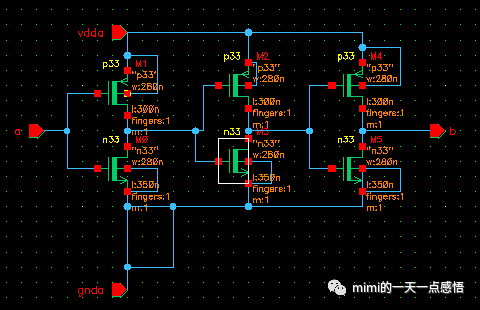

存儲(chǔ)單元采用圖2(a)所示的8管雙端口結(jié)構(gòu),每個(gè)端口對(duì)應(yīng)一條的字線和一對(duì)位線。當(dāng)字線電位拉高時(shí),對(duì)應(yīng)的兩個(gè)NMOS管打開(kāi),數(shù)據(jù)通過(guò)位線寫(xiě)入或者讀出。作為ROM使用時(shí),為了實(shí)現(xiàn)對(duì)存儲(chǔ)單元的初始化,必須

2020-07-22 16:30:40 1732

1732

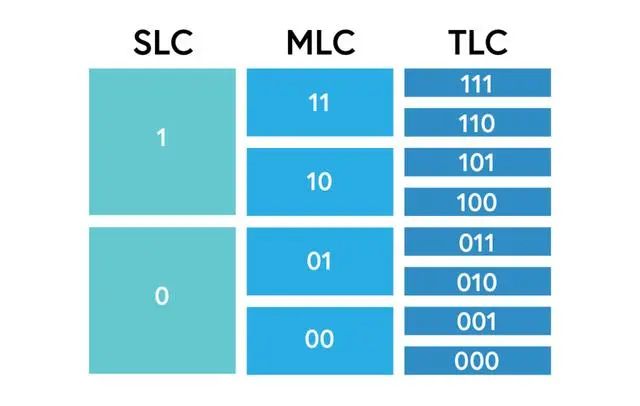

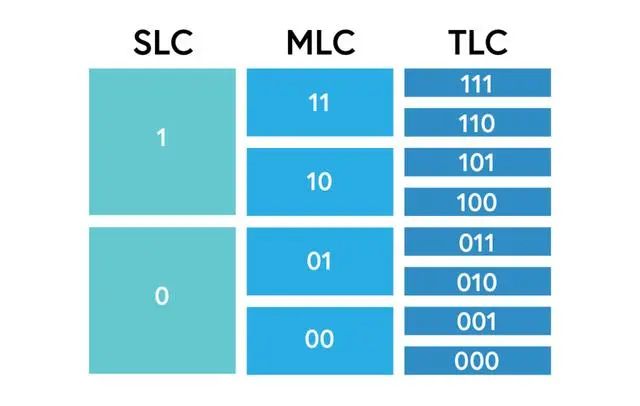

就基本的 SSD 存儲(chǔ)單元而言,有 SLC、MLC、TLC 和 QLC。其中,TLC 是最受歡迎的,不過(guò),QLC 最終將取代它們。在 I/O 方面,有 SATA 和 NVMe。

2022-08-26 16:41:35 4862

4862

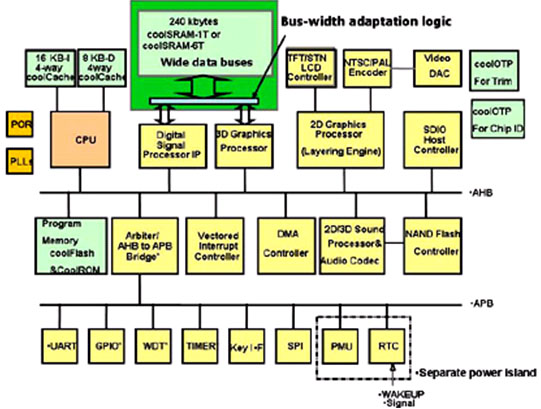

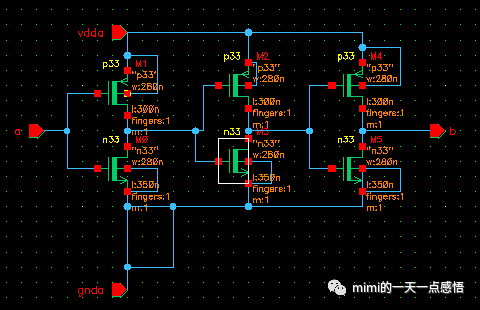

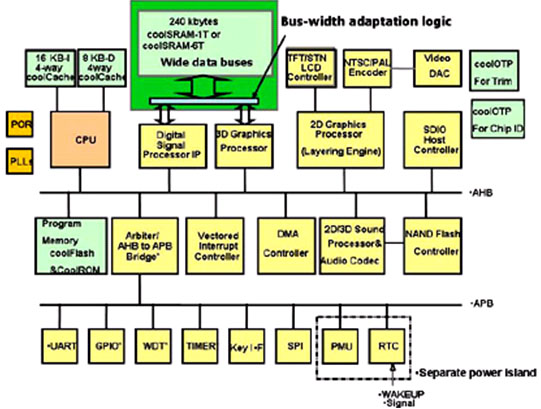

在芯片設(shè)計(jì)時(shí),通常需要用到各種類(lèi)型的存儲(chǔ)單元,用以臨時(shí)或者永久地存儲(chǔ)數(shù)據(jù)。根據(jù)應(yīng)用場(chǎng)合的不同,所用到的存儲(chǔ)單元也不同。本文對(duì)常見(jiàn)的幾個(gè)存儲(chǔ)單元進(jìn)行了介紹,并簡(jiǎn)述了其工作原理和特點(diǎn)。需要特別

2022-12-02 17:36:24 4079

4079

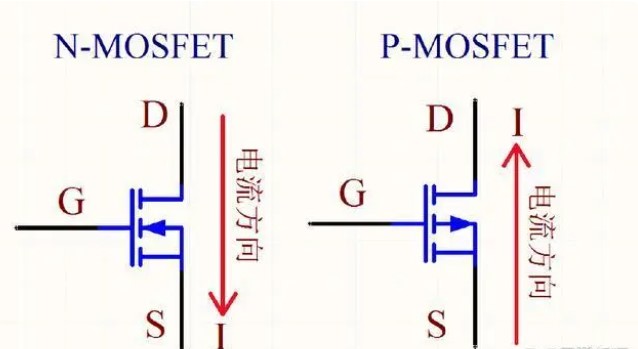

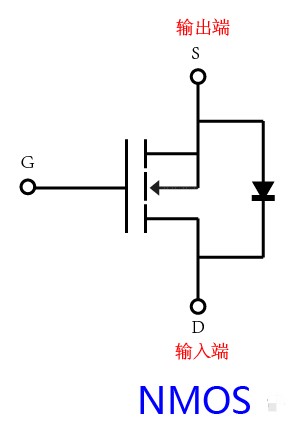

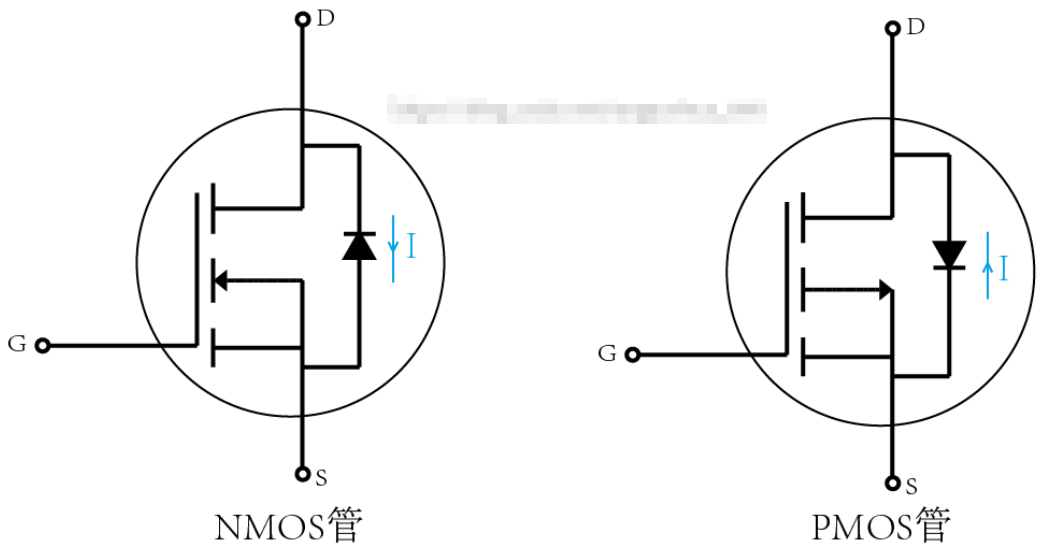

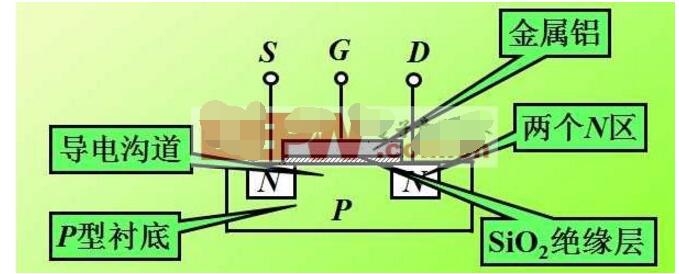

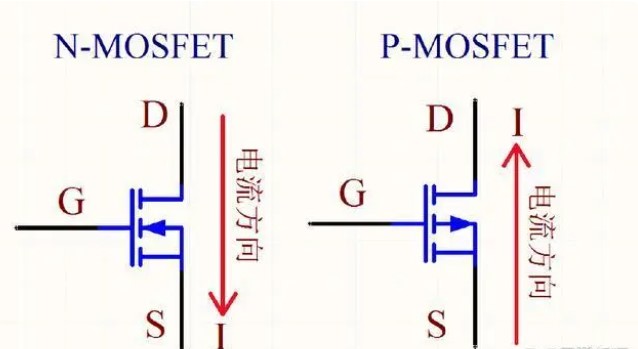

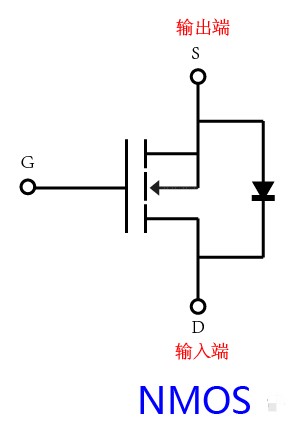

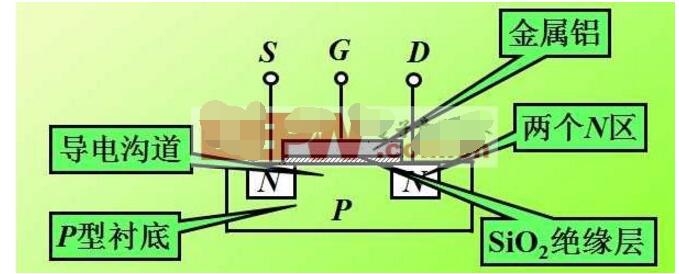

NMOS英文全稱(chēng)為N-Metal-Oxide-Semiconductor。 意思為N型金屬-氧化物-半導(dǎo)體,而擁有這種結(jié)構(gòu)的晶體管我們稱(chēng)之為NMOS晶體管。 MOS晶體管有P型MOS管和N型

2023-02-16 17:00:15 10476

10476

NMOS英文全稱(chēng)為N-Metal-Oxide-Semiconductor。 意思為N型金屬-氧化物-半導(dǎo)體,而擁有這種結(jié)構(gòu)的晶體管我們稱(chēng)之為NMOS晶體管。 MOS晶體管有P型MOS管和N型

2023-02-21 17:23:46 27682

27682

NMOS英文全稱(chēng)為N-Metal-Oxide-Semiconductor。 意思為N型金屬-氧化物-半導(dǎo)體,而擁有這種結(jié)構(gòu)的晶體管我們稱(chēng)之為NMOS晶體管。

2023-02-21 17:35:14 20597

20597

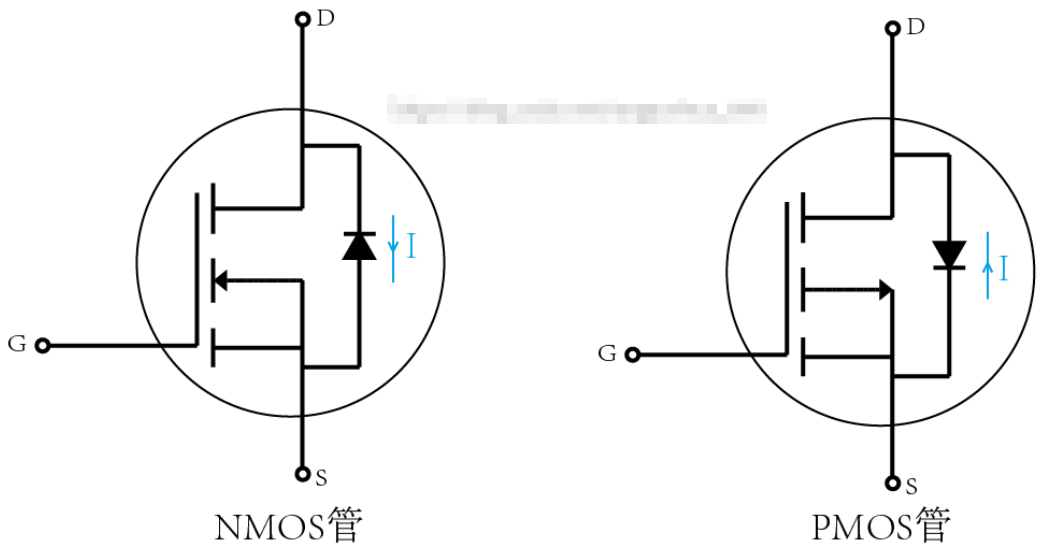

MOS管的管腳有三個(gè):源極S(source)、柵極G(Gate)和漏極(Drain),但是實(shí)際工程應(yīng)用中,經(jīng)常無(wú)法區(qū)分PMOS管和NMOS管、各管腳的位置以及它們各自導(dǎo)通的條件。

2023-02-28 17:08:42 8562

8562

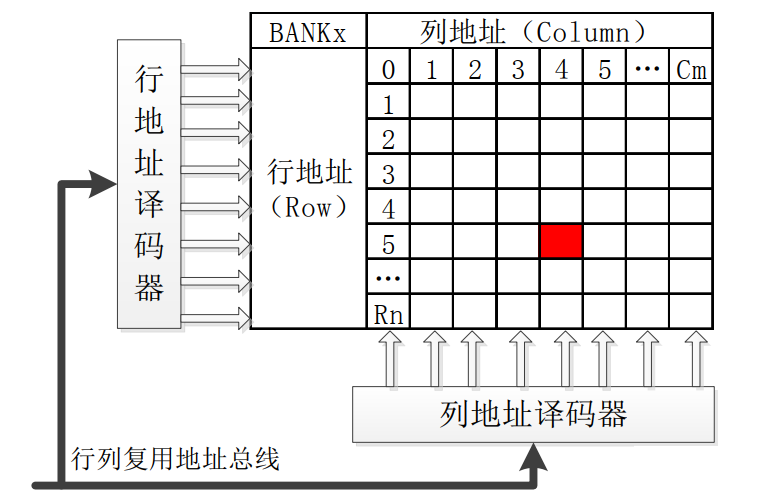

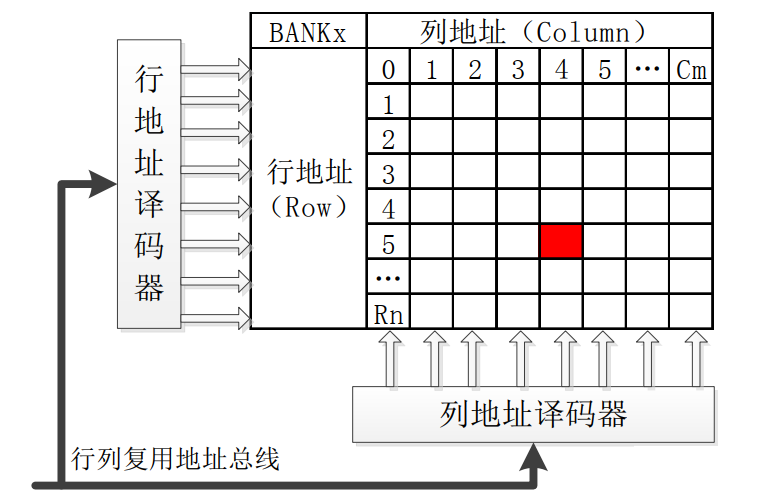

SDRAM英文名是:Synchronous Dynamic Random Access Memory,即同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步指存儲(chǔ)器的工作需要參考時(shí)鐘。

2023-04-04 17:11:32 8006

8006

牛津大學(xué)設(shè)計(jì)了一種新型計(jì)算機(jī)存儲(chǔ)單元,可以同時(shí)通過(guò)電和光信號(hào)對(duì)其進(jìn)行訪問(wèn)或?qū)懭耄蠓忍嵘藥捄凸β市剩策M(jìn)一步推動(dòng)了芯片級(jí)光子學(xué)技術(shù)的發(fā)展。

2020-01-21 08:38:00 1754

1754 80C51單片機(jī)片內(nèi)RAM低128個(gè)存儲(chǔ)單元劃分為哪4個(gè)主要部分?各部分主要功能是什么?

2011-10-08 16:10:02

什么是MOS管?NMOS是什么?PMOS又是什么?NMOS管與PMOS管有哪些不同?

2021-10-15 09:09:38

存儲(chǔ)位元與存儲(chǔ)單元是什么含義?數(shù)據(jù)通信的方式可以分為哪幾種呢?

2022-01-21 07:17:58

設(shè)存儲(chǔ)器讀/寫(xiě)周期為 0.5us, CPU在1us內(nèi)至少要訪問(wèn)一次。試問(wèn)采用哪種刷新方式比較合理? 兩次刷新的最大時(shí)間間隔是多少? 對(duì)全部存儲(chǔ)單元刷新遍所需的實(shí)際刷新時(shí)間是多少?

2021-10-26 07:05:19

理,相比之下在SRAM存儲(chǔ)芯片上一個(gè)bit通常需要六個(gè)晶體管。因此DRAM擁有非常高的密度,單位體積的容量較高因此成本較低。 DRAM存儲(chǔ)原理 DRAM的每一位存儲(chǔ)單元采用一個(gè)晶體管和小電容來(lái)實(shí)現(xiàn)

2020-12-10 15:49:11

1.(判斷題)DRAM上電時(shí)存儲(chǔ)單元的內(nèi)容是全0,而Flash上電時(shí)存儲(chǔ)單元的內(nèi)容是全1。(4分) A.正確B.錯(cuò)誤 FLASH可保存 上電后不知道是啥2.(判斷題)眼圖可以用來(lái)分析高速信號(hào)的碼間

2021-07-22 08:57:49

判斷題:DRAM上電時(shí)存儲(chǔ)單元的內(nèi)容是全0,而Flash上電時(shí)存儲(chǔ)單元的內(nèi)容是全1

2017-08-23 09:29:31

的上升、下降時(shí)序,以及盡可能小的延遲和面積開(kāi)銷(xiāo)。所有的多路選擇器是用面積最小的晶體管來(lái)實(shí)現(xiàn),SRAM單元也是用面積最小的晶體管來(lái)實(shí)現(xiàn),布線開(kāi)關(guān)的晶體管在面積和延遲方面做了平衡。所有基本單元中的NMOS

2020-04-28 08:00:00

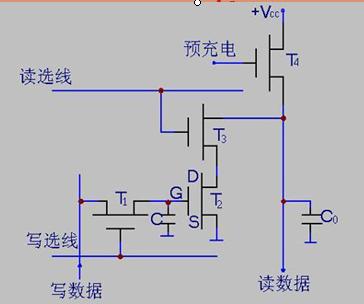

方式邊界對(duì)齊的數(shù)據(jù)存放方法主存的基本結(jié)構(gòu)和工作過(guò)程存儲(chǔ)系統(tǒng)的層次結(jié)構(gòu)半導(dǎo)體存儲(chǔ)器靜態(tài)MOS存儲(chǔ)器 SRAM靜態(tài)MOS存儲(chǔ)單元靜態(tài)MOS存儲(chǔ)器的結(jié)構(gòu)動(dòng)態(tài)MOS存儲(chǔ)器 DRAM四管動(dòng)態(tài)MOS存儲(chǔ)元的工作原理

2021-07-28 07:59:20

Nand Flash的物理存儲(chǔ)單元的陣列組織結(jié)構(gòu)Nand flash的內(nèi)部組織結(jié)構(gòu),此處還是用圖來(lái)解釋?zhuān)容^容易理解:圖2.Nand Flash物理存儲(chǔ)單元的陣列組織結(jié)構(gòu)[url=][img=1,0

2018-06-12 10:10:18

請(qǐng)教Arm專(zhuān)家大俠: SOC內(nèi)SRAM各存儲(chǔ)單元, 其“每次上電冷啟動(dòng)后、還未寫(xiě)入應(yīng)用數(shù)據(jù)前的初始狀態(tài)數(shù)據(jù)”是否是由其硬件電路保證總是一樣的(全0或全1)?不會(huì)隨機(jī)變化(有時(shí)為0有時(shí)為1)? 能否從硬件原理角度簡(jiǎn)單說(shuō)明下? 謝謝。

2022-08-19 15:37:40

SRAM 即靜態(tài)RAM.它也由晶體管組成,SRAM的高速和靜態(tài)特性使它們通常被用來(lái)作為Cache存儲(chǔ)器。計(jì)算機(jī)的主板上都有Cache插座。下圖所示的是一個(gè)SRAM的結(jié)構(gòu)框圖。由上圖看出SRAM一般由

2022-11-17 14:47:55

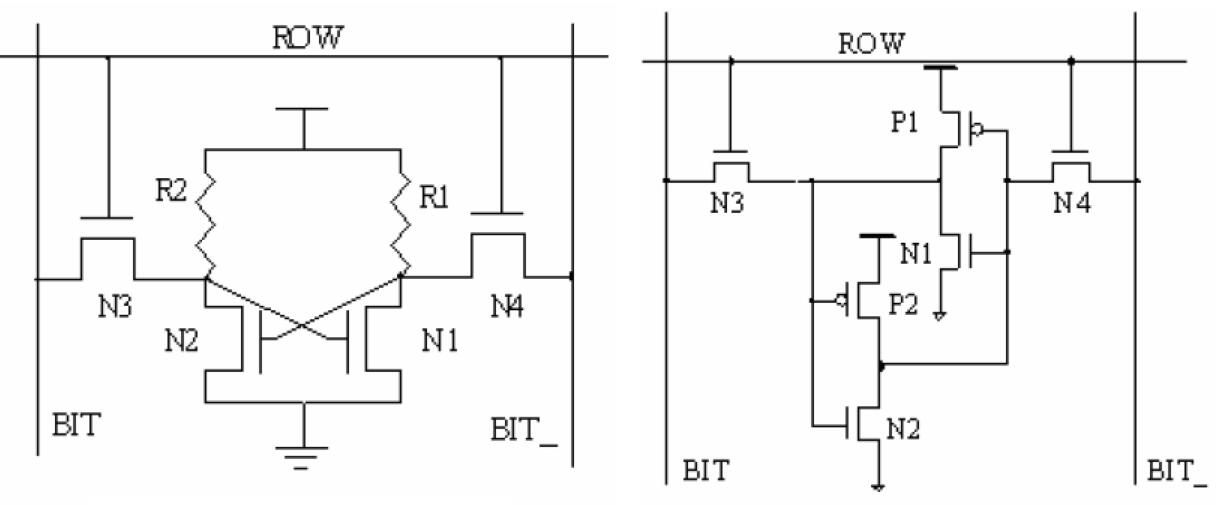

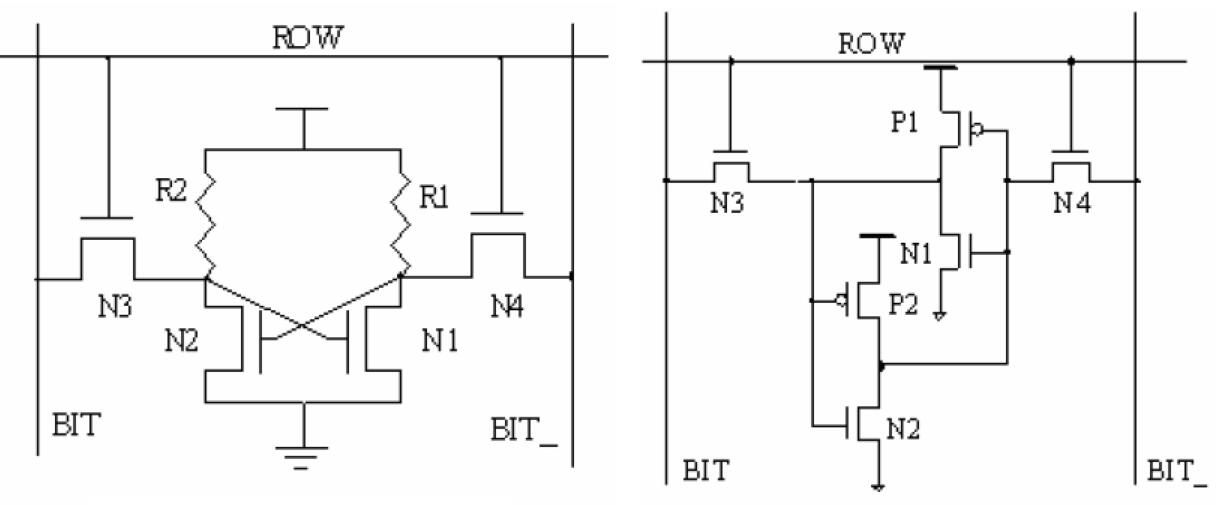

靜態(tài)RAM的基本構(gòu)造塊是SRAM存儲(chǔ)單元。通過(guò)升高字線的電平觸發(fā)存儲(chǔ)單元,再通過(guò)位線對(duì)所觸發(fā)的存儲(chǔ)單元進(jìn)行讀出或?qū)懭搿T?b class="flag-6" style="color: red">靜態(tài)CMOS存儲(chǔ)器中,存儲(chǔ)單元陣列將會(huì)占去整個(gè)存儲(chǔ)器芯片面積的一半以上,在一些

2020-06-05 15:18:24

niosii編譯提示on-chip menmory 存儲(chǔ)單元不夠,怎么解決?

2015-01-18 09:31:43

的多少,即電容端電壓的高低來(lái)表示“1”和“0”。DRAM每個(gè)存儲(chǔ)單元所需的場(chǎng)效應(yīng)管較少,常見(jiàn)的有4管,3管和單管型DRAM。因此它的集成度較高,功耗也較低,但缺點(diǎn)是保存在DRAM中的信息__場(chǎng)效應(yīng)管柵極

2011-11-28 10:23:57

主存中存儲(chǔ)單元地址是如何進(jìn)行分配的?存儲(chǔ)芯片的容量有多大?

2021-10-19 08:25:52

4.2.1.主存中存儲(chǔ)單元地址的分配:存儲(chǔ)字長(zhǎng):存儲(chǔ)器中一個(gè)存儲(chǔ)單元(存儲(chǔ)地址)所存儲(chǔ)的二進(jìn)制代碼的位數(shù),即存儲(chǔ)器中的MDR的位數(shù)。字(word) : 若干個(gè)字節(jié)組成一一個(gè)”字” ( word)。一

2021-07-28 06:43:06

的通路,稱(chēng)為位線。每一個(gè)存儲(chǔ)單元都能通過(guò)選擇適當(dāng)?shù)淖志€和位線被唯一地定位。宇芯有限公司介紹關(guān)于SRAM存儲(chǔ)器的讀操作分析。 圖1 六管單元的讀出操作 SRAM存儲(chǔ)單元讀操作分析存儲(chǔ)單元的讀操作是指被

2020-04-29 17:27:30

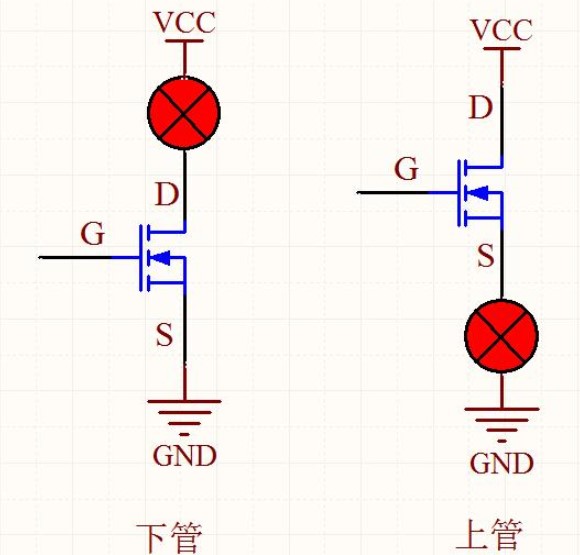

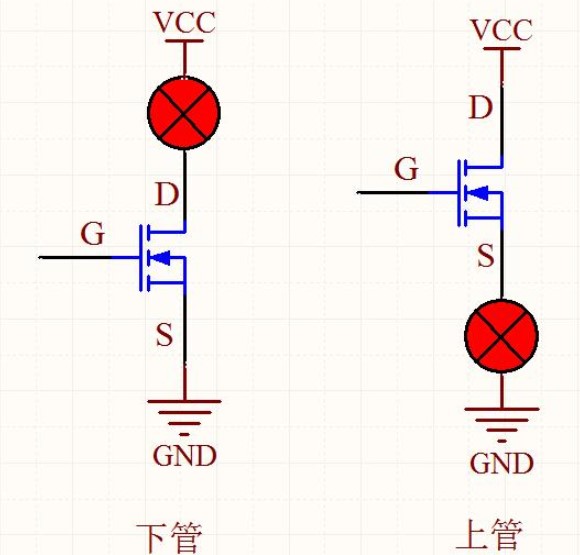

1 MOS管導(dǎo)通截止原理NMOS管的主回路電流方向?yàn)镈—>S,導(dǎo)通條件為VGS有一定的壓差,如 5V(G電位比S電位高)。PMOS管的主回路電流方向?yàn)镾—>D,導(dǎo)通條件為

2023-02-17 13:58:02

、無(wú)負(fù)載型和六管 CMOS 單元等。電阻負(fù)載型存儲(chǔ)單元由于電其壓傳輸特性曲線(VTC)不陡并且功耗大已遠(yuǎn)離了主流設(shè)計(jì);無(wú)負(fù)載型存儲(chǔ)單元雖然可以實(shí)現(xiàn)較高的密度[16],但其穩(wěn)定性差;六管 CMOS

2020-07-09 14:38:57

存儲(chǔ)單元”是構(gòu)成“靜態(tài)存儲(chǔ)器”(SRAM)的最基本單元。其中每一個(gè)BIT存儲(chǔ)在4個(gè)晶體管構(gòu)成的2個(gè)交叉耦合的反相器中。而另外2個(gè)晶體管作為“寫(xiě)控制電路”的控制開(kāi)關(guān)。 有趣的是,搭建這個(gè)電路需要嚴(yán)格對(duì)稱(chēng)

2017-01-08 12:11:06

在分析傳統(tǒng)SRAM存儲(chǔ)單元工作原理的基礎(chǔ)上,采用VTC蝴蝶曲線,字線電壓驅(qū)動(dòng),位線電壓驅(qū)動(dòng)和N曲線方法衡量了其靜態(tài)噪聲容限。 在這種背景下,分析研究了前人提出的多種單元優(yōu)化方法。這些設(shè)計(jì)方法,大部分

2020-04-01 14:32:04

你好如何在不使用DDR內(nèi)存控制器的情況下設(shè)計(jì)FPGA BRAM(或任何其他內(nèi)存模塊_SD,DDR以外的本地等)大容量存儲(chǔ)單元?當(dāng)我通過(guò)示例設(shè)計(jì)“VC707_bist”替換DRAM控制器和BRAM

2019-04-04 15:10:55

基于傳統(tǒng)六晶體管(6T)存儲(chǔ)單元的靜態(tài)RAM存儲(chǔ)器塊一直是許多嵌入式設(shè)計(jì)中使用ASIC/SoC實(shí)現(xiàn)的開(kāi)發(fā)人員所采用的利器,因?yàn)檫@種存儲(chǔ)器結(jié)構(gòu)非常適合主流的CMOS工藝流程,不需要增添任何額外的工藝步驟。那么究竟怎么樣,才能實(shí)現(xiàn)嵌入式ASIC和SoC的存儲(chǔ)器設(shè)計(jì)呢?

2019-08-02 06:49:22

怎么把單片機(jī)存儲(chǔ)單元清0或置1?

2023-10-16 07:59:42

怎么隨機(jī)存取存儲(chǔ)器ram中的存儲(chǔ)單元

2023-09-28 06:17:04

靜態(tài)存儲(chǔ)單元和其讀寫(xiě)控制電路組成的記憶體電路,對(duì)此的詳細(xì)內(nèi)容在四個(gè)晶體管搭建靜態(tài)存儲(chǔ)單元,加兩個(gè)晶體管搭建寫(xiě)控制電路一文中。LY62L5128是一個(gè)CMOS SRAM。容量512KB(512K X 8

2016-08-30 04:32:10

模式也使得DRAM的集成度高于SRAM,一個(gè)DRAM的存儲(chǔ)單元僅需要一個(gè)晶體管和一個(gè)小電容,而每個(gè)SRAM單元需要四道六個(gè)晶體管和其它的零件,故DRAM在大容量以及價(jià)格上會(huì)有優(yōu)勢(shì)。 FlashFLASH

2019-09-18 09:05:09

基于傳統(tǒng)六晶體管(6T)存儲(chǔ)單元的靜態(tài)RAM 存儲(chǔ)器塊一直是許多嵌入式設(shè)計(jì)中使用ASIC/SoC 實(shí)現(xiàn)的開(kāi)發(fā)人員所采用的利器,因?yàn)檫@種存儲(chǔ)器結(jié)構(gòu)非常適合主流的CMOS工藝流程,不需要

2009-11-30 16:06:41 18

18 對(duì)第一代開(kāi)關(guān)電流存儲(chǔ)單元產(chǎn)生的時(shí)鐘饋通誤差做了合理的近似分析,設(shè)計(jì)了一種高性能開(kāi)關(guān)電流存儲(chǔ)單元。該電路僅在原存儲(chǔ)單元的基礎(chǔ)上增加了一個(gè)MOS管,使誤差降為原來(lái)的4%,

2010-07-05 14:50:48 22

22 存儲(chǔ)器的分類(lèi)

內(nèi)部存儲(chǔ)器的系統(tǒng)結(jié)構(gòu)

動(dòng)、靜態(tài)讀寫(xiě)存儲(chǔ)器RAM的基本存儲(chǔ)單元與芯片

2010-11-11 15:35:22 67

67 低電壓甲乙類(lèi)開(kāi)關(guān)電流存儲(chǔ)單元

引言 開(kāi)關(guān)電流存儲(chǔ)單元是電流模式采樣數(shù)據(jù)信號(hào)處理系統(tǒng)的基本單元電路,其性能的優(yōu)

2007-08-15 16:06:29 710

710 使用新SRAM工藝實(shí)現(xiàn)嵌入式ASIC和SoC的存儲(chǔ)器設(shè)計(jì)基于傳統(tǒng)六晶體管(6T)存儲(chǔ)單元的靜態(tài)RAM存儲(chǔ)器塊一直是許多嵌入式設(shè)計(jì)中使用ASIC/SoC實(shí)現(xiàn)的開(kāi)發(fā)人員所采用的利器,因

2009-02-01 09:11:51 1746

1746

三態(tài)MOS動(dòng)態(tài)存儲(chǔ)單元電路

2009-10-10 18:45:49 1445

1445

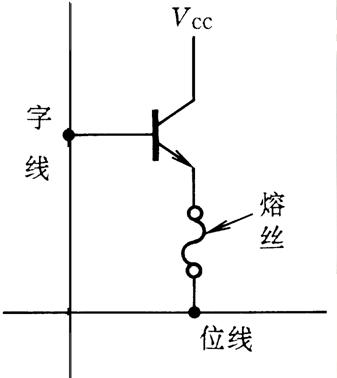

熔絲型PROM的存儲(chǔ)單元

2009-12-04 12:25:26 2492

2492

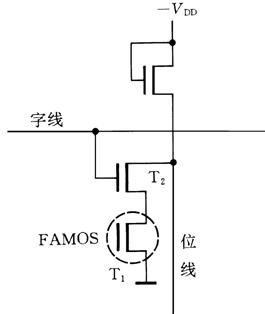

使用FAMOS管的存儲(chǔ)單元

2009-12-04 12:27:29 1016

1016

E2PROM的存儲(chǔ)單元

2009-12-04 13:03:57 1672

1672 E2PROM存儲(chǔ)單元的三種工作狀態(tài)

2009-12-04 13:04:45 1617

1617 四管動(dòng)態(tài)MOS存儲(chǔ)單元

2009-12-04 16:34:14 2641

2641 單管動(dòng)態(tài)MOS存儲(chǔ)單元

2009-12-04 16:50:24 4158

4158 NMOS管的開(kāi)關(guān)特性,基礎(chǔ)的模擬電路,很好的資料

2016-01-13 14:47:03 0

0 靜態(tài)數(shù)碼管靜態(tài)數(shù)碼管靜態(tài)數(shù)碼管靜態(tài)數(shù)碼管

2016-05-13 15:39:49 6

6 應(yīng)用于超低電壓下的SRAM存儲(chǔ)單元設(shè)計(jì)_劉冰燕

2017-01-07 21:39:44 0

0 使用賽道存儲(chǔ)單元的近閾值非易失SRAM_孫憶南

2017-01-07 21:45:57 1

1 。O工P存儲(chǔ)器的種類(lèi)很多,很多是基于熔絲和反熔絲,本文介紹的O工P存儲(chǔ)器基于反熔絲結(jié)構(gòu)。在反熔絲O工P存儲(chǔ)器中,通過(guò)對(duì)選中單元的編程改變了存儲(chǔ)單元內(nèi)部的結(jié)構(gòu)。理想的讀機(jī)制下,沒(méi)有編程的存儲(chǔ)單元讀取時(shí)會(huì)讀出0,而通過(guò)編程的存儲(chǔ)單元在讀取時(shí)會(huì)讀出1。反

2017-11-07 11:45:21 11

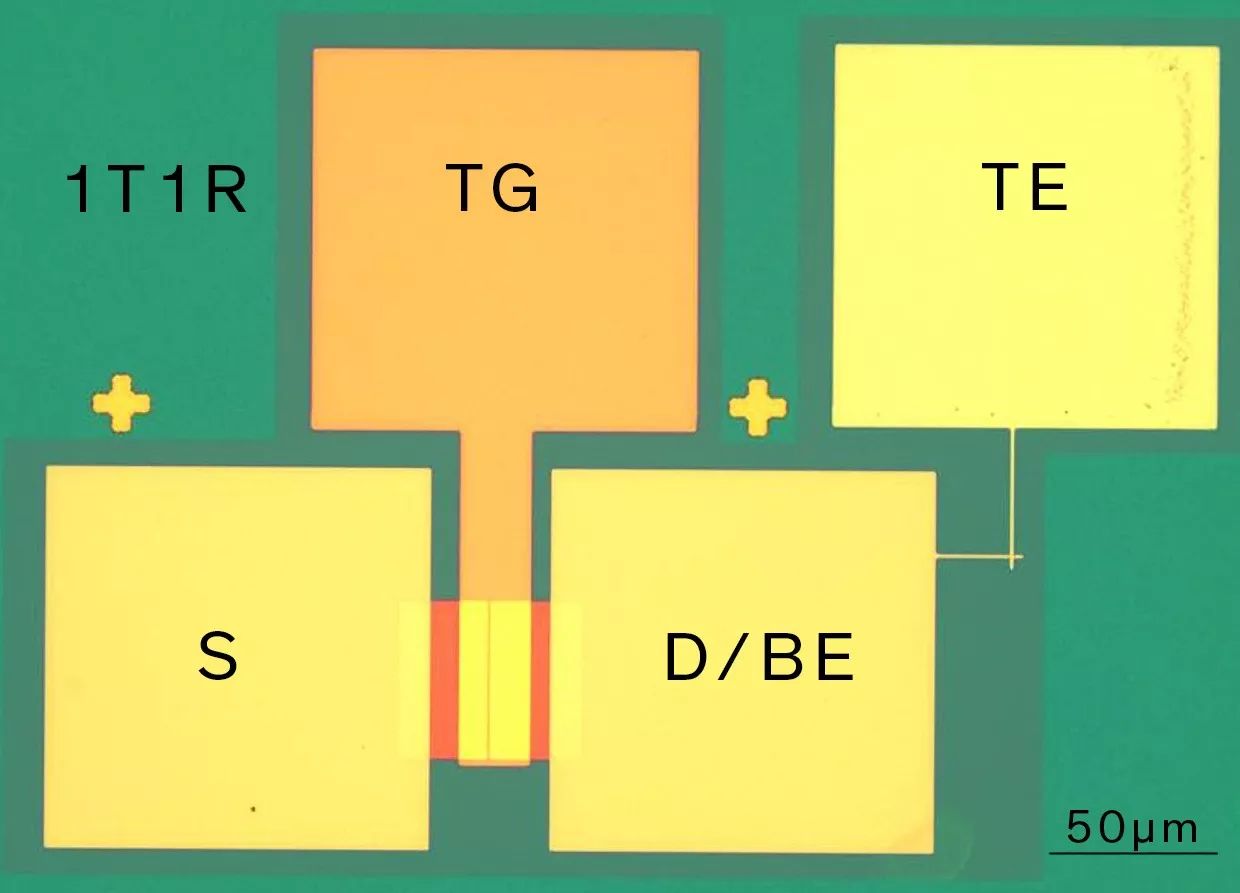

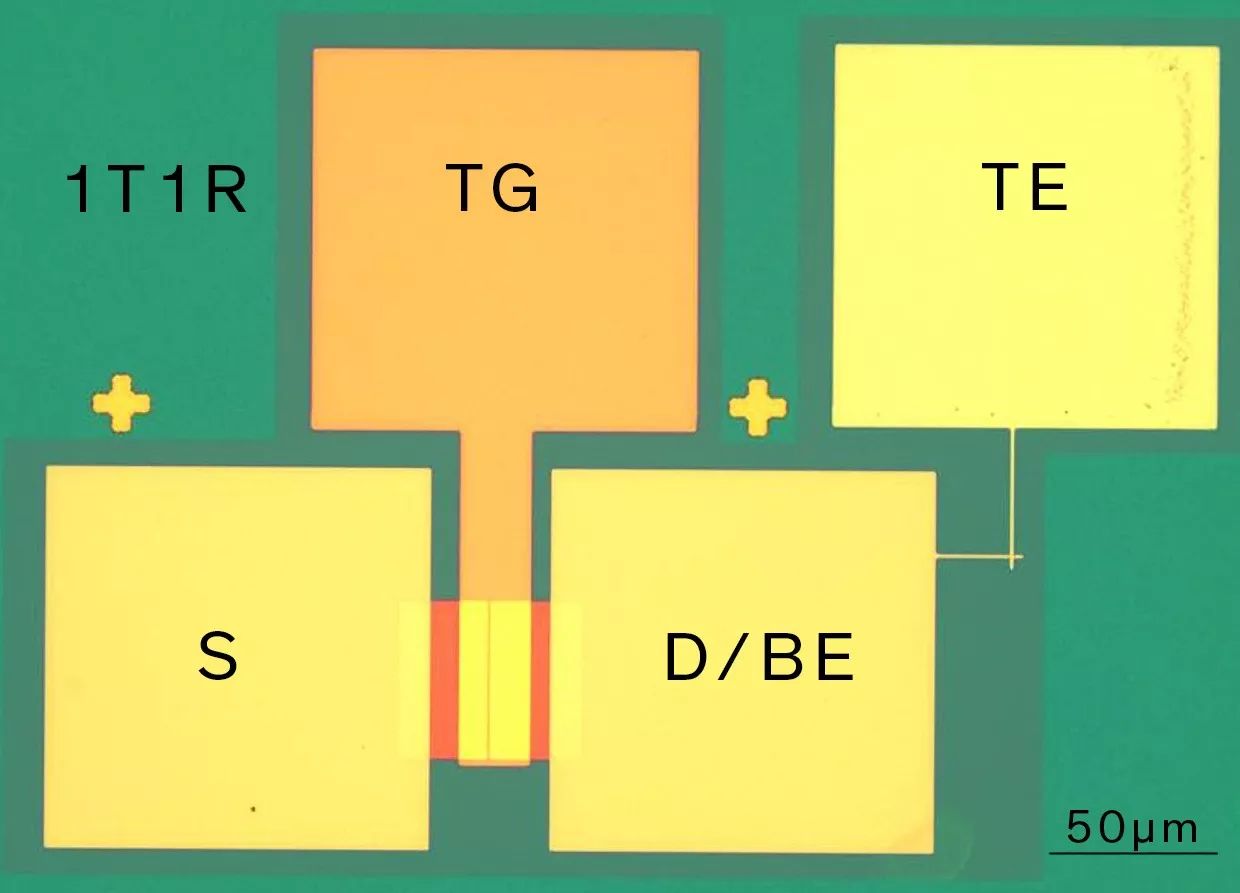

11 斯坦福研究人員開(kāi)發(fā)的芯片被稱(chēng)為“單晶體管單阻變存儲(chǔ)器”(1T1R)單元。這種1T1R存儲(chǔ)單元相對(duì)于含有阻變存儲(chǔ)器但沒(méi)有晶體管的存儲(chǔ)單元,能夠提供極大好處。

2018-01-23 17:23:59 7500

7500

本文開(kāi)始介紹了mos管的結(jié)構(gòu)特點(diǎn)、工作原理和MOS管應(yīng)用,其次介紹了PMOS管的概念和工作原理,最后介紹了兩種判斷NMOS管和PMOS管的方法。

2018-04-03 14:12:18 29704

29704

東芝公司近日發(fā)布了BENAND產(chǎn)品。該產(chǎn)品基于單層存儲(chǔ)單元(SLC)NAND閃存,并且內(nèi)嵌錯(cuò)誤糾正功能(ECC)。BENAND產(chǎn)品正式批量生產(chǎn)的時(shí)間為2012年3月。BENAND在東芝公司最先

2018-10-08 17:11:00 2440

2440 1.靜態(tài)局部變量的值在函數(shù)調(diào)用結(jié)束后不消失而保留原值,即其占用的存儲(chǔ)單元不釋放,在下一次該函數(shù)調(diào)用時(shí),該變量已有值,就是上一次函數(shù)調(diào)用結(jié)束時(shí)的值;

2.靜態(tài)局部變量屬于靜態(tài)存儲(chǔ)類(lèi)別,在靜態(tài)存儲(chǔ)

2019-03-14 14:28:11 3575

3575

FPGA的邏輯是通過(guò)向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來(lái)實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能,F(xiàn)PGA允許無(wú)限次的編程。

2019-11-12 07:09:00 1993

1993 SRAM表示靜態(tài)隨機(jī)存取存儲(chǔ)器,只要供電它就會(huì)保持一個(gè)值,它沒(méi)有刷新周期,由觸發(fā)器構(gòu)成基本單元,集成度低,每個(gè)SRAM存儲(chǔ)單元由6個(gè)晶體管組成,因此其成本較高。

2019-09-11 16:26:21 3574

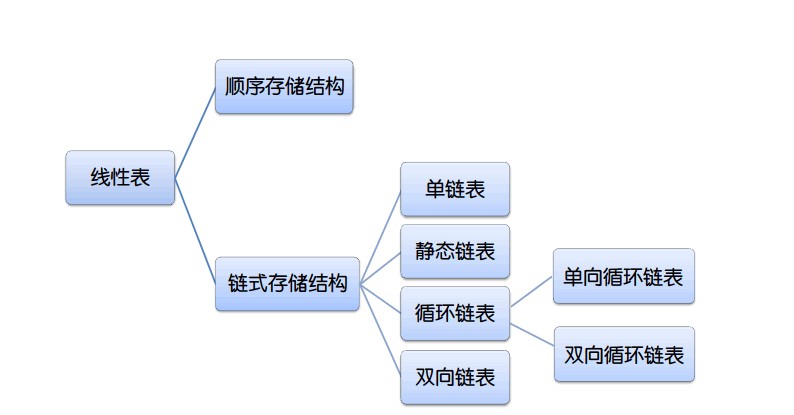

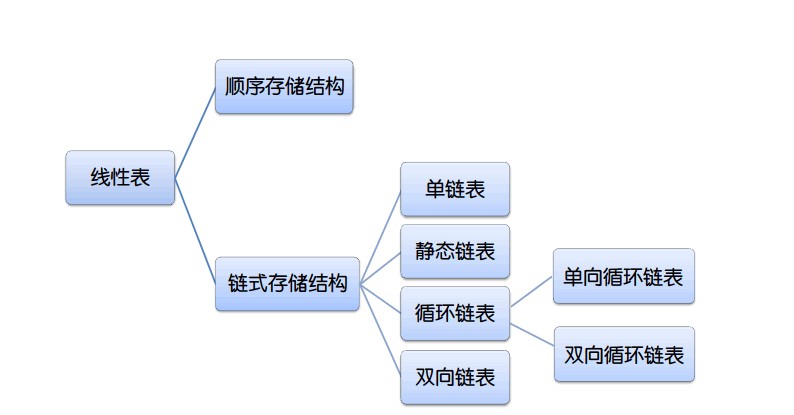

3574 順序存儲(chǔ)方法: 該方法把邏輯上相鄰的結(jié)點(diǎn)存儲(chǔ)在物理位置上相鄰的存儲(chǔ)單元里,結(jié)點(diǎn)間的邏輯關(guān)系由存儲(chǔ)單元的鄰接關(guān)系來(lái)體現(xiàn)。

2019-10-27 12:31:00 45911

45911

鎧俠株式會(huì)社(Kioxia Corporation)宣布開(kāi)發(fā)出創(chuàng)新的儲(chǔ)存單元結(jié)構(gòu)“Twin BiCS FLASH”。該結(jié)構(gòu)將傳統(tǒng)3D閃存中圓形存儲(chǔ)單元的柵電極分割為半圓形來(lái)縮小單元尺寸以實(shí)現(xiàn)高集成化。

2019-12-24 17:01:22 3790

3790 存儲(chǔ)單元的作用:可以進(jìn)行讀寫(xiě)操作以及存放數(shù)據(jù)。

2020-03-22 17:34:00 5392

5392 靜態(tài)RAM的基本構(gòu)造塊是SRAM存儲(chǔ)單元。通過(guò)升高字線的電平觸發(fā)存儲(chǔ)單元,再通過(guò)位線對(duì)所觸發(fā)的存儲(chǔ)單元進(jìn)行讀出或?qū)懭搿T?b class="flag-6" style="color: red">靜態(tài)CMOS存儲(chǔ)器中,存儲(chǔ)單元陣列將會(huì)占去整個(gè)存儲(chǔ)器芯片面積的一半以上,在一些

2020-05-14 09:19:47 4400

4400

磁性材料的存儲(chǔ)元,它可存儲(chǔ)一個(gè)二進(jìn)制代碼.由若干個(gè)存儲(chǔ)元組成一個(gè)存儲(chǔ)單元,然后再由許多存儲(chǔ)單元組成一個(gè)存儲(chǔ)器,就用來(lái)存放程序和數(shù)據(jù)了. 按其功能可分為:隨機(jī)存取存儲(chǔ)器(簡(jiǎn)稱(chēng)ram)和只讀存儲(chǔ)器(只讀ROM) RAM包括DRAM(動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)和SRAM(靜態(tài)隨機(jī)存取

2020-05-10 10:10:54 8308

8308 個(gè)名為Row Hammer的頑固安全漏洞。 Spin Memory的垂直環(huán)繞柵晶體管可以縮小MRAM和RRAM存儲(chǔ)單元。 Spin Memory將設(shè)備稱(chēng)為通用選擇器(Universal

2020-09-04 16:10:13 2895

2895 靜態(tài)存儲(chǔ)區(qū)存放全部的全局變量, 這些變量將在鏈接之后產(chǎn)生, 程序執(zhí)行完畢就釋放, 程序執(zhí)行的過(guò)程中它們占據(jù)固定的存儲(chǔ)單元, 而不會(huì)動(dòng)態(tài)的進(jìn)行分配和釋放。

2020-11-01 10:51:28 5015

5015

按照數(shù)據(jù)存取的方式不同,ram中的存儲(chǔ)單元分為兩種:靜態(tài)存儲(chǔ)單元一靜態(tài)RAM(SRAM);動(dòng)態(tài)存儲(chǔ)單元動(dòng)態(tài)RAM(DRAM)。 1.靜態(tài)存儲(chǔ)單元(SRAM):它由電源來(lái)維持信息,如觸發(fā)器,寄存器等

2020-12-02 14:31:30 2826

2826

該方法把邏輯上相鄰的結(jié)點(diǎn)存儲(chǔ)在物理位置上相鄰的存儲(chǔ)單元里,結(jié)點(diǎn)間的邏輯關(guān)系由存儲(chǔ)單元的鄰接關(guān)系來(lái)體現(xiàn)。

2020-12-02 10:17:55 38464

38464 數(shù)據(jù)必須首先在計(jì)算機(jī)內(nèi)被表示,然后才能被計(jì)算機(jī)處理。計(jì)算機(jī)表示數(shù)據(jù)的部件主要是存儲(chǔ)設(shè)備;而存儲(chǔ)數(shù)據(jù)的具體單位是存儲(chǔ)單元;因此,了解存儲(chǔ)單元的結(jié)構(gòu)是十分必要的。

2021-01-08 10:03:55 3383

3383 采用HSPICE分別對(duì)設(shè)計(jì)的存儲(chǔ)單元、延遲單元和積分器電路進(jìn)行了仿真,晶體管模型選用TSMC0.18μm標(biāo)準(zhǔn)數(shù)字工藝參數(shù)。電源電壓為±1 V;輸入電流iin=40μA,信號(hào)頻率fin=100 kHz

2021-02-18 10:06:39 2248

2248

采用基于物理的指數(shù)MOSFET模型與低功耗傳輸域MOSFET模型,推導(dǎo)了新的超深亞微米無(wú)負(fù)載四管與六管SRAM存儲(chǔ)單元靜態(tài)噪聲容限的解析模型.對(duì)比分析了由溝道摻雜原子本征漲落引起的相鄰MOSFET的閾值電壓失配對(duì)無(wú)負(fù)載四管和六管SRAM單元靜態(tài)噪聲容限的影響。

2021-03-26 15:17:54 6

6 NMOS管和PMOS管做開(kāi)關(guān)控制電路

2021-11-07 13:36:00 123

123 VDSR20M40XS84XX6V12是一種高速存取時(shí)間、高密度靜態(tài)隨機(jī)存取存儲(chǔ)器20Mbit。該芯片采用VDIC高密度SIP技術(shù)制造,堆疊六個(gè)SRAM芯片,采用CMOS工藝(6晶體管存儲(chǔ)單元)。它被組織為兩個(gè)256Kx40bit寬的獨(dú)立塊數(shù)據(jù)接口。可以使用專(zhuān)用的#CSn單獨(dú)選擇每個(gè)塊。

2022-06-08 14:22:58 0

0 VDSR16M16XS54XX4C12是一種高速存取時(shí)間、高密度靜態(tài)隨機(jī)存取記憶力采用CMOS工藝(6晶體管存儲(chǔ)單元)實(shí)現(xiàn)了高速存取時(shí)間高速電路設(shè)計(jì)技術(shù)。它被組織為四個(gè)256Kx16bit的獨(dú)立塊寬數(shù)據(jù)接口。可以使用專(zhuān)用的#CSn單獨(dú)選擇每個(gè)塊。

2022-06-08 11:57:22 0

0 VDSR8M16XS54XX2V12是一種高速存取時(shí)間、高密度靜態(tài)隨機(jī)存取存儲(chǔ)器。該SIP模塊采用VDIC非常密集的SIP技術(shù)制造,可堆疊四個(gè)4-Mbit SRAM芯片采用CMOS工藝(6晶體管存儲(chǔ)單元)。它被組織為兩個(gè)256K×的獨(dú)立區(qū)塊16位寬數(shù)據(jù)接口。

2022-06-08 11:53:18 0

0 OCE28V256X是一種單電壓(3.3V)、異步、rad-hard 32kbit x8內(nèi)存設(shè)備,使用抗-基于保險(xiǎn)絲的一次性可編程(OTP)存儲(chǔ)單元。采用了標(biāo)準(zhǔn)的1 30nm CMOS工藝用于

2022-06-08 11:22:48 1

1 中國(guó)科學(xué)院上海微系統(tǒng)與信息技術(shù)研究所研究員宋志棠、王浩敏組成聯(lián)合研究小組,首次利用GNR邊緣接觸制備了世界上最小的相變存儲(chǔ)單元器件。

2022-08-02 14:26:26 1524

1524 閃速存儲(chǔ)器(Flash Memory)又稱(chēng)閃存(Flash),是一種非易失性存儲(chǔ)器,用存儲(chǔ)單元閾值的高低表示數(shù)據(jù)。浮柵(Floating Gate )場(chǎng)效應(yīng)管(見(jiàn)圖5-80)是Flash存儲(chǔ)單元采用的主要技術(shù)。

2022-08-08 15:46:00 2239

2239 在當(dāng)前計(jì)算密集的高性能系統(tǒng)中,動(dòng)態(tài)隨機(jī)存儲(chǔ)器(DRAM)和嵌入式動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(embedded-DRAM,eDRAM)是主要的動(dòng)態(tài)快速讀/寫(xiě)存儲(chǔ)器。先進(jìn)的 DRAM 存儲(chǔ)單元有兩種,即深溝

2023-02-08 10:14:57 12490

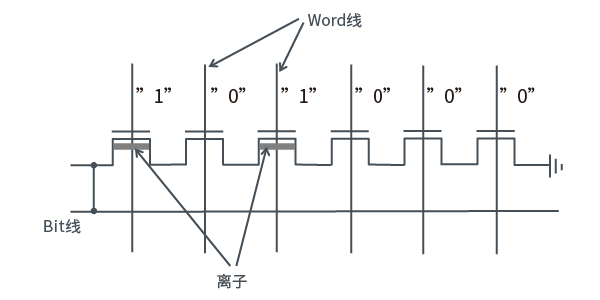

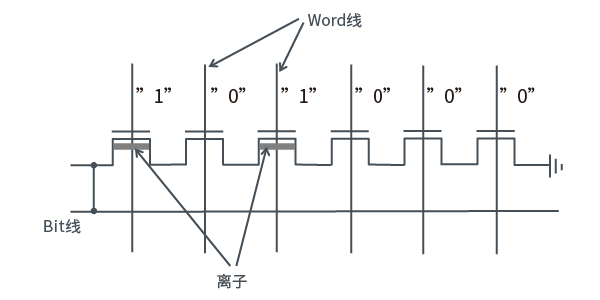

12490 ROM中的資料永遠(yuǎn)無(wú)法做修改。 高度集成化的NAND構(gòu)成。(1個(gè)晶體管單元) 數(shù)據(jù)的寫(xiě)入方法 在Wafer過(guò)程內(nèi)寫(xiě)入信息 “1”:將離子注入晶體管 “0”:不注入離子 數(shù)據(jù)的讀取方法 使讀取單元

2023-07-12 17:35:25 1898

1898

具體的在版圖設(shè)計(jì)中PMOS管和NMOS管是什么樣子的,我們來(lái)看看吧

2023-09-12 10:28:30 13349

13349

SSD主要由控制單元和存儲(chǔ)單元(當(dāng)前主要是FLASH閃存顆粒)組成,控制單元包括SSD控制器、主機(jī)接口、DRAM等,存儲(chǔ)單元主要是NAND FLASH顆粒。

2023-10-27 10:27:03 1343

1343

NMOS當(dāng)下管,即S極(源極)直接接地,只需控制G極(柵極)電壓即可控制NMOS管的導(dǎo)通或截止,因?yàn)镸OS管導(dǎo)通的條件取決于VGS的壓差。

2024-01-15 18:17:14 8956

8956

SRAM 中的每個(gè)存儲(chǔ)單元由多個(gè)觸發(fā)器構(gòu)成。每個(gè)觸發(fā)器可以存儲(chǔ)一個(gè)位的數(shù)據(jù),并在電源供電時(shí)一直保持該狀態(tài),不需要刷新操作。

2024-02-05 09:31:57 7079

7079 存儲(chǔ)單元是計(jì)算機(jī)系統(tǒng)中的基本元素,用于存儲(chǔ)和檢索數(shù)據(jù)。以下是對(duì)存儲(chǔ)單元的全面解析,涵蓋其定義、類(lèi)型、功能、特點(diǎn)以及在計(jì)算機(jī)系統(tǒng)中的重要作用。

2024-08-30 11:03:51 7578

7578 存儲(chǔ)單元和磁盤(pán)是計(jì)算機(jī)系統(tǒng)中存儲(chǔ)數(shù)據(jù)的兩個(gè)重要概念,它們?cè)诙x、功能、特點(diǎn)及應(yīng)用場(chǎng)景等方面存在顯著差異。

2024-08-30 11:25:00 1468

1468 NMOS晶體管和PMOS晶體管是兩種常見(jiàn)的金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)類(lèi)型,它們?cè)诙鄠€(gè)方面存在顯著的差異。以下將從結(jié)構(gòu)、工作原理、性能特點(diǎn)、應(yīng)用場(chǎng)景等方面詳細(xì)闡述NMOS晶體管和PMOS晶體管的區(qū)別。

2024-09-13 14:10:00 9544

9544 的內(nèi)部結(jié)構(gòu)和引腳類(lèi)型對(duì)于它們的功能和與外部設(shè)備的兼容性至關(guān)重要。 存儲(chǔ)器芯片的內(nèi)部結(jié)構(gòu) 存儲(chǔ)單元 :存儲(chǔ)器芯片的核心是存儲(chǔ)單元,它們可以是電容(在DRAM中)或浮柵晶體管(在Flash中)。 地址解碼器 :用于將輸入地址轉(zhuǎn)換為存儲(chǔ)單元的物理位

2024-09-18 11:04:03 3477

3477

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

1732

1732

4862

4862

4079

4079

10476

10476

27682

27682

20597

20597

8562

8562

8006

8006

1754

1754 18

18 22

22 67

67 710

710 1746

1746

0

0 11

11 7500

7500

29704

29704

2440

2440 3575

3575

1993

1993 3574

3574 45911

45911

3790

3790 4400

4400

8308

8308 2895

2895 5015

5015 2826

2826

38464

38464 3383

3383 2248

2248

6

6 0

0 0

0 0

0 1

1 1524

1524 2239

2239 12490

12490 1898

1898

13349

13349

1343

1343

8956

8956

7079

7079 7578

7578 1468

1468 9544

9544 3477

3477

評(píng)論