1 引言

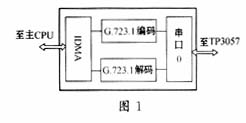

G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前在一些數字音視頻傳輸、高質量語音壓縮等系統中都得到廣泛應用。

2 G.723.1算法的復雜度分析

將G.723.1移植到TMS320C64xx后,就可借助TI集成開發工具CCS(Code Composer Studio)的Profile功能來評估其各個子程序或函數的執行運算量,從而把程序的優化集中在對程序性能影響最大的代碼上去。

通過分析可以看出,在G.723.1的編解碼算法中,碼本搜索所花費的運算量是比較大的,如Find_Best(),Find_Fcbk(),Find_Acbk():另外,在LPC分析和LSP參數的計算上也有運算量比較大的,如Comp_Lpc(),Lsp_Qnt(),Lsp_Svq()。

3 代碼的優化

代碼優化的工作有兩大目的:一是執行速度提高,實現實時;二是盡量不擴大程序體積(Code Size),使之在內存允許的范圍內。顯然,兩者存在一定的矛盾,當今超大規模集成電路的發展使RAM資源不再是系統的瓶頸,因此該部分工作的主要任務是怎樣提高執行速度。代碼的優化工作主要在CCS環境中進行。優化的原則是要充分考慮C64xx處理器超長指令字、多個運算單元和深度流水線的結構特點,以及避免過多的讀寫內存指令和程序轉移指令,充分發揮其強大的運算能力。具體方法包括(次序有先后):

3.1基本運算集的優化

G.723.1算法程序是用定點運算完成浮點運算,為了防止定點運算時可能溢出,許多運算需要進行飽和判斷,為此程序專門定義了基本運算集,實現諸如飽和加法、飽和乘法、除法和移位等操作。在程序中這些操作調用相當頻繁,經CCS的profile工具測試,基本運算函數集的調用占用了95%以上的CPU時間。因此,我們要從基本運算集的優化開始。在熟悉掌握C64xx指令集的前提下,分析基本運算集中各個函數完成的悉掌握C64xx指令集的前提下,分析基本運算集中各個函數完成的功能和對全局變量產生的影響,用C64xx指令取而代之或加以改編。其中包括對跳轉和流水線的優化討論、對乘積的飽和調整和全局變量OveRFlow的相關操作。

由于基本運算集以函數形式存在,兩次跳轉f函數的調用與返回1必不可少,將引起流水線的兩次打斷,表現為12個指令周期的占用。將這嶁基本運算函數集改成宏的形式,即將基本運算內嵌(inline)至lJ調用程序中,由此町以消除跳轉和流水線打斷帶來的指令周期占用,提高執行速度。雖然這樣做增加了代碼長度,多占用了一些內存,但由于基本運算函數體積均較小,再經過一定的代碼優化,在程序體積上的犧牲幾乎町以忽略。

基本運算的函數定義在BASIC.C文件里面,如果能夠對這些簡單甬數進行內聯指令(intrinsic)的優化,就能達到事半功倍的效果。內聯指令是匯編指令的直接映射,具有很高的效率。與此同時帶來的一個問題是溢出保護位Overflow的判斷,這是基本函數里用來標識溢出的全局變量,它的作用等同于CSR(Control Status Register)寄存器的SAT(Saturation)位,當數據溢出時,SAT位被系統自動設置為1,所以編解碼函數里對Overflow的判斷可以轉化成對SAT位的判斷。引用CSR寄存器時需要在最開始的時候聲明extem cregister volatile ansigned int CSR。

C64xx指令提供了飽和乘法指令SMPY,實現16"16位的乘法與飽和結果調整,其執行操作如下:

if(cond){

if((src 1*src2<<1)!=0x80000000)

dst=((src 1*src2)<<1);

else

dst=0x7ffffff;

}

else

nop;

將原指令中的乘法指令改為SMPY.就可以完成乘法和飽和調整兩種計算,這樣可以省去飽和調整3條指令。與此類似,其它的飽和運算,C64xx都提供了相應的指令實現,將普通運算指令替換為飽和運算指令,飽和結果調整部分的運算均可以省去。

3.2主程序的優化

主程序的優化手段主要采用了以下幾種方法:

(1)使用內聯函數(intrinsics)

內聯函數是可直接映射為C64xx指令的特殊函數,它在指令前加上"_”表示。例如:

#define L_add(L_var1,L_var2)? _sadd(L_var1,L_var2)

#define L_mult(var1,vat2)? _smpy(var1,var2)

等,基本函數的內聯優化需要對原函數的定義和內聯指令都比較熟悉。

使用內聯函數代替相應的C語句是一種非常簡便高效的優化方法。如上面提到的飽和乘法,在C語句中。我們通常要使用兩個嵌套的條件判斷語句來檢查結果是否溢出,而指令int_smpy(int a.int b) 則在完成乘b的運算后,再做一次飽和處理,這樣一條DSP指令就可完成C語言中多條語句才能完成的計算,可以節省很多時鐘周期。

(2)循環展開(loop—unrolling)

程序中的有很多的雙重循環和多暈循環(比如代數碼本搜索計算),由于C64xx優化器在優化時只在最內層循環中形成一個指令流水(最多可以達到8級流水),這樣循環語句就不能充分利用軟件流水線,而且對于內部循環次數較少的情況,消耗在prolog和eplog上的時鐘周期也不可忽視。針對這種情況,一個有效的辦法就是將雙重或多重循環展開,降低循環次數。這樣雖然代碼長度增加了,但有更多的運算能夠參加到pipeline中。由于減少了流水線排空和提高了功能單元的利用率,程序執行速度會大大提高。

(3)減少分支和調用指令,減少判斷指令

程序中的分支、調用以及判斷指令會引起程序的跳轉,而每個跳轉指令都有5個延遲間隙。因此延長了程序執行時間;另外,循環內跳轉也會使軟件流水受到阻塞,降低了代碼執行效率。優化中,可以使用內嵌、合并判斷語句來減少判斷次數或用邏輯指令替代判斷的方法盡可能的消除中斷流水線指令帶來的影響。

(4)使用字或雙字存取和計算

C64xx系列DSP是32位CPU,當16位數據在內存中連續存放時,可利用uint_amem4(void*ptr)或double & _amemd8 (void*ptr)指令進行字或雙字數據的讀取或存貯。這樣每次可同時存取2個或4個16位數據,由于從內存執行取數操作需要4個delay,所以減少存取次數可以節省大量的時鐘同期;同時,可利用C64xx指令集中特有的打包指令_pack2(unsigned a,unsigned b),_packh2(unsigned a,unsigned b)等將兩個16位數打包成一個32位數,在進行乘、加計算時則利用_add 2(int a,int b)、_mpy2(int a,int b)同時完成兩組16位數的加法和乘法,效率比單純16位數的加法和乘法提高一倍。

3.3匯編編程的優化

線性匯編是TI提供的一種匯編語言,其指令系統和匯編語言的指令系統完全相同,但在編寫時不需要指定寄存器和操作單元,也不需要考慮延時的問題,因此編寫線性匯編相對要容易一些。

經過以上的優化后,音頻編碼程序在DM642上的運行狀況有了很大改善,但是經測試仍然沒有到達可以接收的程度,而高級語言的效率幾乎發揮到了極致,所以在具體分析耗時大的模塊特點后,采用線性匯編語言重新編寫C代碼的低效率段程序,迸一步提高程序的執行效率。

在編寫線性匯編優化代碼的過程中,為了提高代碼執行效率,我們需要遵循以下原則:

(1)寫并行代碼:通過使用匯編指令并行執行的方法減少循環內的執行周期數,優化線性匯編代碼。這里的關鍵問題是弄清指令相關性,只有不相關的指令才能并行執行。辨別指令是否相關.可以使用相關圖。

(2)處理跳轉指令和轉移指令:匯編程序的一大特點就是頻繁地跳轉,當滿足不同的條件時,要求程序進行不同的操作,或跳到相應的位置。對于“大于”、“大于等于”、“小于”、“小于等于”等較為接近的邏輯判斷和處理,應慎重對待,否則將產生邏輯性錯誤,并且很難調試。當發生溢出需進行相應處理時,這種現象尤為突出。

(3)盡量減少循環體內的指令數[7]:G.72.1的算法實現,有許多是在循環內部完成的,有些地方如同定碼本搜索過程中,為了確定四個非0脈沖的位置和幅度,還用到了多重循環。在循環內部,特別是在嵌套較深的循環內部,減少一條指令可以大大降低程序的操作次數。例如。對于一個每重循環8次的四重嵌套循環,在最內層循環每減少一條指令,整個程序可以少執行84=4096語句。因此在設計程序時,能夠放在循環體外執行的語句.盡量放在循環體外執行。

(4)展開程序體:盡在一定條件下,盡量展開程序,以減少子程序的調用和返回次數,犧牲空問換取時間。

經匯編優化器優化后,代碼效率比C語言直接編譯有明顯提高。

4 優化工作的創新點

在對G.723.1的優化中.本文在前人研究成果的基礎上,針對DSP C64xx系列芯片提}n了一些有價值的新方法。這些創新點在不同程度上提高了代碼的優化速度和執行效率,在語音編解碼的DSP實時實現中起到了關鍵性作用。下面,本文將以舉例的方式闡明一些經典的方法。

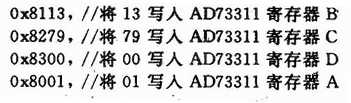

(1)編寫連接命令文件.cmd

明確了系統的程序和數據映射地址后,編寫連接器命令文件將部分調用次數較多的函數、堆棧段、數據段放入內存:cmd文件內容如下:

一L\evmdm642_echocfg.cmd //連接CCS提供的連接命令文件

SECTIONS

{

.tahles>SDRAM

.cinit>ISRAM?? //將變量初值表放入內存

. far >SDRAM

.const>ISRAM //將常數段放入內存

.pinit>SDRAM

. tin >SDRAM

.text>SDRAM

.test >ISRAM

}

一levmdm642bsl.lib //連接庫文件

一levmdm642_edma_aic23.164??? //連接驅動程序的庫文件

一lc6xlx_edma_mcasp.J64?? //連接串口McASP的庫文件

其中.test是筆者在C程序內用#pragma CODE_SECTION或DATA_SECTION自定義的段。

(2)高速緩沖寄存器Cache的使用

Cache即高速緩存,是位于CPU和片內存儲器之間的規模小速度快的存儲器。Cache的工作原理是保存CPU中最常用的數據。當Cache中保存著CPU要讀寫的數據時,CPU直接訪問Cache。由于Cache的速度與CPU相當,CPU能在零等待狀態下迅速地實現數據存取。只有在Cache中不舍有CPU所需的數據時CPU才去訪問片內存儲器。因此Cache的有效利用對整個程序速度的提高有著舉足輕重的作用。在主函數中加入以下代碼,使Cache使能:

CACHE_clean? (CACHE_L2ALL,0,0};? //清除Cache內原有內容

CACHE_setL2Mode? (CACHE_64KCACHE);? //設置Cache的大小為64K

CACHE_enableCaching? (CACHE_EMIFA_CE00);? //Cache使能

添加以上代瑪后,測試速度由原來的20幀/s提高到了400幀/s。提高了將近20倍。

5 結束語

本文詳緇分紹了G.723.1標準的DSP代碼優化工作,重點描述了代碼優化的方法和本課題的創新點.對于算法中的一些函數提出了獨創性改寫方法。基于線性匯編的優化以及Cache的有效利用使本課題的工作取得了顯著成果,在沒有降低音質的情況下,實現了DSP的語音實時編解碼。

本文作者創新點:在對G.723.1的優化中,針對TMS320DM 642 DSP系列芯片提出了一些有價值的新方法。例如:編寫連接命令文件.cmd和高速緩沖寄存器Cache的使用。這些創新點在不同程度上提高了代碼的優化速度和執行效率,在語音編解碼的DSP實時實現中起到了關鍵性作用。

語音編解碼算法G.723.1在DSP上的優化

- 語音(39582)

- 編解碼(20482)

相關推薦

熱點推薦

語音信號的A律編解碼的DSP實現

本文介紹了G.711標準的A律壓縮算法的基本原理,設計出了A律編解碼的軟件流程框圖,在以TMS320VC5416為處理器的硬件開發平臺上實現了語音信號的A律壓縮解壓算法,并給出了C54x的匯編語

2011-10-13 14:45:04 4161

4161

4161

4161

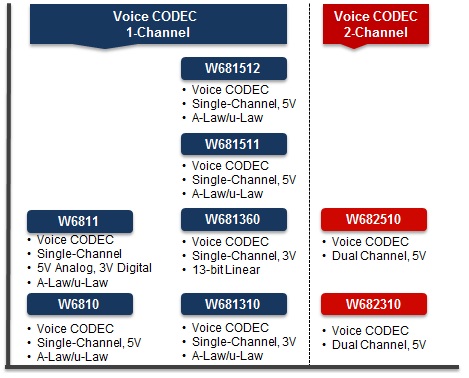

AI玩具爆發,音頻編解碼器如何滿足語音交互需求

編解碼器(Audio Codec)是用于壓縮、解壓縮和轉換音頻信號的硬件設備或軟件算法。其核心作用是在保證音質的前提下,減少音頻數據的存儲空間和傳輸帶寬需求。 ? 通常音頻編解碼器擁有硬件和軟件兩方面,硬件上擁有獨立的電子元件,包含ADC和

2025-06-20 01:07:00 7032

7032

7032

7032在FPGA上h.264視頻編解碼的實現

想在DE2-115的開發板上完成h.264視頻編解碼,自己的想法是在已有的tpad_camer代碼上加一軟核,但一直失敗,希望有相關經驗的高手指點下?

2014-03-05 16:24:19

在TMS320C6657器件上輕松運行經TI 優化的Opus編碼器/解碼器

適用于語音通信、聯網音頻甚至高性能音頻處理應用。較之 ARM 等通用處理器,此設計還通過在 DSP 上實現 Opus 編解碼器來提升性能。根據通用處理器上所運行代碼的優化級別,通過在 C66x TI

2022-09-22 06:32:42

語音壓縮算法研究

希望廣大DSP大俠們幫我出出主意,怎么才能寫一個好的音頻壓縮算法,最好是在時域的壓縮。頻域的壓縮發現都相對比較復雜。大家好,我是做語音芯片的。最近想研究一種壓縮率高,音質好,并且解碼簡單。最好能用8

2013-09-18 17:38:38

語音和音頻統一編解碼算法研究

最近在研究MPEG-D標準的語音和音頻統一編解碼算法(USAC),USAC是2011年才開始提出來的,感覺挺有研究意義的,大家有興趣可以互相交流下

2014-07-20 15:38:57

I91260語音芯片在SDS不同的編解碼格式有什么區別?

我正在使用 I91260 語音芯片,我在SDS 看到有不同的編解碼格式(AudioPlayback MD4 NuOneEx ...) 我想知道這些格式有什么區別,我如何更好的選擇使用那個格式?

我的另一個問題是,在那個文檔 展示了關于 音頻編解碼的 介紹,比如 采樣率,通道選擇 等描述

2023-08-21 07:39:16

ISD91260編解碼格式如何選擇?

我正在使用 I91260 語音芯片,我在SDS 看到有不同的編解碼格式(AudioPlayback MD4 NuOneEx ...) 我想知道這些格式有什么區別,我如何更好的選擇使用那個格式?

我的另一個問題是,在那個文檔 展示了關于 音頻編解碼的 介紹,比如 采樣率,通道選擇 等描述

2023-06-13 06:16:22

MP3解碼算法的軟件優化有什么方法?

,嵌入式MP3軟解碼器的應用將越來越廣泛。這里在分析MPEG I Audio Layer3解碼算法的基礎上,提出基于ARM946E處理器實現解碼算法的軟件優化方法。

2019-09-03 06:26:26

OMAPL138上移植G.722.1語音編碼算法

老師讓在OMAPL138上實現G.722.1語音編碼算法的移植。是不是只用C6748芯片就可以完成這個任務?還是DSP和ARM都要用?新手一枚,多謝指點,不勝感激!

2018-06-21 20:15:16

opus編解碼的相關資料分享

)====================================================================版權歸作者所有,未經允許,請勿轉載。====================================================================一、opus編解碼簡介Opus是一個完全開放,免版稅,高度通用的音頻編解碼器。在互聯網上Opus是交互式語音和音樂傳輸,也

2021-12-24 06:56:37

什么是基于嵌入式DSP的流媒體編解碼器?

可編程的DSP可用于實現各種現有的編解碼器和將來的編解碼標準。目前的趨勢是每兩年就會發布新的編解碼標準,每個新標準會需要更多的DSP周期。因此,選擇具有兼容性發展藍圖的DSP平臺(如ZSP)非常重要,這樣通過系統升級而不是重新設計即可滿足未來的系統要求。

2019-09-03 06:35:12

基于TMS320C6657實現的高效OPUS編解碼器解決方案包含BOM,PCB文件及參考指南

語音通信、聯網音頻甚至高性能音頻處理應用。較之 ARM 等通用處理器,此設計還通過在 DSP 上實現 Opus 編解碼器來提升性能。根據通用處理器上所運行代碼的優化級別,通過在 C66x TI DSP

2018-08-20 06:02:22

新一代視頻編碼標準H.264在高速DSP平臺上的實現與優化

H.264在TMS320C6416上的實現與優化。筆者的工作是在C6416DSP的開發平臺NVDK上實現了H.264的獨立編解碼算法,并對其進行優化,使其達到實時通信的要求,完成一個多媒體通信終端

2008-06-25 10:35:31

有哪位能用FPGA實現G.729語音編解碼的協議?

有哪位能用FPGA實現G.729語音編解碼的協議?初步我們打算外包,如題,如您有把握能做的話,請聯系我郵箱qox2009@163.com

2013-06-03 13:01:30

簡化針對云服務的語音檢測算法的部署

。資料來源:DSP集團Brosh說,像Amazon Web Services(AWS)這樣的云平臺對在芯片上配置寄存器不感興趣。相反,這些云服務專注于語音算法如何有效檢測喚醒詞。Brosh說:“他們希望

2021-03-03 10:46:14

請教關于DM368編解碼算法創建順序的問題

各位大神們你們好,請問DM368 dvsdk中含有編解碼的程序中,打開引擎以后,只能先創建解碼算法再創建編碼算法嗎?如果反之,則報錯創建解碼h264失敗,encodedecode例程中確實如此,請問,這是必須的嗎

2018-07-25 06:42:22

音頻編解碼芯片 VS1005最集成的音頻編解碼芯片

芯片,具有低功耗、高保真的音質效果,編解碼格式全面,帶有自主產權的低功耗DSP 處理器核VS_DSP4,可做主機也可做叢機。適合 廣播、車載、電梯、樓宇對講、卡拉OK、錄音筆、智能家居(背景音樂

2012-11-06 09:44:06

N9400語音芯片MP3芯片音樂解碼芯片語音ic

憑借不斷優化自主的音頻編解碼算法,以及更先進的芯片設計,來保證語音芯片高保真,高識別率,滿足客戶在產品應用中越來越高的技術要求。https://www.n-ec.

2021-10-27 09:54:49

MPEG4視頻處理編解碼算法代碼

MPEG4視頻處理編解碼算法代

The files in this directory comprise ANSI-C language reference implementationsof

2008-10-30 14:22:25 56

56

56

56語音編解碼芯片MT8965在ALU中的應用

語音編解碼芯片MT8965在ALU中的應用::MT8965是一種功能較強的語音編解碼芯片,它采用( 律編碼,可通過控制總線接收從處理器.發出的控制信號來寫控制寄存器,從而控制驅動輸

2008-11-11 09:26:17 28

28

28

28無線音箱藍牙語音ic MP3解碼芯片

憑借不斷優化自主的音頻編解碼算法,以及更先進的芯片設計,來保證語音芯片高保真,高識別率,滿足客戶在產品應用中越來越高的技術要求。

2022-05-20 09:28:59

G.729B編解碼算法在DM642上的實現與優化

語音通信是多媒體通信的基礎為了提高語音通信的效率與質量,對高質量低位率靜音壓縮算法G.729B進行了研究,將該算法移植到”公司最新一代定點數字信號處理器,期陽么)OM翻2上

2009-03-18 10:45:06 16

16

16

16基于DSP 的信道譯碼算法優化

在DSP 上移植算法,代碼優化程度成為提高系統性能、縮短開發周期的瓶頸。同時針對復雜算法在DSP 上的實現, 也產生很多優化策略、方法。本文以在數字通信系統中應用廣泛的Viter

2009-04-15 11:15:44 18

18

18

18語音編解碼芯片MT8965在ALU中的應用

MT8965是一種功能較強的語音編解碼芯片,它采用A律編碼,可通過控制總線接收從處理器發出的控制信號來寫控制寄存器,從而控制驅動輸出信號。文章介紹了MT8965的性能特點及其在A

2009-04-25 17:13:29 20

20

20

20語音編解碼芯片MT8965在ALU中的應用

MT8965是一種功能較強的語音編解碼芯片,它采用A律編碼,可通過控制總線接收從處理器發出的控制信號來寫控制寄存器,從而控制驅動輸出信號.文章介紹了MT8965的性能特點及其在ALU中的

2009-04-27 15:54:35 51

51

51

51AC-3解碼算法的通用DSP實現

Audio Compression-3(A C-3)算法廣泛應用于電影、DVD.DTV等消費電子領域。本文設計并實現了一種AC-3軟件解碼器,并成功地在通用DSP (TMS320C6701)上優化實現T AC-3實時解碼算法。

2009-05-08 16:46:03 20

20

20

20基于DSP芯片的MELP聲碼器的算法實現

論文對MELP 編解碼算法的原理進行了簡要分析,討論了如何在定點DSP 芯片TMS320VC5416 上實現該算法,并研究了其關鍵技術,最后對測試結果進行了分析。關鍵詞:MELP;語音編碼;

2009-08-06 08:46:47 20

20

20

20G.723.1 語音壓縮算法的分析及DSP實現

本文首先闡述了G.723.1語音編解碼標準的流程。根據低功耗、高性能的16位定點的數字信號處理芯片TMS320DM642的特點對源代碼中運算量較大的模塊進行了代碼優化。最后,在DSP硬

2009-08-10 10:00:11 31

31

31

31基于DSP改進的MBE語音算法的研究

在介紹MBE 語音算法以及TMS3201VC5402 定點DSP 芯片的基礎之上,詳細的討論了改進的MBE 語音算法以及它在TMS320VC5402 上實時實現的關鍵技術,實驗表明,改進以后的MBE 語音算法在TMS320VC54

2009-08-13 09:59:04 14

14

14

14基于G.729算法的新型語音通信系統的實現

在簡單介紹G.729 算法的編解碼原理的基礎上,介紹了如何用TMS320VC5402DSP 實現該算法。詳細介紹了硬件的實現框圖和軟件實現的流圖,文章的最后給出了實驗結果并對其作了分析

2009-09-10 16:34:59 12

12

12

12基于定點DSP語音錄放系統的設計

提出了一種基于定點DSP 的語音錄放系統。著重討論了DSP 芯片TMS320VC5416 與音頻編解碼芯片TLV320AIC23 的硬件接口和軟件設計,并在此硬件基礎上實現語音信號的采集、播放、存儲、回

2009-09-16 11:16:09 23

23

23

23基于TMS320C6713的G.723.1語音編解碼的實時實

ITU-T G.723.1 是一種用于多媒體通信的雙碼率語音編碼標準。本文在簡單介紹其編解碼算法和浮點數字信號處理器TMS320C6713 之后,著重介紹了該編解碼算法在TMS320C6713 DSK 上的軟件和硬

2009-11-27 15:31:23 10

10

10

10G.726語音編解碼器在SoPC中的實現

在對G.726 語音編解碼標準分析的基礎上給出了基于FPGA 的DSP 設計流程,利用MATLAB/Simulink、DSP Builder 和SOPC Builder 工具設計了G.726 語音編解碼器,通過仿真實驗驗證了所設計的編解碼器模

2009-11-30 14:59:24 12

12

12

12G7231算法在DSP上的優化

在ITU-T 的G.723.1 語音編解碼算法基礎上,本文詳細介紹了該算法在定點 C 語言程序和全匯編程序實現時的關鍵技術和優化策略,使優化后的 G.723.1 編碼器在內存占用率和運算復雜

2009-12-18 14:40:37 9

9

9

9基于DSP6711的OFDM技術編解碼實現

基于DSP6711的OFDM技術編解碼實現:基于浮點數字信號處理芯片DSP6711, 采用軟件無線電方法構建一個基本的O FDM 通信系統。在用MA TLAB 語言對該通信系統進行仿真的基礎上, 完成了CCS2. 1

2010-01-01 11:39:11 22

22

22

22三代移動通信變速率語音編解碼AMR-WB+算法優化

首先簡要介紹了AMR-WB+語音壓縮算法的基本原理,描述了AMR-WB+編解碼流程;然后通過兩類優化策略對AMR-WB+算法進行優化;最后給出了優化前后編解碼復雜度比較,并對結果進行了分析。

2010-03-01 15:03:51 20

20

20

20G.726語音編解碼器在SoPC中的實現

在對G.726語音編解碼標準分析的基礎上給出了基于FPGA的DSP設計流程,利用MATLAB/Simulink、DSP Builder和SOPC Builder工具設計了G.726語音編解碼器,通過仿真實驗驗證了所設計的編解碼器模型

2010-07-16 15:06:52 18

18

18

18在DSP上G.729A算法的優化

在ITU-T的G.729A語音編解碼算法基礎上,本文介紹了使用TI公司的TMS320C6x系列DSP實現該算法的一些線性匯編的具體優化技術,這在很大的程度上降低了該算法的計算復雜度,而輸出語音

2010-07-27 16:44:30 17

17

17

17基于定點DSP語音錄放系統的設計

提出了一種基于定點DSP的語音錄放系統。著重討論了DSP芯片TMS320VC5416與音頻編解碼芯片TLV320AIC23的硬件接口和軟件設計,并在此硬件基礎上實現語音信號的采集、播放、存儲、回放。

2010-08-05 14:58:44 42

42

42

42ISD5216 集成編解碼和語音錄放芯片的應用

ISD5216 集成編解碼和語音錄放芯片的應用

ISD5216是華邦電子美洲公司推出的具有語音編解碼和數據存儲功能的語音錄/放芯片。該芯片具

2008-11-11 09:05:02 1632

1632

1632

1632

多樣化的語音編解碼芯片

多樣化的語音編解碼芯片

由于可攜式產品愈來愈多,因此對于音效播出的功能要求也就愈被要求能夠達到高音質輸出的能力,事實上,目前在市場上有相當多的音效語音解

2008-11-11 09:07:20 3899

3899

3899

3899

G.723.1編譯碼算法的DSP實現

【摘 要】 介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法

2009-05-10 19:54:11 1801

1801

1801

1801

采用DSP芯片的MELP聲碼器的算法設計方案

采用DSP芯片的MELP聲碼器的算法設計方案

摘要:論文對MELP編解碼算法的原理進行了簡要分析,討論了如何在定點DSP芯片MS320VC5416上實現該算法,

2010-03-06 14:20:11 1809

1809

1809

1809

G.723.1算法在DSP上的優化

G.723.1算法在DSP上的優化

1 引言

G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標

2010-04-12 15:19:35 962

962

962

962基于AMR語音編解碼算法的VoIP系統

本文提出了一種基于AMR語音編解碼算法的新VoIP系統,該系統可以根據網絡信道質量的好壞來自適應地選擇一種最佳的傳輸速率,從而使得合成后的語音質量有了更加良好的QoS保障。

2010-06-24 11:05:16 1974

1974

1974

1974

分紹了G.723.1標準的DSP代碼優化

G.723.1是刪組織于 1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。

G.723.1主要用于對語音及其它多媒體聲音信號的

2010-07-02 09:06:57 1169

1169

1169

1169ADPCM語音編解碼VLSI芯片的設計方法

ADPCM算法及其編解碼器原理

ADPCM(Adaptive Differential Pulse Code Modulation,自適應差分脈沖編碼調制)綜合了APCM的自適應特性和DPCM系統的差分特性,是一種性能較好的波形

2010-09-03 16:58:27 2894

2894

2894

2894

基于AMBE-2000編解碼芯片的語音系統

0 引言

語音通信是數字通信系統中最常用的通信方式之一,優良的語音編解碼算法能夠更加有效地節省帶寬資源,提高頻率利用率。現在語音編碼技術可以廣

2010-10-26 09:44:38 7211

7211

7211

7211

G.723.1編譯碼算法的DSP實現

介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法,通過了ITU-T的所

2011-07-06 09:49:07 1808

1808

1808

1808

G.726語音編解碼在SoPC系統中的實現

G.726是ITU前身CCITT于1990年在G.721和G.723標準的基礎上提出的關于把64kbps非線性PCM信號轉換為 40kbps、32kbps、24kbps、16kbps的ADPCM信號的標準。G.726標準算法簡單,語音質量高,多次轉換后語音

2012-08-06 09:28:06 1784

1784

1784

1784

基于DSP的G.723.1數字對講機基帶系統中的應用分析

效率,已成為當前急需解決的問題之一。DSP數字信號處理器的運算能力越來越強,本設計采用TI公司的通用定點DSP TMS320C5509A作為基帶系統的處理器,主要對G.723.1語音壓縮編碼在頻帶、DSP資源有限的數字對講機基帶系統中的具體應用進行

2017-10-24 10:22:42 0

0

0

0基于DSP的G.723.1語音編碼算法實現方案分析

壓縮處理方法,G.723.1 語音編碼 算法 便是ITU-T(國際電信聯盟電信標準化部門)制定的H.324協議簇首推的標準算法,主要用于低比特率多媒體業務的話音或其他音頻信號分量的壓縮。它是一種雙速率語音編碼標準,其中6.3 kb/s的速率提供了

2017-10-25 10:05:22 1

1

1

1基于DSP的語音編解碼算法G.723.1優化分析

1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前在

2017-10-25 11:13:56 0

0

0

0DSP在數字語音壓縮系統中的應用

優秀的語音壓縮系統要求能夠在軟硬件資源占用比例低和壓縮編解碼時間短的同時可以實現多通道語音實時壓縮。目前,G.729A算法多是在TI的5000系列DSP上實現單通道或雙通道語音壓縮,而本設計在現有的TMS320C6711系列DSP平臺上使用最少

2017-10-26 10:43:43 0

0

0

0基于DSP的G.729A語音壓縮算法測試分析

優秀的語音壓縮系統要求能夠在軟硬件資源占用比例低和壓縮編解碼時間短的同時可以實現多通道語音實時壓縮。目前,G.729A算法多是在TI的5000系列DSP上實現單通道或雙通道語音壓縮,而本設計在現有的TMS320C6711系列DSP平臺上使用最少

2017-10-26 16:50:23 0

0

0

0語音編解碼算法G.723.1在DSP上的優化

1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前在

2017-11-01 16:03:40 0

0

0

0詳解G.723.1算法在DSP上的優化

1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前在

2017-11-02 10:43:04 0

0

0

0多制式語音編解碼算法的DSP設計

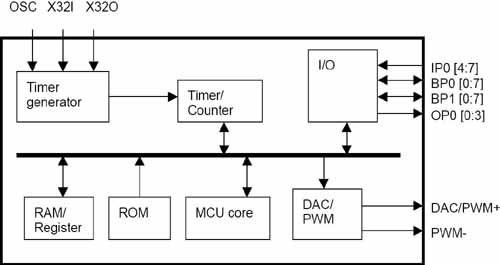

的可靠性和效率。因此,研究語音處理技術并將其用基于DSP芯片硬件系統實現有著非常重要的現實意義和廣闊的市場前景。本文介紹了語音編解碼硬件平臺的設計思路和編解碼算法在硬件平臺上的實現和優化過程,同時給出了硬件平臺結構

2017-11-06 14:14:10 3

3

3

3基于TMS320C6201的G.723.1多通道語音編解碼分析

優化方法以降低計算量,最后給出了各個主要模塊的性能指標。該實現能夠在200MHz的C6201 DSP上實現16路語音信號的實時編解碼,完全符合ITU-T G.723.1標準的定點算法,通過了ITU-T的所有測試

2017-11-06 14:55:13 1

1

1

1基于FPGA驗證所設計的ADPCM算法語音編解碼電路

近年來,多媒體技術逐漸深入到人們的生活中。MP3播放器已經成為流行的便攜式音頻播放設備,由于MP3編碼算法非常復雜,目前,一部分MP3播放器的錄音功能主要基于ADPCM算法和DSP來實現。本文闡述了ADPCM語音編解碼VLSI芯片的設計方法以及利用FPGA的硬件實現。

2019-07-02 08:08:00 3763

3763

3763

3763

CML升級語音編解碼產品CMX655D

據麥姆斯咨詢報道,CML升級了其語音編解碼產品CMX655D。該語音編解碼器集成兩個匹配通道和數字信號處理技術(DSP),以及效率高達90%、功率為1W的無濾波器D類音頻放大器,支持數字MEMS麥克風。

2018-10-29 17:10:54 4854

4854

4854

4854淺談SinoV-200I 2FXS IAD語音網關

技術特性:

● IEEE 802.3 10 Base T

● 支持G.711A/U,G.723.1,G.729 /A/B/AB 和GSM610語音編解碼

2019-11-13 09:06:22 2620

2620

2620

2620

SinoV-100AI單網口單FXS IAD語音網關詳細參數介紹

技術特性:

● IEEE 802.3 10 Base T

● 支持G.711A/U,G.723.1,G.729 /A/B/AB 和GSM610語音編解碼

2019-11-13 10:51:26 3073

3073

3073

3073

基于32位浮點DSP芯片TMS320C6713實現語音編解碼系統的設計

本系統使用TI公司浮點型DSP TMS320C6713實現G.723.1等語音編解碼,為G.723.1、G.729等常用的低碼率語音壓縮標準提供運行及測試硬件平臺。有別于大多數編解碼系統,本設計采用

2020-09-21 09:58:07 5162

5162

5162

5162

DSP芯片實現語音編解碼技術的設計方案

、并行總線共用和丌AG菊花鏈技術。通過國內外技術對比和網絡性能測試,DSP實現語音編解碼技術最終在多個項目中得以廣泛應用,為今后語音編解碼技術的發展提供了借鑒經驗。

2021-04-11 11:39:38 18

18

18

18NANDFLASH快速BCH編解碼算法及便件實現

NANDFLASH快速BCH編解碼算法及便件實現(嵌入式開發自學網)-NANDFLASH快速BCH編解碼算法及便件實現? ? ? ??

2021-07-30 14:14:40 9

9

9

9BCH編解碼器在NAND Flash主控中的研究與優化實現

BCH編解碼器在NAND Flash主控中的研究與優化實現(嵌入式開發培訓哪家好)-該文檔為BCH編解碼器在NAND Flash主控中的研究與優化實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 10:43:36 19

19

19

19探究SoundStream神經音頻編解碼器

情況下,音頻編解碼器對最終用戶來說應是透明的,這樣解碼后的音頻在感覺上便可與原始音頻幾無差別,且編碼/解碼過程不會存在感知延遲。 在過去的幾年里,我們已經成功開發出不同的音頻編解碼器,如 Opus

2021-09-23 09:49:10 3808

3808

3808

3808

編解碼一體機相對于傳統的編解碼設備有哪些優勢?

編解碼一體機相對于傳統的編解碼設備具有多個優勢。以下是編解碼一體機的幾個主要優勢: 高效實時的視頻處理能力:編解碼一體機采用先進的編解碼算法和云計算技術,能夠實現高效、實時的視頻處理,滿足各種應用場

2024-01-31 14:56:04 2267

2267

2267

2267

電子發燒友App

電子發燒友App

評論