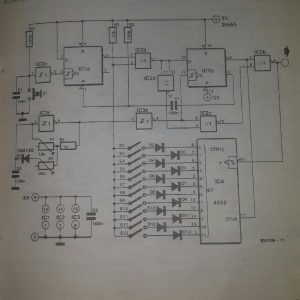

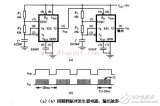

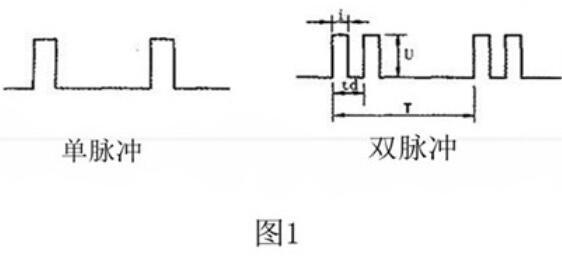

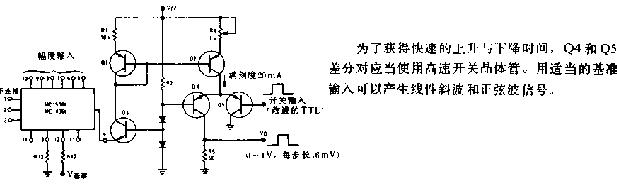

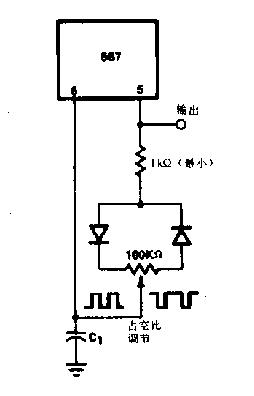

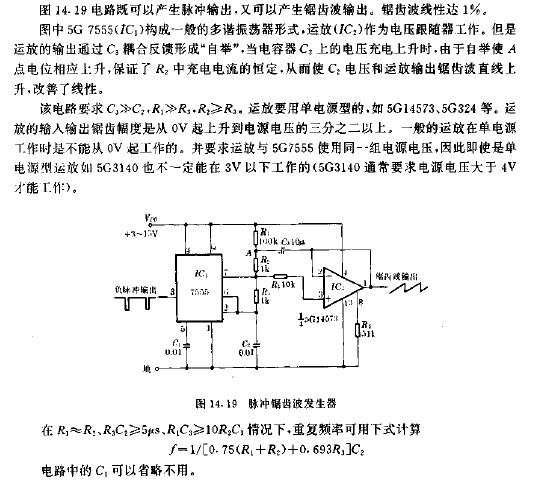

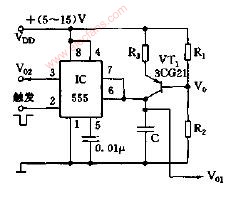

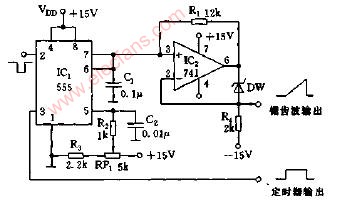

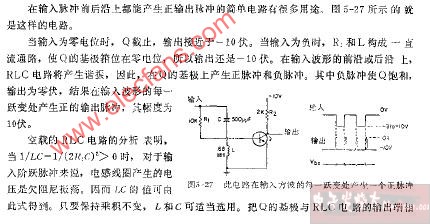

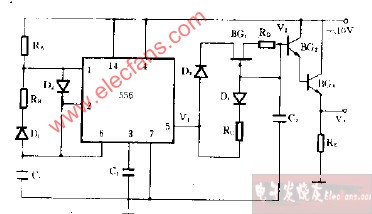

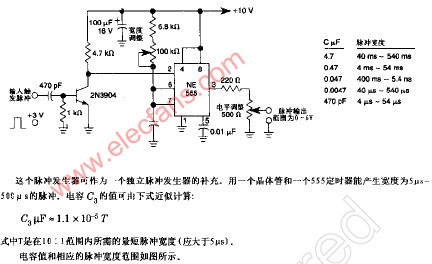

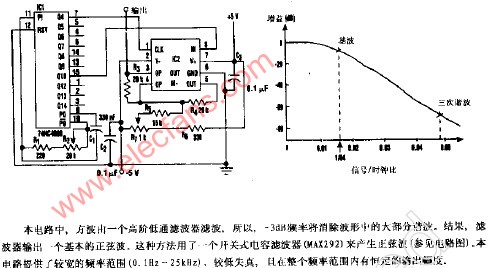

脈沖波群發生器又稱“Bust波發生器”,多用于遙控、測量、報警等場合的信號源。如果對波群持續期內的脈沖個數要求不嚴,一般采用二塊555(或一塊556)集成電路。如圖1所示。

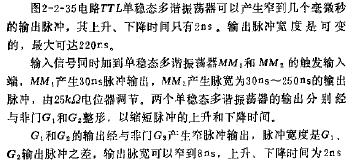

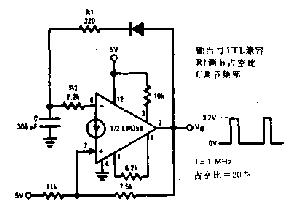

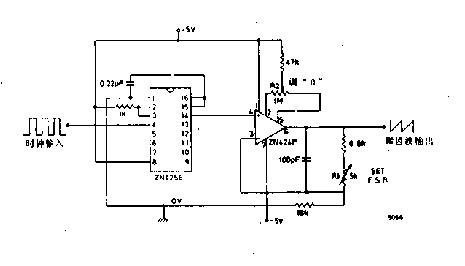

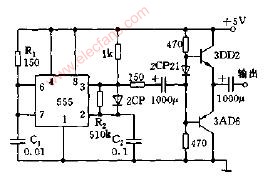

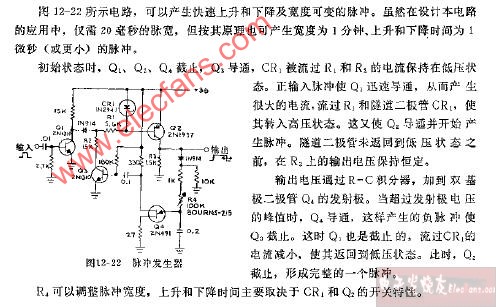

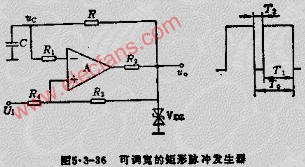

將兩塊555集成電路分別連成振蕩器,用較低頻率的振蕩器(IC1)輸出控制較高頻率的振蕩器(IC2)。IC1輸出(OUT1)為低電平時,IC2停振,此時IC2輸出(OUT2)低電平;IC1輸出(OUT1)為高電平時,IC2振蕩,IC2輸出(OUT2)脈沖振蕩信號。通過調節二個振蕩器的頻率,可以調節輸出波群的間隔和輸出波群持續期內的脈沖個數,但調節較難,精度不高。另有一種對波群持續期內脈沖個數可控、精度較高、調節容易的脈沖波群發生器,如圖2所示。

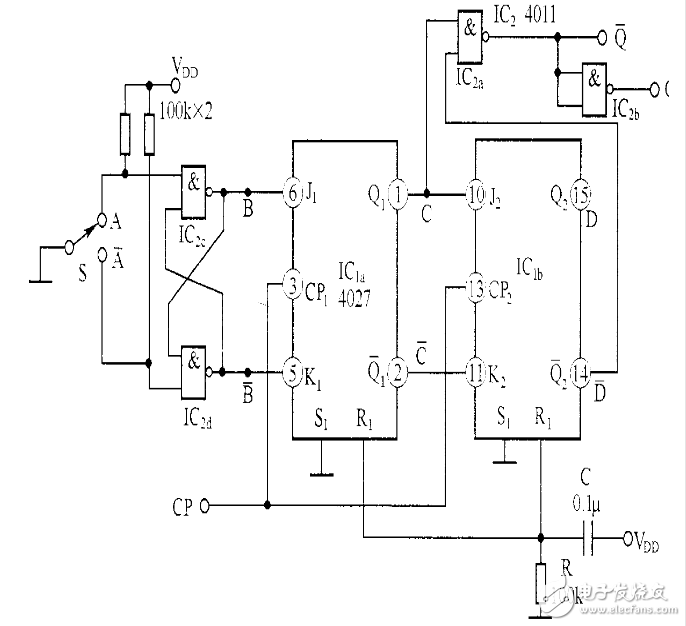

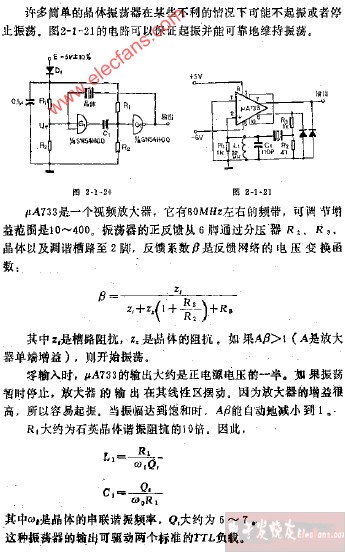

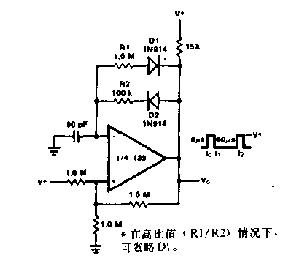

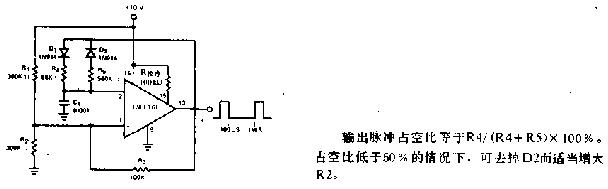

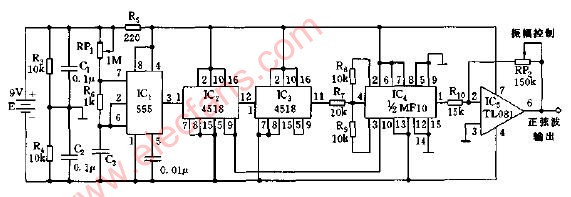

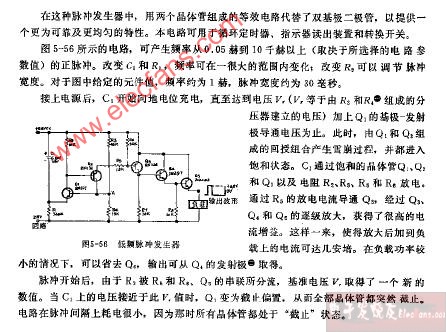

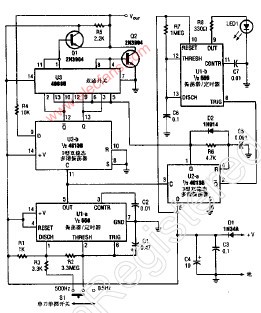

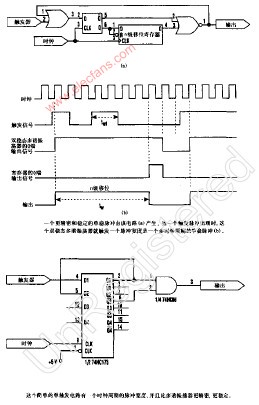

電路由可控脈沖振蕩器(IC1)、十進制計數器/脈沖分配器(IC2)及脈沖間隔時間控制電路三部分組成。IC1及其外圍元件(R1~R3、C1~C2、D1)構成可控脈沖振蕩器,波群信號由IC1的第③腳輸出。該振蕩器能否振蕩取決于受控端A點的電位。A點為高電平時,振蕩器停振;A點為低電平時,振蕩器振蕩。CD4017(IC2)接成下降沿觸發的計數器,觸發電平取自IC1的⑦腳,IC2的輸出端Y1~Y9由預置鍵S1~S9選擇,加至受控振蕩器的受控端及間隔時間控制電路(R4、C3、D2)的輸入端(A點)。間隔時間控制電路的輸出端(B端)加至計數器的復位端。工作過程如下。

假設按下預置鍵S5,計數器輸出端Y5輸出為低電平,此時B點為低電平,計數器處于計數狀態,A點為低電平,振蕩器振蕩。IC1的⑦腳輸出的方波下降沿觸發IC2計數進位。當第5個脈沖下降沿到來時,IC2的Y5輸出端變為高電平。通過其按鍵S5使受控端A點也變為高電平,迫使IC1停振,這樣波群持續期內的脈沖個數正好為5個。在IC1停振后,IC2輸出端Y5的高電平,通過電阻R4給電容C3充電。當B點的電位大于計數器復位電位時,計數器復位。此時Y5為低電平,IC1又重新起振。電容C3通過二極管D2放電,確保在IC1振蕩器⑦腳輸出的第一個脈沖波下降沿到來前,計數器恢復計數狀態。這樣周而復始,就產生了波群脈沖。該電路通過控制預置鍵S1~S9,可以在波群持續時間內得到所需個數的脈沖;調節IC1的振蕩頻率,可以改變波群持續期內的脈沖頻率;調節R1和C1的值,可以調節波群的間隔時間。如果要求波群持續期內的脈沖個數大于9,可將計數器進行相應的擴展。

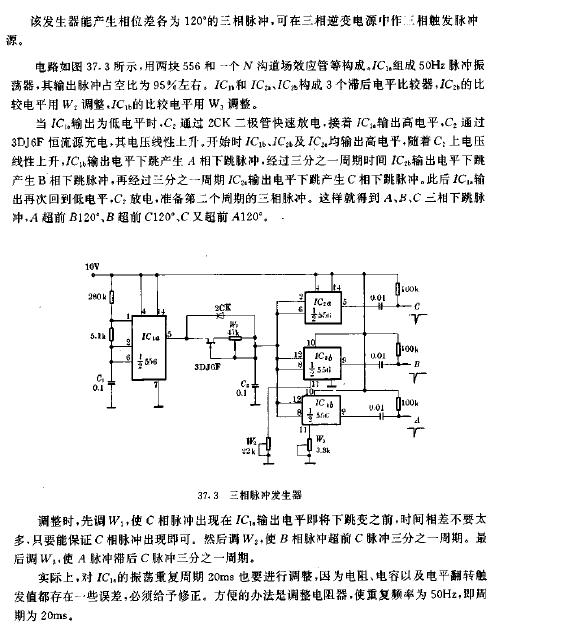

- 組圖脈沖(5470)

- 群發生器(5355)

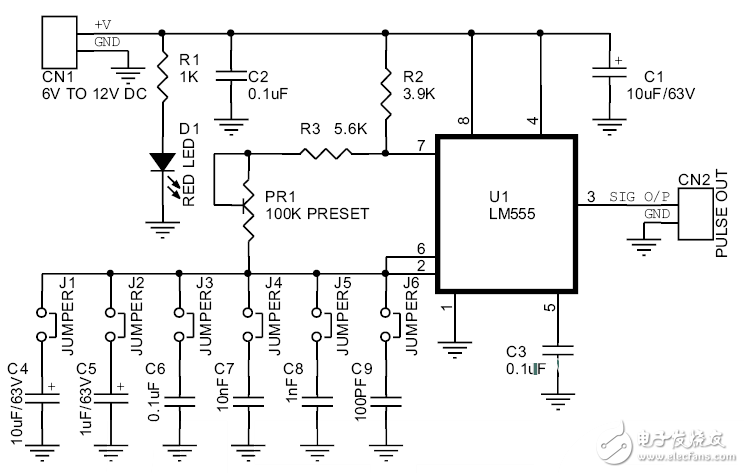

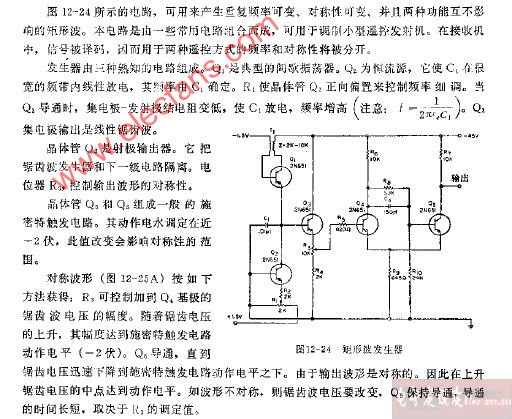

脈沖發生器電路原理圖

4348

4348

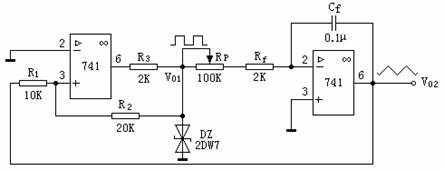

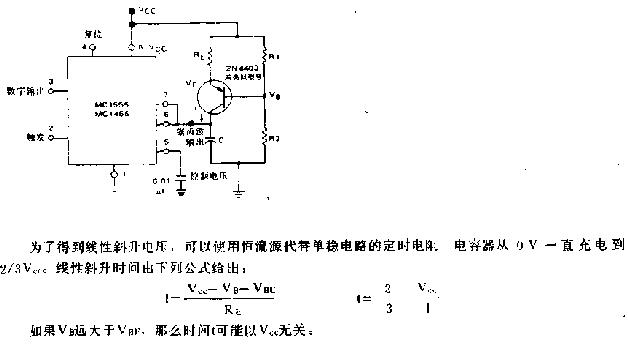

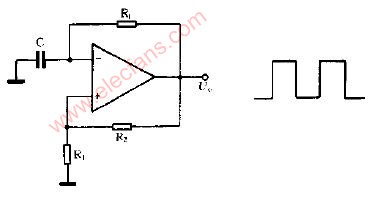

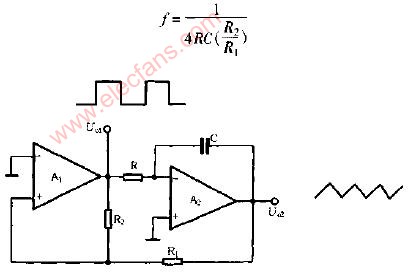

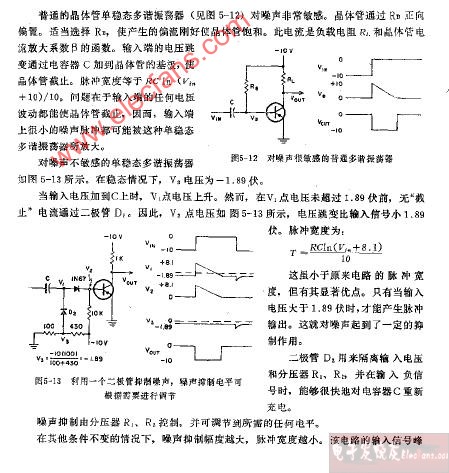

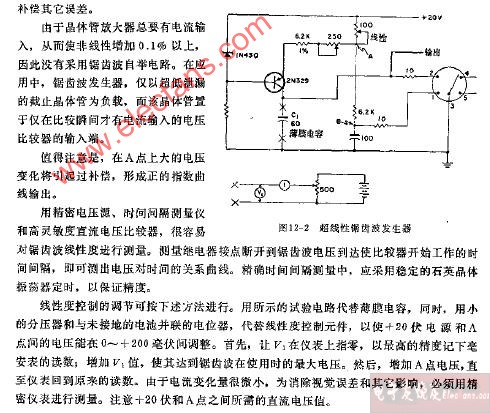

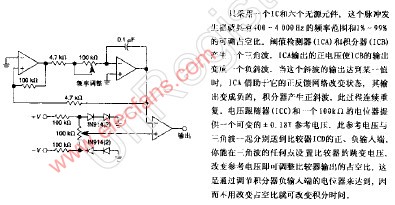

如何利用脈沖序列發生器和積分器構成三角波發生器呢?

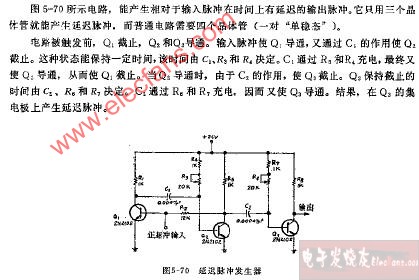

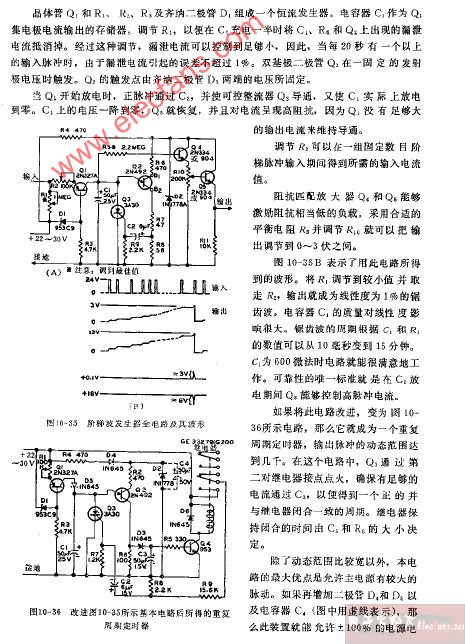

階梯波發生器之二

5342

5342

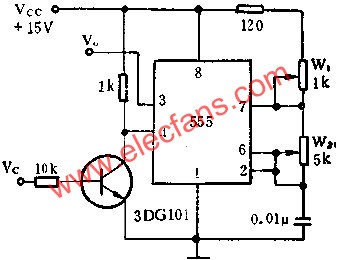

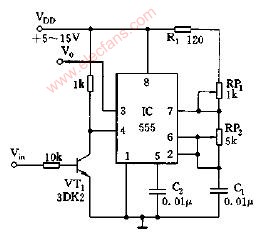

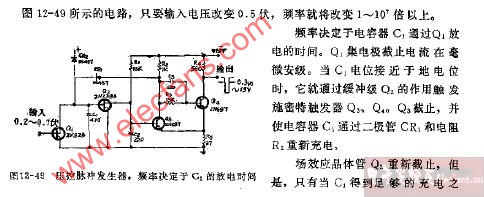

時基集成電路組成開關控制的脈沖發生器電路圖

3529

3529

脈沖信號發生器原理

23381

23381

脈沖碼型發生器工作原理

1725

1725

555脈沖發生器電路圖大全(六款555脈沖發生器電路設計原理圖詳解)

232653

232653

單次脈沖發生器電路圖大全(七款單次脈沖發生器電路設計原理圖詳解)

102482

102482

高壓脈沖發生器電路圖大全(六款等效電路/電子滅蟲燈/脈沖發生器產生)

41609

41609

脈沖信號發生器原理_脈沖信號發生器應用領域

15350

15350

如何使用FPGA實現靜止補償的PWM脈沖發生器設計

24

24脈沖發生器的分類及特點

4780

4780什么是信號發生器 信號發生器類型總結

5862

5862電快速瞬變脈沖群發生器的校準方法

3002

3002

關于脈沖發生器,你知道多少?

6672

6672

脈沖發生器輸出是1嗎?信號發生器怎么只發一個脈沖?

3340

3340脈沖發生器是什么意思?脈沖發生器怎么使用?

5688

5688信號發生器如何發出雙脈沖?

4289

4289脈沖發生器輸出的是什么信號 脈沖信號發生器原理

4257

4257

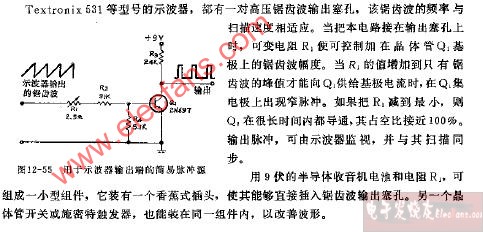

泰克信號發生器脈沖模式應用

1021

1021

電子發燒友App

電子發燒友App

評論