ldo知識總結:影響電源抑制比因素有哪些?

- 開關電源(496617)

- ldo(159374)

- 電源電壓(26211)

- 數據轉換器(30547)

- 電源抑制比(14108)

相關推薦

熱點推薦

LDO 基礎知識:噪聲 - 降噪引腳如何提高系統性能

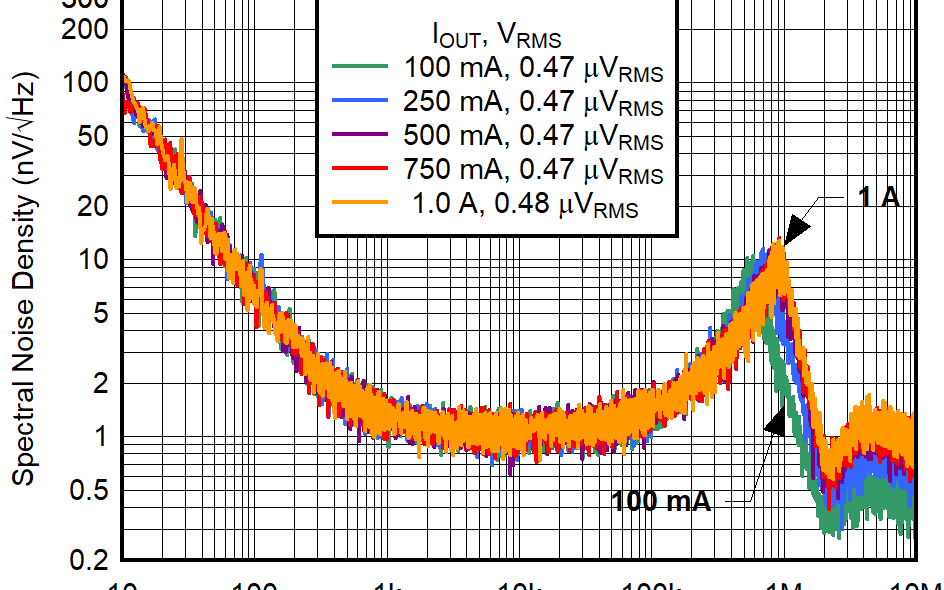

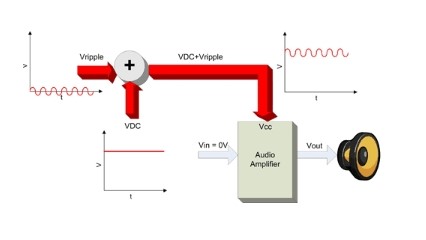

在“LDO基礎知識:電源抑制比”一文中,Aaron Paxton討論了使用低壓降穩壓器 (LDO) 來過濾開關模式電源產生的紋波電壓。然而,這并不是實現清潔直流電源的唯一考慮因素。由于LDO

2022-04-18 18:05:29 6842

6842

6842

6842

LDO在開關電源中的應用

LDO是一種微功耗的低壓差線性穩壓器,它通常具有極低的自有噪聲和較高的電源抑制比PSRR(PowerSupplyRejectionRatio)。

2011-09-29 10:46:00 6193

6193

6193

6193

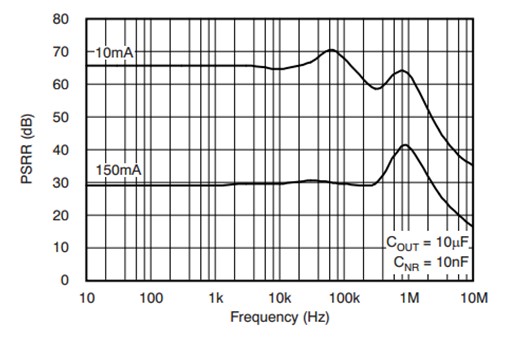

關于LDO基礎知識:電源抑制比

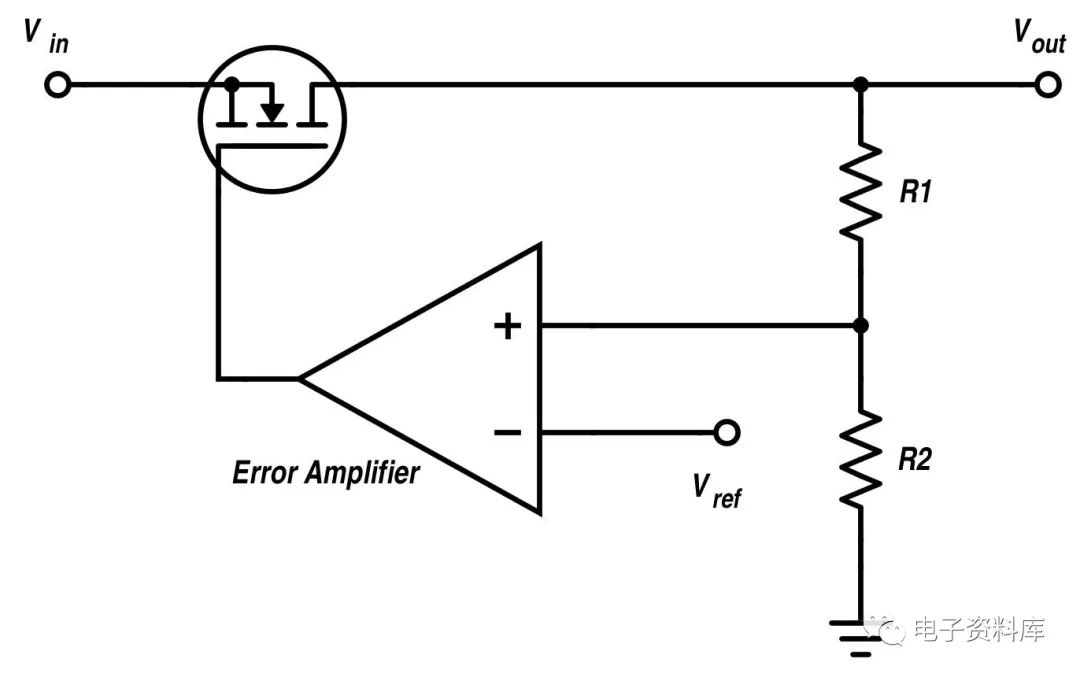

Ramus在博客中介紹了噪音對信號調節設備的不利影響:減少高速信號鏈電源問題。然而,電源抑制比(PSRR)仍然通常被誤認為單一的靜態值。在這篇文章中,我將嘗試說明什么是PSRR以及影響它的變量有哪些。 什么是 PSRR ? PSRR是許多LDO數據手冊中的公

2018-06-28 10:16:00 25787

25787

25787

25787

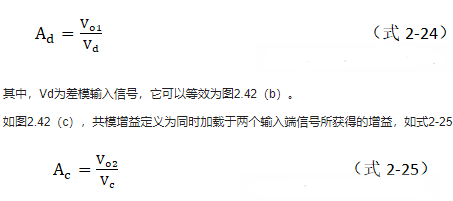

放大器共模抑制比參數定義及影響電路共模抑制的因素分析

的評估方法,不代表可以在應用電路對共模信號實現有效抑制。本篇解析放大器共模抑制比參數定義與其影響的評估方法,以及結合一個實際案例討論影響電路共模抑制的因素。

2020-10-14 16:41:45 13605

13605

13605

13605

一文詳解LDO的電源抑制比

低壓差線性穩壓器(LDO)相比 DC-DC 的優點之一,是輸出電壓紋波小。但是高速電路下,LDO 的電源抑制比(PSRR)也是不可忽略的因素,通常被誤認為是單一的靜態值,本篇文章將詳細講解電源抑制比(PSRR)及如何測量它。

2022-08-30 17:09:25 26513

26513

26513

26513

電源抑制比(PSRR)的基礎知識

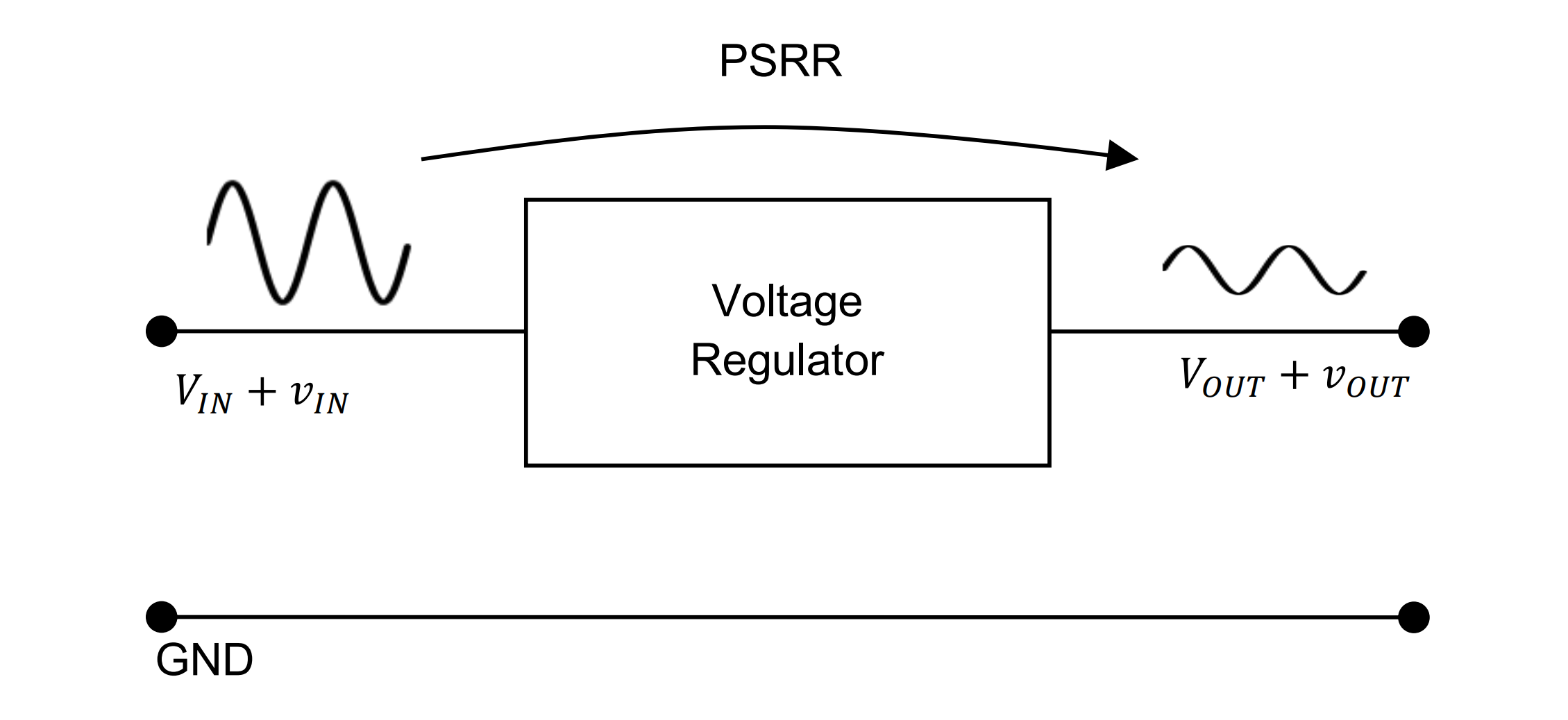

電源抑制比 ,英文名Power Supply Rejection Ratio,簡稱PSRR,它描述了電路抑制任何電源變化傳遞到其輸出信號的能力,通常以dB為單位進行測量,用來描述輸出信號受電源

2022-09-09 15:37:05 40955

40955

40955

40955

什么是LDO?LDO中的噪聲和PSRR介紹

在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩壓器中的影響。讓我們簡要討論一下什么是 LDO。

2023-09-26 14:29:43 6745

6745

6745

6745

什么是LDO?淺析低壓差穩壓器 (LDO) 中的噪聲及電源抑制比

在本文中,我們將介紹低壓差 (LDO) 穩壓器中噪聲和電源抑制比 (PSRR) 的影響。讓我們簡單討論一下什么是 LDO。

2024-03-15 17:12:08 6800

6800

6800

6800

LDO的電源抑制比測量

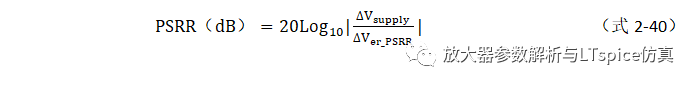

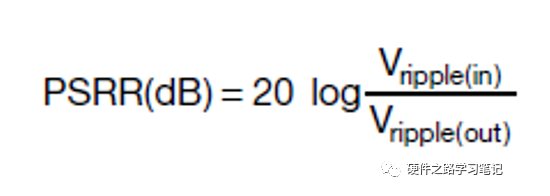

作者:Hao Wang深圳模擬工程師PSRR是什么PSRR(Power supply rejection ratio)又稱電源抑制比,是衡量電路對于輸入電源中紋波抑制大小的重要參數,表示為輸出紋波

2019-03-20 06:45:01

LDO的PSRR該如何測量呢

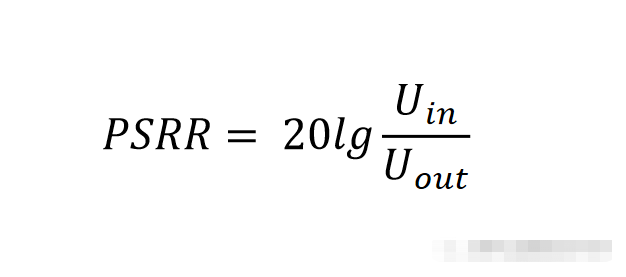

PSRR(Power supply rejection ratio)又稱電源抑制比,是衡量電路對于輸入電源中紋波抑制大小的重要參數,表示為輸出紋波和輸入紋波的對數比,單位為分貝(dB)[1],其

2022-11-11 06:09:55

電源抑制比

電源抑制比(PSRR),電源抑制比(PSRR)是什么意思關鍵字:電源抑制比(PSRR),電源抑制比(PSRR)是什么意思電源抑制比電源抑制比(Power Supply Rejection Ratio

2025-04-08 13:30:34

電源抑制比提高

現在正做一個折疊式共源共柵放大器的設計,性能指標增益和電源抑制比不能同時達到要求,各位大神幫忙告訴我怎么提高電源抑制比?另外,抑制電路到底是什么啊?最好有圖呈現,謝謝了!

2016-05-27 13:52:28

電源抑制比是如何去定義的

電源抑制比電源抑制比(Power Supply Rejection Ratio):把電源的輸入與輸出看作獨立的信號源,輸入與輸出的紋波比值即是PSRR,通常用對數形式表示,單位是dB。 PSRR=20log{[ripple(in)/...

2021-12-31 07:03:52

電源抑制比是如何去定義的

{cc}ΔVcc?,輸入失調電壓變化ΔVos\Delta V_{os}ΔVos?,定義電源抑制比PSRR=20lg?(ΔVcc/ΔVos)PSRR = 20\lg (\Delta V_{cc}/\Delt...

2021-12-27 06:07:54

電源電壓抑制比(PSRR)是什么意思

如果運算放大器的電源發生變化,輸出不應變化,但實際上通常會發生變化。如果X V的電源電壓變化產生Y V的輸出電壓變化,則該電源的PSRR(折合到輸出端)為X/Y。無量綱比通常稱為電源電壓抑制比

2021-12-27 08:15:06

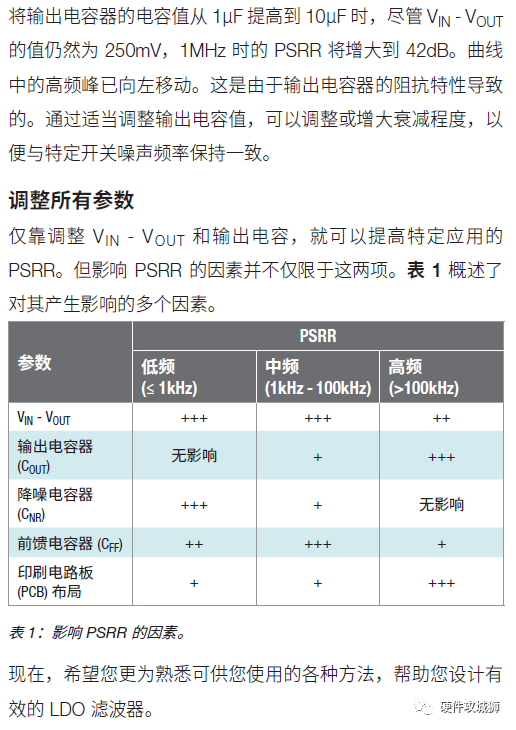

低壓降穩壓器參數和電源抑制比特性,是如何受到應用條件影響的?

我們將重點談談低壓降穩壓器(LDO)參數和電源抑制比(PSRR)特性,以及它如何受到應用的條件影響。

2021-03-17 07:55:31

共模抑制比CMRR與電源抑制比PSRR相關介紹

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2021-12-27 07:24:51

共模抑制比和電源抑制比區別

讀論文analysis of switched-capacitor commom-mode feedback circuit1.與單端輸出相比,全差分電路有更好的共模抑制比和電源抑制比。2.共模環路

2021-10-29 07:10:25

關于ldo的紋波抑制比 精選資料分享

近期,項目遇到的問題,不得不考慮ldo的紋波抑制比問題,在選型時,確實沒有仔細研究,咨詢所選電源芯片的廠家后,才得知,自己選的這個芯片,紋波抑制不是很好。具體什么是紋波抑制比,腦子里倒是有,還是準確

2021-07-30 06:38:39

如何理解運放的電源抑制比參數?

電源抑制比PSRR有三個參數,如OPA333

1、電源抑制比為1uV/V

2、長期穩定性為1uV

3、通道分離,直流為0.1uV/V

特別是3號參數,怎么理解

2024-08-12 06:37:41

開關電源和LDO設計

能力的LDO的電源抑制比在100KHz以上都不太好開關電源如果選用類似LM2596這樣的芯片,看到紋波輸出大概在150KHz以上,求大神指點迷津,開關電源的紋波和噪聲可以抑制到什么程度呢?可不可以不用開關電源,直接用LDO來抑制適配器的噪聲呢?開關電源芯片有沒有開關頻率比較低的呢?

2014-04-22 22:30:52

影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

此電路用來檢測腦電波的信號,性能要求此電路的共模抑制比要達到不低于80dB,而現在實測只能達到67dB,想知道,影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

2024-08-20 07:21:02

放大器電源抑制比與頻率的影響,工程師都該了解

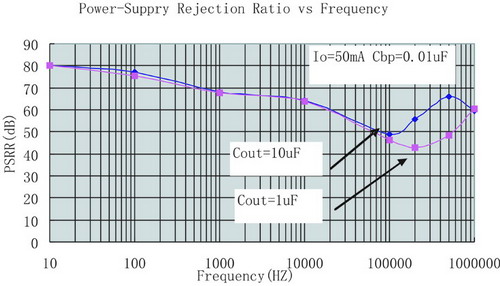

的 LDO 1117 電源抑制比與頻率關系,可見 1117 在 1KHz 處電源抑制比最強,達到 84dB,頻率為 100KHz 的電源抑制比僅為 40dB,高于 100KHz 的電源抑制比性能沒有提供

2020-11-24 09:20:54

放大器的電源抑制比和共模抑制比

電源或共模電壓變化產生的失調偏移時很容易產生困惑。這種困惑的根本原因如下圖所示:圖 1:儀表放大器的典型電源抑制比曲線在圖 1 中,放大器的電源抑制比 (PSRR) 隨放大器增益配置的升高而增加。這樣很

2018-09-19 11:00:26

模擬電源被數字電源取代的因素有哪些?

數字控制能解決問題,是因為它具有比模擬控制更好的性能、更靈活且在復雜的設計中更易用。然而下面總結的六個方面是決定了模擬電源被數字電源取代的主要因素。

2021-03-16 10:46:33

設計電路時LDO穩壓器要考慮的因素

=Vin-Vout,這個差值不能太大,要不然穩壓精度會受到影響,可以看出LDO只能降壓而不能升壓; 3、噪聲 噪聲其實是一個統稱,是衡量一款電源產品優秀的重要參考因素,它里面包含耦合、諧振等; 4、紋波抑制比 電源變化量與輸出變化量的比值,是輸出信號受電源影響比值,反映LDO抑制信號源的能力。

2020-06-28 14:53:05

具有高電源抑制比性能的線性穩壓器

具有高電源抑制比性能的線性穩壓器

低壓降穩壓器(LDO)主要用于產生供音頻和射頻電路使用的低紋波、低噪聲電源,也可以作為頻率合成器和VCO的局部純凈電源。一般

2010-01-14 16:54:00 921

921

921

921

共模抑制比,共模抑制比是什么意思

共模抑制比,共模抑制比是什么意思

共模抑制比的定義

為了綜合評價差動放大電路對共模信號的抑制能力和對差模信號的放大能力,特

2010-03-09 16:36:11 14810

14810

14810

14810電源抑制比(PSRR),電源抑制比(PSRR)是什么意思

電源抑制比(PSRR),電源抑制比(PSRR)是什么意思

電源抑制比

電源抑制比(Power Supply Rejection Ratio):把電源的輸入與輸出看作獨

2010-03-09 16:41:06 16320

16320

16320

16320RF電路中LDO電源抑制比和噪聲原理及選擇

RF電路中LDO電源抑制比和噪聲原理及選擇

本文討論LDO的特點以及RF電路對LDO的電源抑制比和噪聲的選擇。引言便攜產品電源設計需

2010-03-09 16:51:32 2972

2972

2972

2972

LDO應用的考量因素

1、選擇 LDO的基本要素

包括輸入電壓范圍、預期輸出電壓、負載電流范圍以及其封裝的功耗能力。此外,地腳電流 Ignd 或靜態電流 Iq、電源波紋抑制比 PSRR、噪聲及

2010-08-27 11:31:33 1282

1282

1282

1282電源抑制比提高電路圖

由ISO124與MC78L05、MC79L05和DCP011515構成的外部調整器提高電源抑制比(PSR)的電路。利用MC78L05和MC79L05作為輔助穩壓調整,使得在不減小±10V輸入范圍條件下可以降低電源抑制比誤差。

2011-08-31 15:35:57 2232

2232

2232

2232

LDO應用的考量因素

包括輸入電壓范圍、預期輸出電壓、負載電流范圍以及其封裝的功耗能力。此外,地腳電流 Ignd 或靜態電流 Iq、電源波紋抑制比 PSRR、噪聲及封裝等也是 LDO 選擇時的應關注的因素。

2011-11-01 11:55:34 1295

1295

1295

1295高電源抑制比無片外電容LDO設計

模塊對外部電源進行處理,得到模塊所需性能標準的電壓。 設計了一種可用于射頻前端芯片供電的高電源抑制比(PSR)無片外電容CMOS低壓差線性穩壓器(LDO)。基于對全頻段電源抑制比的詳細分析,提出了一種PSR增強電路模塊,使100

2018-02-23 11:41:48 0

0

0

0電源抑制比的基本知識及如何降低噪音

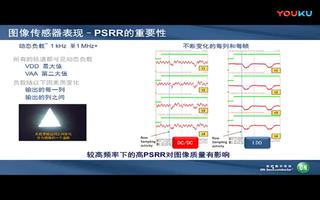

視頻簡介:圖像傳感器的圖像質量直接受到高頻、高PSRR LDO穩壓器的影響。本網上廣播講解電源抑制比(PSRR)的基本知識,以及在您的圖像傳感器設計中如何最大程度地降低噪聲。

2019-03-14 06:10:00 6191

6191

6191

6191

放大器電源抑制比參數的評估方法

放大器電源抑制比參數對電路的影響與共模抑制比參數的影響近似,因為來自電源線路的噪聲對于放大器而言可視為共模噪聲。本篇介紹放大器電源抑制比參數的評估方法,并通過LTspice仿真參數測量電路。 電源

2020-12-06 10:22:00 4961

4961

4961

4961LT3094演示電路-超低噪聲、超高電源抑制比負LDO穩壓器(-20V至-3.3V@500 mA)

LT3094演示電路-超低噪聲、超高電源抑制比負LDO穩壓器(-20V至-3.3V@500 mA)

2021-03-23 14:27:09 28

28

28

28影響電源壽命的因素有哪些

電解電容之所以能夠廣泛適用于各種電子產品,主要是靠著能夠調整電壓的濾波。在進行開關電源的預前計時,就需要通過解析樣本結果來驗證影響電源壽命的因素有哪些,所以了解電源開關內部結構是非常重要。

2021-04-16 13:50:35 2185

2185

2185

2185ADM7172:6.5 V,2 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

ADM7172:6.5 V,2 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-14 17:01:48 6

6

6

6ADM7170:6.5 V,500 mA,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

ADM7170:6.5 V,500 mA,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-21 19:19:34 7

7

7

7ADM7171:6.5 V,1 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

ADM7171:6.5 V,1 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-21 19:33:05 12

12

12

12LDO_DCDC基礎知識

LDO_DCDC基礎知識(深圳市核達中遠通電源技術有限公司簡介)-文檔為LDO_DCDC基礎知識總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-22 11:23:57 50

50

50

50電源抑制比(PSRR )

如果運算放大器的電源發生變化,輸出不應變化,但實際上通常會發生變化。如果X V的電源電壓變化產生Y V的輸出電壓變化,則該電源的PSRR(折合到輸出端)為X/Y。無量綱比通常稱為電源電壓抑制比

2022-01-05 14:11:14 11

11

11

11共模抑制比CMRR與電源抑制比PSRR的仿真原理

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2022-01-05 14:22:58 6

6

6

6什么是電源抑制比(PSRR)

原文鏈接: http://www.3532n.com/baike/bandaoti/jichuzhishi/20100309184356.html電源抑制比電源抑制比(Power

2022-01-11 10:05:06 8

8

8

8什么是電源抑制比參數影響評估與測試電路仿真

放大器電源抑制比參數對電路的影響與共模抑制比參數的影響近似,因為來自電源線路的噪聲對于放大器而言可視為共模噪聲。本篇介紹放大器電源抑制比參數的評估方法,并通過LTspice仿真參數測量電路。

2023-02-22 14:20:44 3679

3679

3679

3679

運放的直流電源抑制比

電源抑制比的概念,接觸過運放的讀者應該知道,指的是運放對電源噪聲或者紋波的抑制能力,噪聲和紋波是交流的,所以運放的電源抑制比一般指的是AC PSRR。但是什么又是運放的直流電源抑制比(DC_PSRR)呢?是指運放供電電壓的變化,引起運放輸入失調電壓的變化,這兩個變化之比就是運放的直流電源抑制比。

2023-03-17 15:52:46 3346

3346

3346

3346

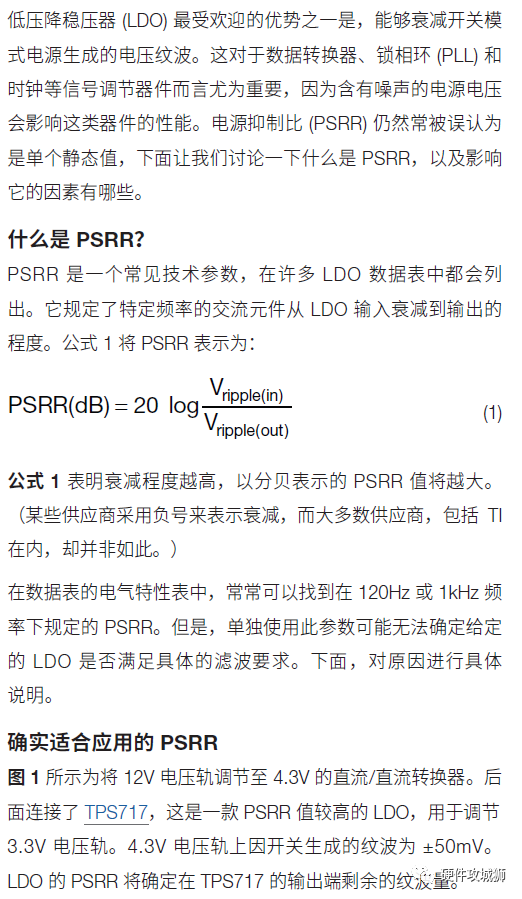

LDO基礎知識:電源抑制比

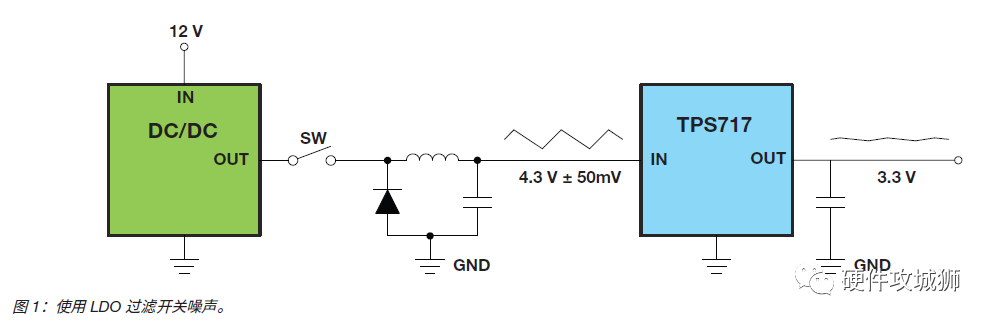

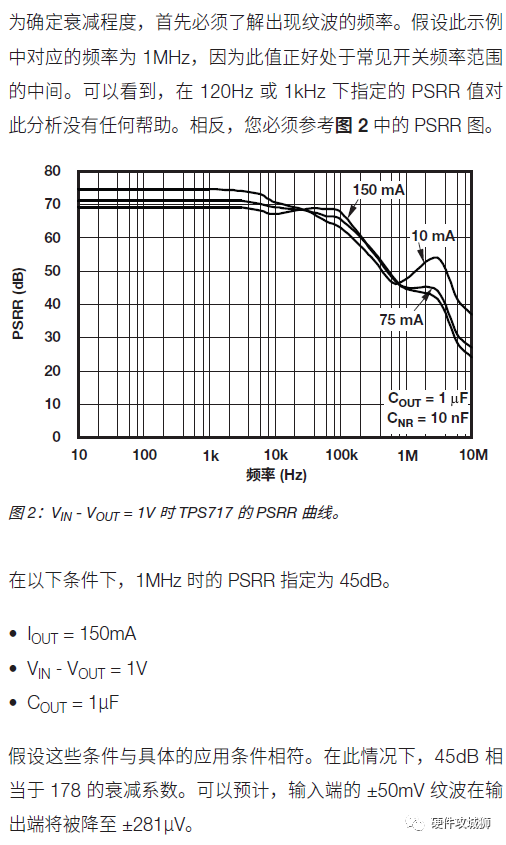

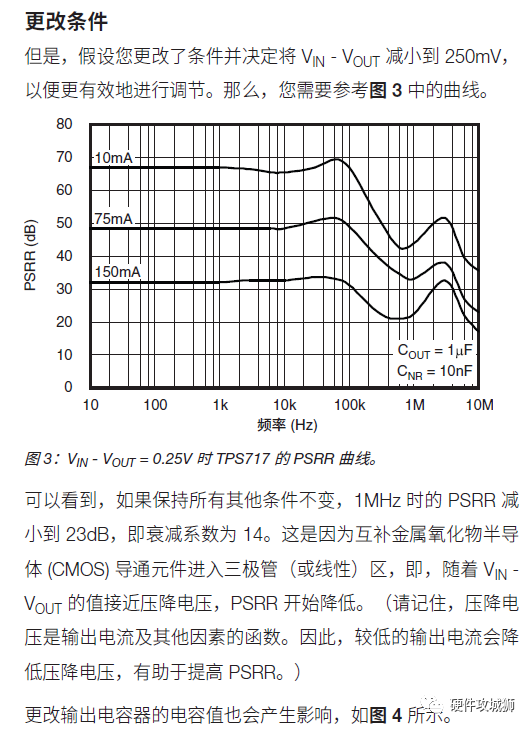

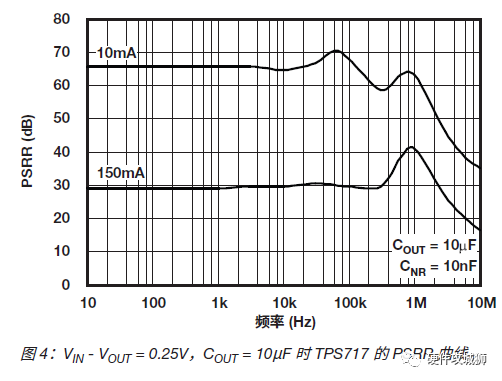

低壓差線性穩壓器(LDO)最大的優點之一是它們能夠衰減開關模式電源產生的電壓紋波。這對鎖相環(PLL)和時鐘等信號調節器件在內的數據轉換器尤為重要,因為噪聲電源電壓會影響性能。電源抑制比(PSRR)仍然通常被誤認為單一的靜態值。在這篇文章中,我將嘗試說明什么是PSRR以及影響它的變量有哪些。

2023-04-04 10:25:33 2418

2418

2418

2418電源抑制比簡述

電源抑制比又叫做電源紋波抑制比(power supply rejection ratio)簡稱PSRR。不少電源芯片手冊中有此參數,比如LDO芯片,很多人在閱讀LDO手冊的時候忽略了此參數,其實這個

2023-04-24 12:57:43 10571

10571

10571

10571

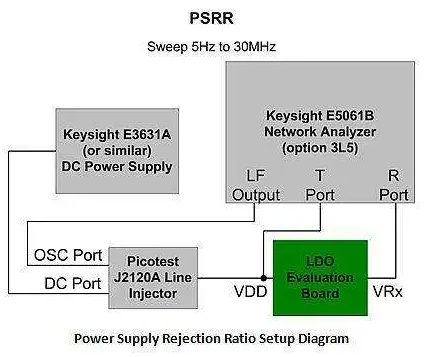

測量新手的LDO電源抑制比

為了在LDO上執行PSRR測量,需要兩臺設備。第一種是直流電源,用于為 LDO 輸入電壓供電。再次使用是德科技 (安捷倫) E3631A 直流電源。第二款也是最重要的設備是德科技 E5061B

2023-06-30 14:54:48 2555

2555

2555

2555

電源抑制比是什么意思?電源抑制比怎么提高?

電源抑制比是什么意思?電源抑制比怎么提高? 一、電源抑制比的概念 電源抑制比(PSRR)又稱電源噪聲抑制比,是指在電路中,當電源發生噪聲時,電路輸出端對電源噪聲的抑制程度,一般使用分貝(dB)單位

2023-09-02 17:50:32 9857

9857

9857

9857什么是共模抑制比CMRR?什么是電源抑制比PSRR?

什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和電源抑制比(power supply rejection

2023-10-29 11:45:48 10802

10802

10802

10802影響共模抑制比的主要因素 如何提高共模抑制比?

能夠有效抑制共模干擾,提高信號傳輸質量。影響共模抑制比的主要因素有系統設計、電路拓撲、濾波器設計、地線布局等。 首先,系統設計是影響共模抑制比的關鍵因素之一。在系統設計過程中,合理地選擇合適的工作電壓范圍、工作

2023-11-08 17:46:26 3550

3550

3550

3550電源抑制比怎么提高

電源抑制比怎么提高? 電源抑制比是衡量電源噪聲抑制效果的重要指標。提高電源抑制比可以有效降低電源噪聲對電子設備的影響,提升設備的穩定性和性能。本文將從信號處理、濾波器設計、抑制電路、電源線布局等多個

2023-12-12 14:33:28 1552

1552

1552

1552什么是電源抑制比(PSRR)?它有哪些作用和應用?

在電子設備和系統的設計中,電源抑制比(Power Supply Rejection Ratio,簡稱PSRR)是一個至關重要的參數。它描述了電子設備或系統對來自電源的噪聲和干擾的抑制能力。本文將詳細探討電源抑制比的概念、計算方法、作用及其在電子設備設計中的應用,以期為讀者提供全面的理解和深入的見解。

2024-05-24 14:31:29 8058

8058

8058

8058LDO電源抑制比的測量方法

LDO電源抑制比(PSRR,Power Supply Rejection Ratio)是衡量線性穩壓器(LDO)在電源電壓變化時對輸出電壓穩定性的影響的一個重要指標。 一、LDO電源抑制比的概念

2024-07-14 10:14:09 2434

2434

2434

2434詳解LDO電路的電源抑制比

電源抑制(Power Supply Rejection)能力是SoC系統中電源模塊很重要的指標,在當今數字和模擬電路高度集成的趨勢下,一個能提供穩定輸出電壓的系統模塊顯得尤為重要,而這個模塊又很容易受到供電電源的噪聲和紋波影響,電源抑制能力描述的就是對這一類影響的抑制能力。

2024-11-09 17:30:39 2178

2178

2178

2178 電子發燒友App

電子發燒友App

評論