電源抑制比是什么意思?電源抑制比怎么提高?

一、電源抑制比的概念

電源抑制比(PSRR)又稱電源噪聲抑制比,是指在電路中,當(dāng)電源發(fā)生噪聲時(shí),電路輸出端對(duì)電源噪聲的抑制程度,一般使用分貝(dB)單位表示。電源噪聲多數(shù)來(lái)自于電源線路中的電感、電容、功率管等組件,在電路工作過(guò)程中,電源信號(hào)可能發(fā)生抖動(dòng),從而產(chǎn)生對(duì)電路各個(gè)部分的影響,導(dǎo)致電路輸出端的干擾和誤差。

二、電源抑制比的意義

在很多應(yīng)用中,大部分精度和帶寬實(shí)際上都由電源噪聲抑制比所決定,因?yàn)殡娫丛肼曇种票雀撸湍鼙WC電路輸出端的干擾和誤差較小,成為保證電路穩(wěn)定可靠工作的重要因素。例如在高性能模擬轉(zhuǎn)換器中,需要對(duì)輸入信號(hào)進(jìn)行高精度轉(zhuǎn)換,而轉(zhuǎn)換器的輸出端即為整個(gè)系統(tǒng)的響應(yīng),如果電源噪聲抑制比太低,將會(huì)引入電源噪聲干擾,從而導(dǎo)致系統(tǒng)精度下降。因此,提高電源噪聲抑制比是提高系統(tǒng)性能和輸出信號(hào)質(zhì)量的重要手段。

三、電源抑制比的影響因素

1、電源噪聲的頻率范圍:在電源噪聲的頻率范圍內(nèi),電源抑制比會(huì)逐漸降低或變化。在工作頻率范圍內(nèi),電路對(duì)電源噪聲的抑制能力會(huì)不斷增加,但超出該范圍,抑制能力會(huì)降低或失效。

2、電源線路的阻抗匹配:當(dāng)電源線路的阻抗與負(fù)載端的阻抗不匹配時(shí),會(huì)導(dǎo)致電源噪聲抑制比下降。電源線路應(yīng)該采用合適的電源濾波器,使得電源輸出端的阻抗和負(fù)載端的阻抗匹配,以提高電源噪聲抑制比。

3、電源線路的穩(wěn)定性:電源線路的穩(wěn)定性也會(huì)影響電源噪聲抑制比。如果電源線路內(nèi)部存在電流過(guò)大、功率管損壞等情況,將導(dǎo)致電源抑制比下降或失效。

四、電源抑制比的提高方法

1、使用低噪聲線性穩(wěn)壓電源

線性穩(wěn)壓電源比開(kāi)關(guān)穩(wěn)壓電源更具有穩(wěn)定性,能夠提供更加穩(wěn)定、低噪聲的電源,從而提高電路的穩(wěn)定性和電源抑制比。

2、使用合適的電源濾波器

電源濾波器主要是利用電感和電容的濾波特性,將電源信號(hào)中的高頻噪聲濾除。在設(shè)計(jì)電源濾波器時(shí),需要根據(jù)工作頻率和所需抑制比進(jìn)行參數(shù)選擇,消除電源噪聲的影響,提高電路的穩(wěn)定性和輸出信號(hào)質(zhì)量。

3、合理布線

在抑制電源噪聲方面,合理的布線設(shè)計(jì)也非常重要。關(guān)鍵信號(hào)線路需要設(shè)備地面共模抑制(CMRR)和差分模式噪聲抑制(DMRR)電路的支持。同時(shí),還要注意降低電源線路的電阻和電抗,以減少電源噪聲的穿透和影響。

總之,提高電源抑制比可以有效消除電源噪聲對(duì)電路的干擾和影響,提高系統(tǒng)的性能和精度,因此需要在設(shè)計(jì)和選型方面,重視電源噪聲抑制比的影響,采取相應(yīng)的措施提高電源噪聲抑制比。

-

DMR

+關(guān)注

關(guān)注

1文章

35瀏覽量

14029 -

電源抑制比

+關(guān)注

關(guān)注

0文章

78瀏覽量

14102 -

PSRR

+關(guān)注

關(guān)注

0文章

225瀏覽量

40628 -

線性穩(wěn)壓電源

+關(guān)注

關(guān)注

3文章

60瀏覽量

12849 -

電源濾波器

+關(guān)注

關(guān)注

6文章

493瀏覽量

25852

發(fā)布評(píng)論請(qǐng)先 登錄

在移動(dòng)電源應(yīng)用中,電容的高容值和低ESR,哪個(gè)對(duì)抑制紋波更重要?

有沒(méi)有相關(guān)標(biāo)準(zhǔn)或規(guī)范來(lái)規(guī)定隔離模塊的調(diào)整率和紋波抑制比?

什么是共模抑制比?

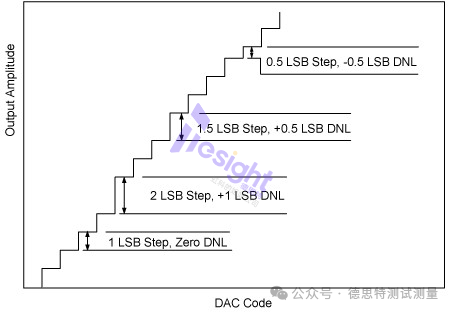

從偏移誤差到電源抑制比,DAC核心術(shù)語(yǔ)全解析

海洋儀器電源抑制比測(cè)試方案26800元起

DCDC電源模塊的噪聲抑制方法

開(kāi)關(guān)電源的共模干擾抑制技術(shù)|開(kāi)關(guān)電源共模電磁干擾(EMI)對(duì)策詳解

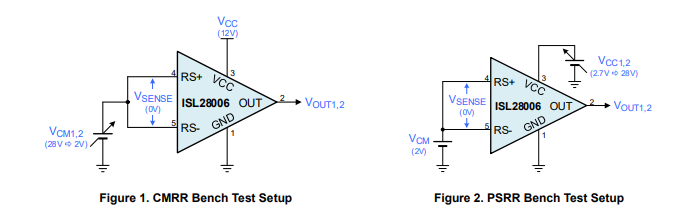

ISL28006:測(cè)量共模和電源抑制比

如何評(píng)估電源濾波器對(duì)瞬態(tài)干擾的抑制能力?

電源模塊的EMC設(shè)計(jì)與干擾抑制技術(shù)

電源濾波器的差模抑制能力會(huì)受哪些因素影響

如何使用開(kāi)關(guān)浪涌抑制器替代傳統(tǒng)的線性浪涌抑制器

電源抑制比是什么意思?電源抑制比怎么提高?

電源抑制比是什么意思?電源抑制比怎么提高?

評(píng)論