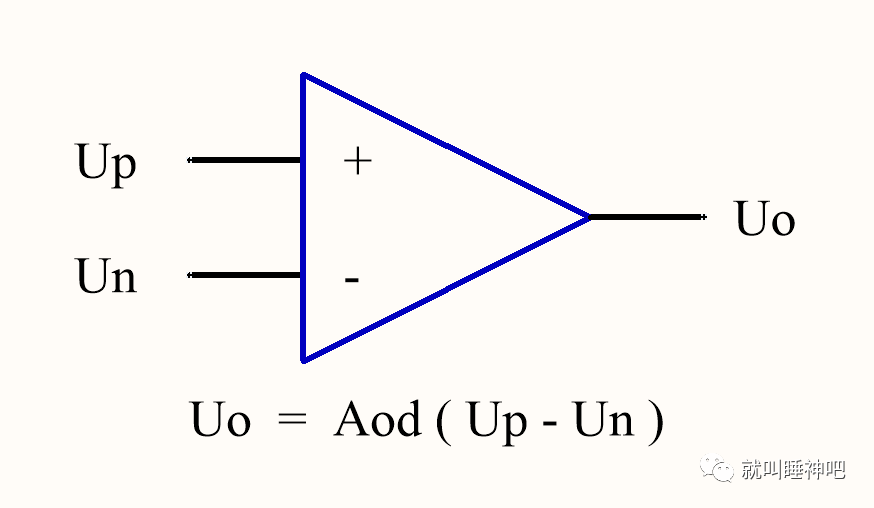

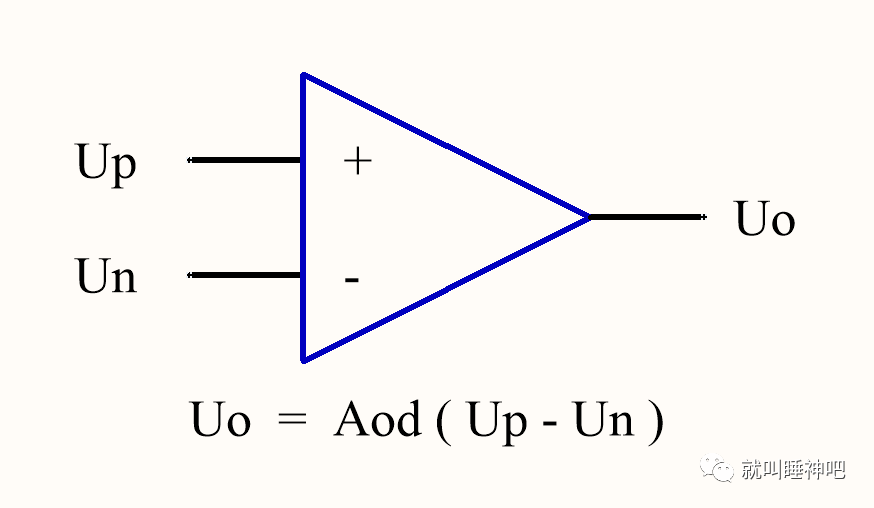

運放的共模抑制比 (CMRR) 是一個重要參數,它表示運放抑制共模信號對運放輸出影響的能力。理想的運算放大器應具有無限大的CMRR,也就是說當運放的兩個輸入具有相同的電壓時,則放大器的輸出應該為零

2024-10-21 11:12:13 13383

13383

為了提高電路的共模抑制比,常采用對消驅動電路(右腿驅動)來提高共模抑制比,本文分析了對消驅動電路的原理,結合實際電路實際驗證了電路的效果。

2012-02-02 11:20:15 3869

3869

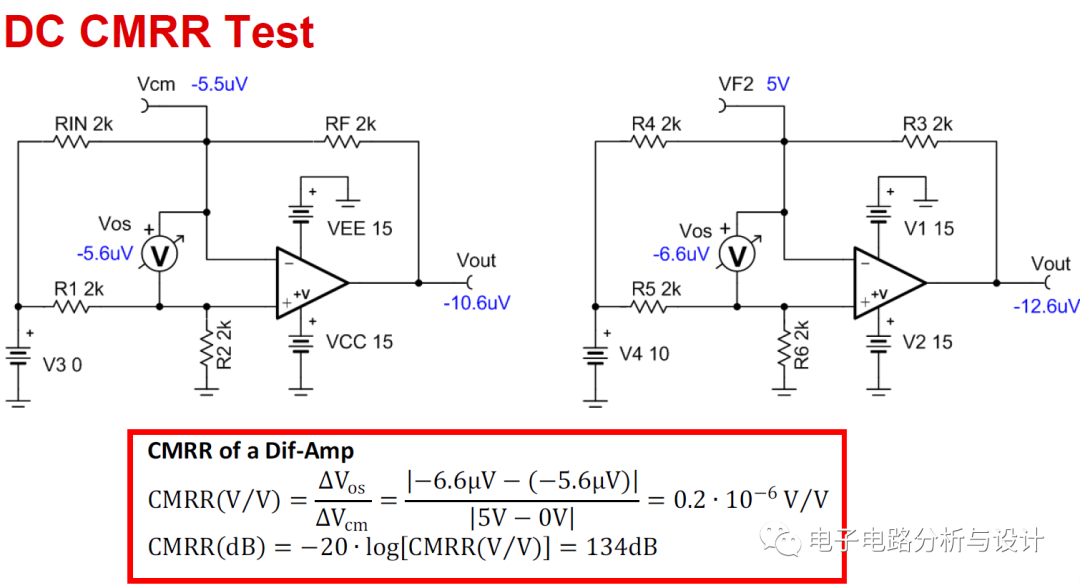

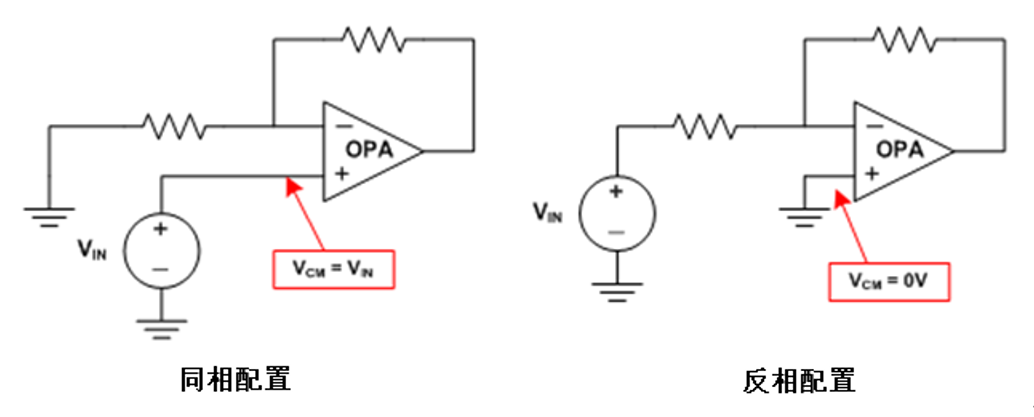

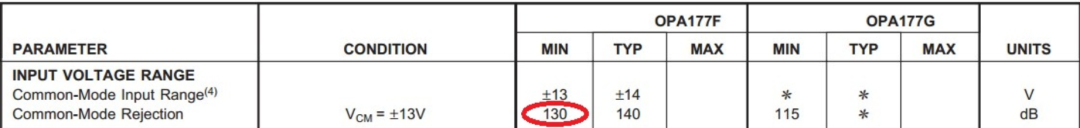

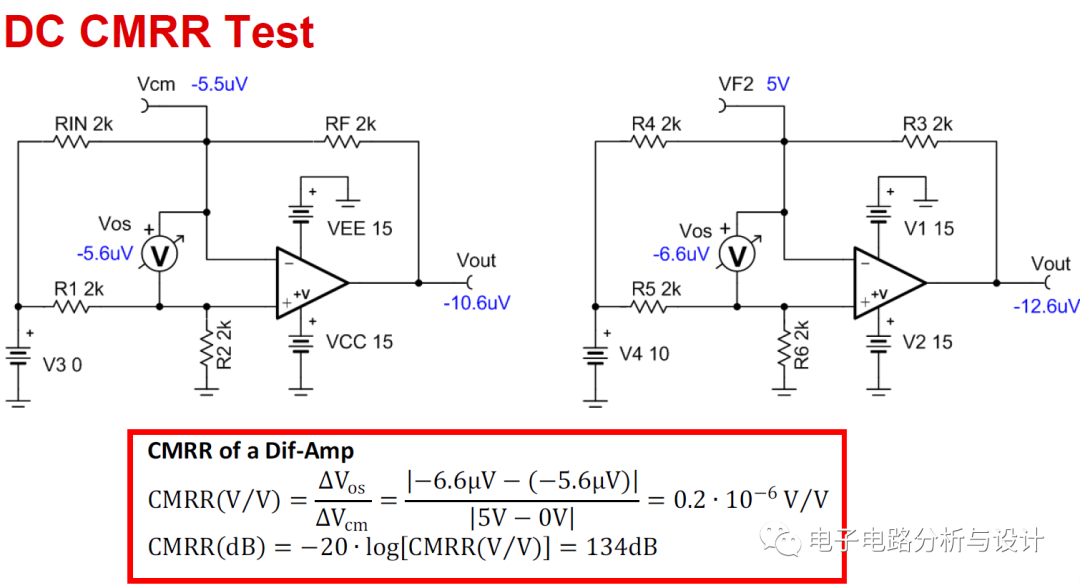

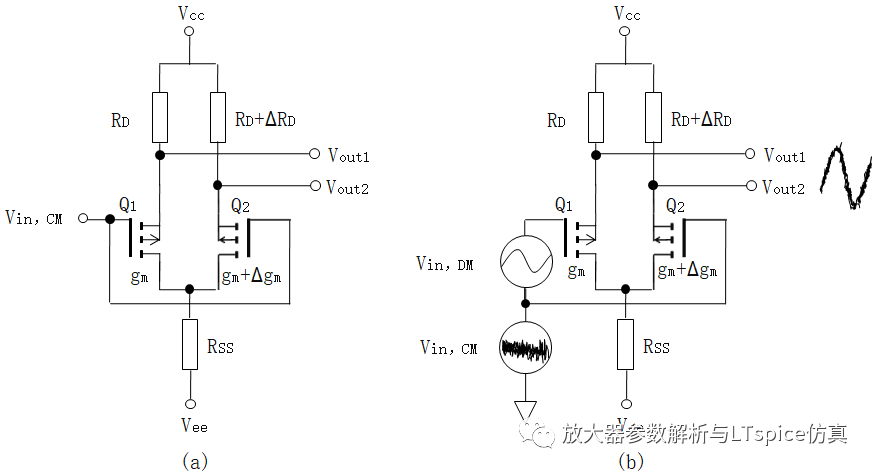

的評估方法,不代表可以在應用電路對共模信號實現有效抑制。本篇解析放大器共模抑制比參數定義與其影響的評估方法,以及結合一個實際案例討論影響電路共模抑制的因素。

2020-10-14 16:41:45 13606

13606

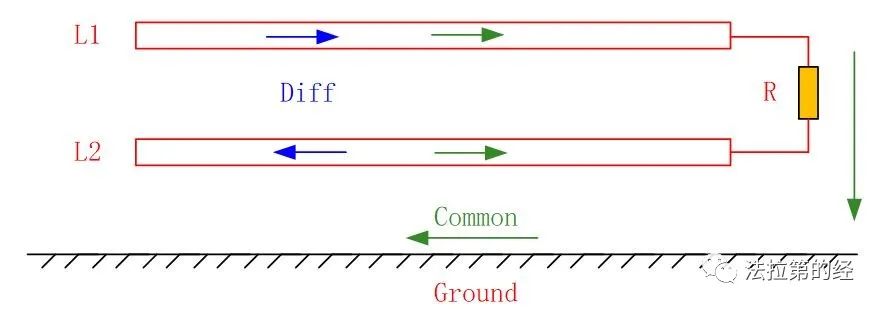

共模抑制比(CMRR)是最重要的規格參數,它表示將要測量的共模信號量。CMMR的值經常取決于信號頻率和指定的功能。CMMR功能專門用于降低傳輸線上的噪聲。例如,當在嘈雜的環境中測量熱電偶的電阻時,來自環境的噪聲表現為兩條輸入引線上的偏移,并使其成為共模電壓信號,CMRR儀器測量應用于噪聲的衰減。

2022-08-30 17:21:05 15546

15546

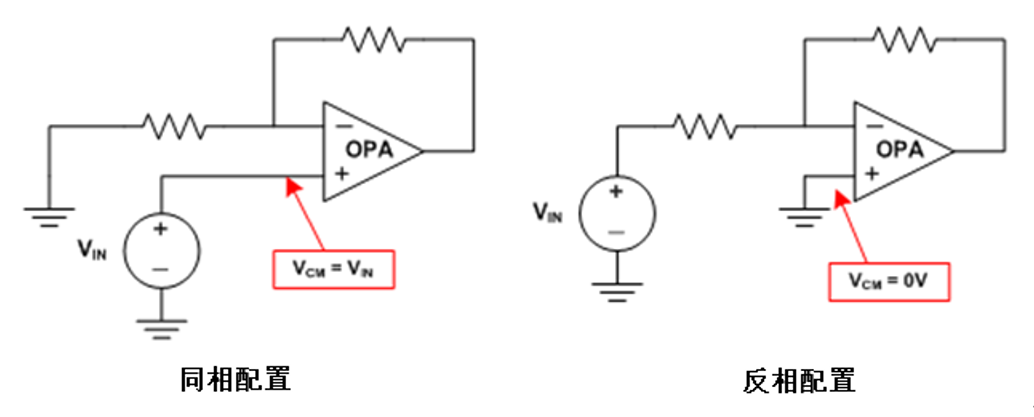

在運放的使用中,最初級的硬件設計者的想法就是只有增益倍數這一個參數。當然這是運放的基本能力,但是顯然只知道放大倍數是不能說其會使用運放的。或許你知道運放,知道差分放大是放大差分信號的,甚至還知道共模抑制比。那么,今天來聊聊共模電平對于運放以及信號系統的意義。

2022-09-21 17:19:10 3082

3082 很多用戶對運放器件自身的CMRR值比較在意,實際上在外部電阻精度只有1%或者更差時,運放器件自身CMRR值對電路整體CMRR值的降低程度已經可以忽略不計了。

2022-10-10 18:17:50 4683

4683 實際上,共模電壓的變化會引起輸出變化。 運算放大器共模抑制比(CMRR)是 指共模增益與差模增益的比值。

2023-02-12 17:08:42 7038

7038

在選型運算放大器時,不少工程師朋友片面追求運放器件自身的CMRR參數,而忽視了電路整體的CMRR。

2023-05-18 16:45:37 6066

6066

特性而引入的計算誤差。國內模電書與國外相關書籍(包括運放數據手冊)在一些參數符號上的表示習慣不同,比如輸入失調電壓和共模抑制比,模電書里一般用Uio和Kcmr表示,而數據手冊則通常用Vos和CMRR表示,這里統一用模電書里的符號表示。

2023-07-26 15:02:12 7828

7828

在高壓差分探頭的設計和應用中共模抑制比(Common Mode Rejection Ratio,簡稱CMRR)是一個重要的性能指標。CMRR代表了差分信號和共模信號之間的差異,量化了探頭能夠抵抗共模

2023-08-09 09:41:30 1504

1504

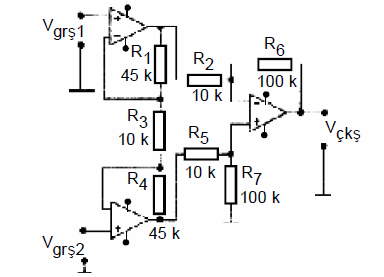

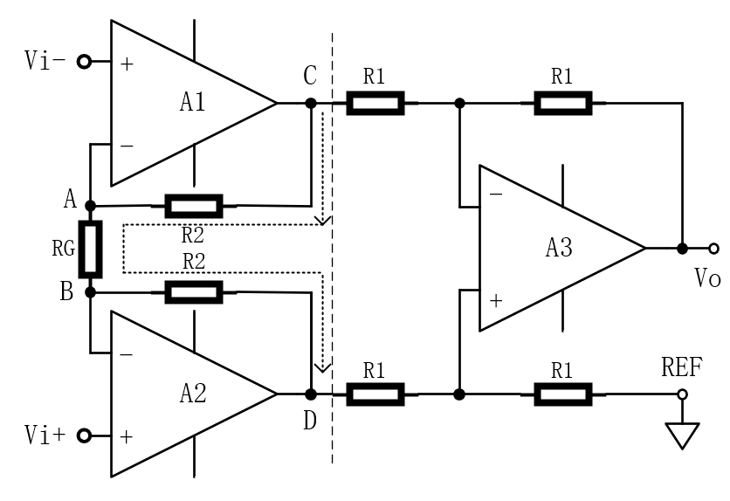

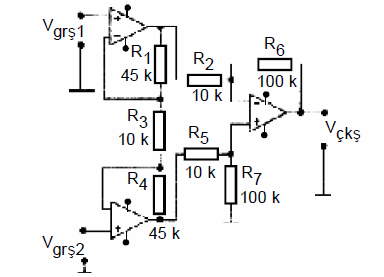

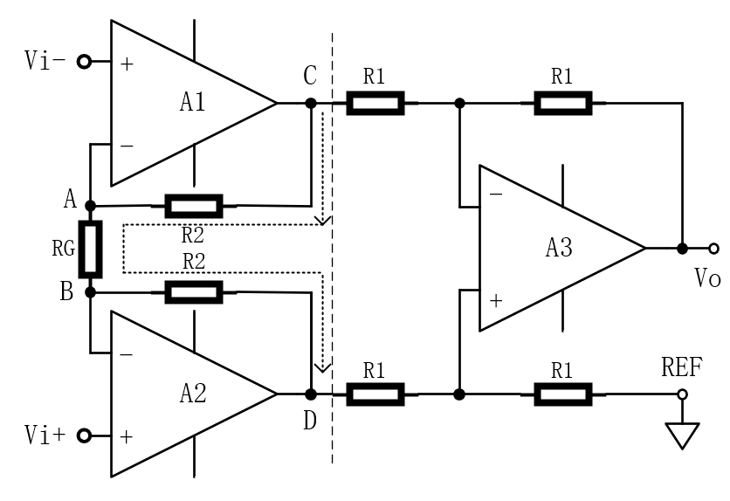

在儀表放大器中,高共模抑制比 (CMRR) 是一個理想的屬性,因為它允許精確的差分信號放大,同時抑制共模噪聲。我們將在這篇文章中討論高 CMRR 儀表放大器的電路原理圖。

2023-08-09 15:39:10 6298

6298

在開始討論運放的共模抑制比CMRR之前,我們先了解一下運放的共模輸入電壓和軌對軌運放。

2023-11-02 10:20:11 9676

9676

一、什么是共模抑制比?共模抑制比(CMRR)是衡量放大器對共模信號抑制能力的一個關鍵指標,是用來描述設備抵御共模信號影響的能力。共模信號是指同時存在于兩個輸入端并具有相同大小和相位的信號,例如電源

2024-06-04 08:10:46 6434

6434

號,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調電壓,失調電流通常是我們關注的參數,然而還有一個非常重要的參數,CMRR,共模抑制比也會對儀表放大器的精度造成

2022-11-14 06:20:19

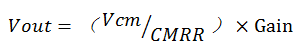

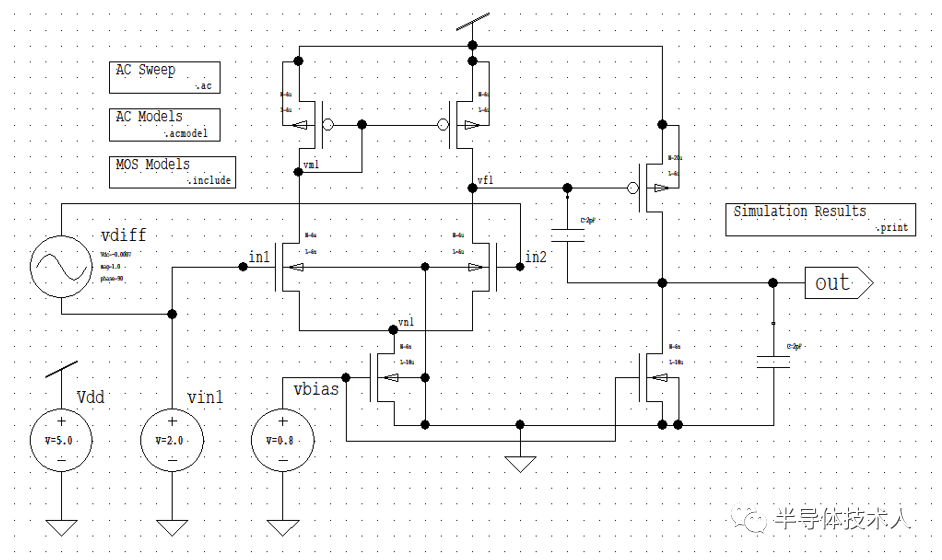

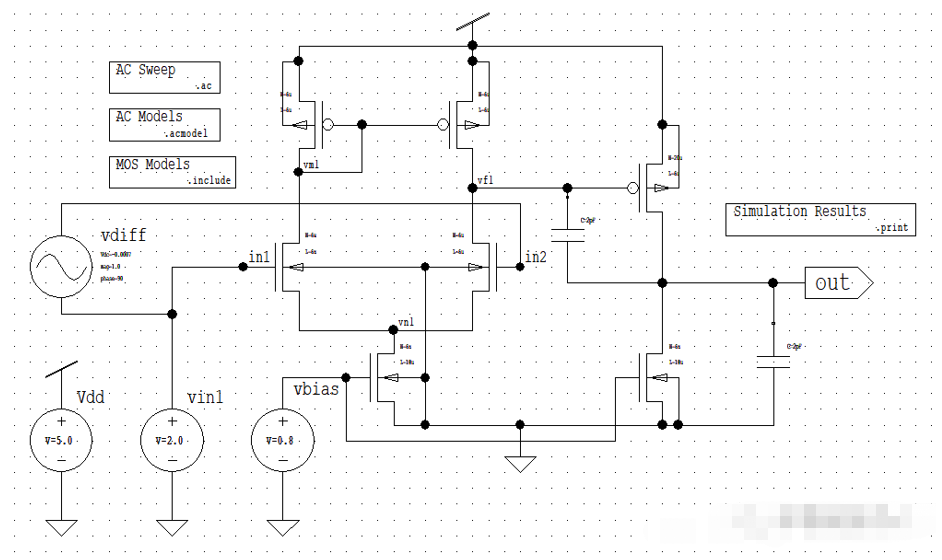

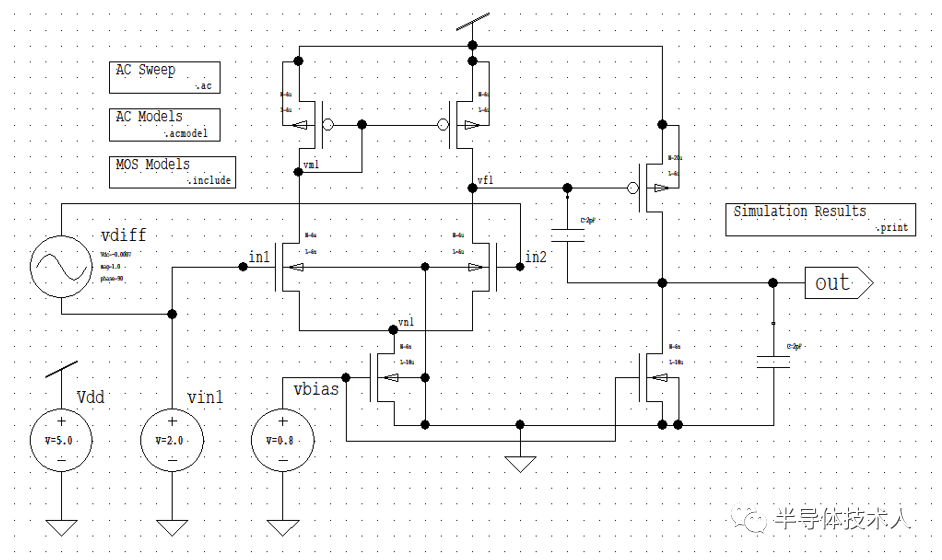

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2021-12-27 07:24:51

我在找信號放大器的時候,有的給出了增益,類似于功率可以增加多少倍,有的給出了共模抑制比,這兩個我怎么分別?我最后的結果是看我的信號功率能否從-15dBm增加到10dBm,共模抑制比我怎么換算?

2018-08-09 09:48:40

讀論文analysis of switched-capacitor commom-mode feedback circuit1.與單端輸出相比,全差分電路有更好的共模抑制比和電源抑制比。2.共模環路

2021-10-29 07:10:25

1、很多人用運放選共模抑制比越大越好,考慮到成本,我想計算一下理論值到底符不符合,比如我采分流器上的電流±74A,Gain=0.0335,共模輸入電壓有5V,電流精度要滿足0.05%,假如運放

2024-08-15 07:43:04

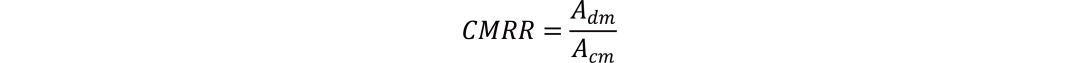

Rejection Ratio) 共模抑制比定義為當運放工作于線性區時,運放差模增益與共模增益的比值。 共模抑制比是一個極為重要的指標,它能夠抑制共模干擾信號。由于共模抑制比很大,大多數運放的共模抑制比一般在數

2018-09-29 15:26:19

對精度影響,判斷是否選用高阻運放或者是精密運放。3、環境條件看看運放溫度量程;注意溫漂參數影響;注意電源紋波抑制比PSRR參數4、其他要求1)通道數:如果是多級在確定其他指標前提下選用多通道運放;2

2022-10-18 09:35:27

AD-運算放大器共模抑制比CMRR

2012-04-01 10:47:33

。實測出來的這個值相比其他差分運放相差很大,在AD8260的手冊上并沒有找到CMRR值說明。High current driver的共模抑制比測量出來的結果對嗎??

2024-03-06 06:58:28

ads1291共模抑制比與頻率曲線中,為什么CMRR是負數,我們的理解CMRR應該是正數。

謝謝

2024-11-25 08:16:54

~120dB之間。實際運放的差模開環電壓增益是頻率的函數,為了便于比較,一般采用差模開環直流電壓增益(5)共模抑制比CMRR:共模抑制比定義為當運放工作于線性區時,運放差模增益與共模增益的比值

2014-05-26 13:30:40

的情況下,需要在電路設計中注意這個問題。

9、共模抑制比(Common Mode Rejection Ratio)

共模抑制比定義為當運放工作于線性區時,運放差模增益與共模增益的比值。

共模抑制比是一

2023-11-22 07:09:18

全工作頻率范圍內的運放共模抑制比如何測試?

2023-11-17 09:17:54

的CMRR參數決定。這個參數一般在實際工程上是很難達到的。在實際電路設計中,可以使用高精度萬用表測出低漂移的電阻,使得R1=R2, R3=R4,這樣,可以是運放的共模抑制比大幅度提升。轉自(嵌入式資訊精選)

2016-09-23 15:34:29

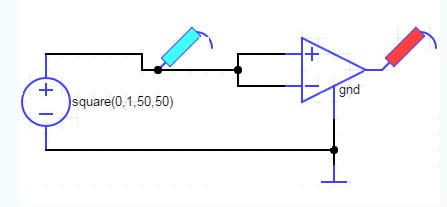

如圖所示,下面是一個交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(10V,10Hz),進行電路的共模抑制比(CMRR)測試,測試發現:

1、差分信號從INS+

2018-08-03 06:26:16

[td][/td] 如圖所示,如何設計AD8221交流耦合電路能:

1、降低噪聲,提高信噪比(SNR);

2、提高儀表運放輸入阻抗;

3、提高共模抑制比(CMRR)。

2023-11-17 09:47:43

提高差分放大器的共模抑制比,電阻的選擇很關鍵

2021-03-11 07:17:03

一個900KHZ的DC-DC經過一個LDO作為一個運放的供電電源 那我看這個運放CMRR的時候這個流入運放的電源的頻率是900khz嗎 我應該按照900KHZ去找他的cmrr對應嗎

2020-04-02 10:46:24

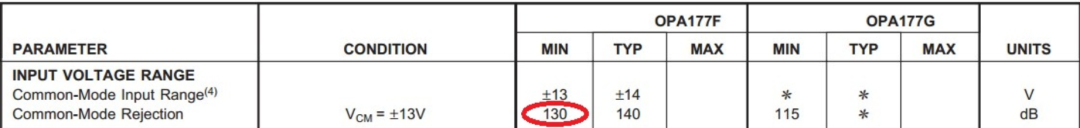

假設R1~R4都是理想5K的電阻,運放的CMRR為130dB,那么由此運放CMRR帶來的共模輸出電壓怎么算呢?原理圖如下:

2024-08-15 07:51:51

如何利用高增益運放,設計了一種具有高共模抑制比,高增益數控可顯的測量放大器。提高了測量放大器的性能指標,并實現放大器增益較大范圍的步進調節。

2021-04-22 06:59:18

下圖是電子學第二版的一個差分放大電路,書中說這電路共模抑制比是10萬,這能從圖中算出來嗎?

2020-04-08 23:09:06

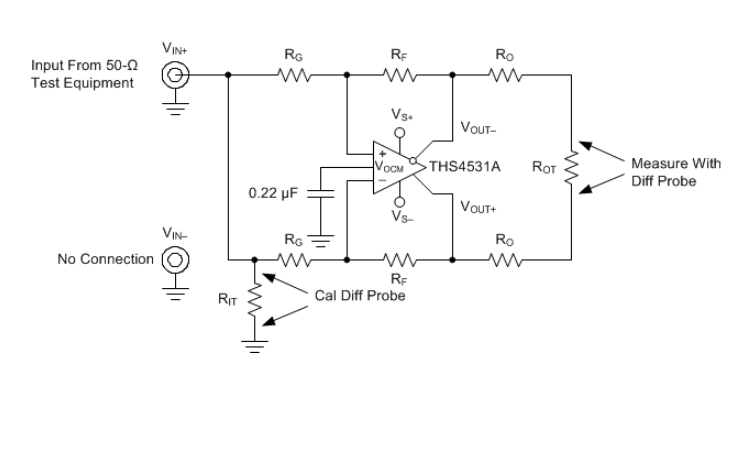

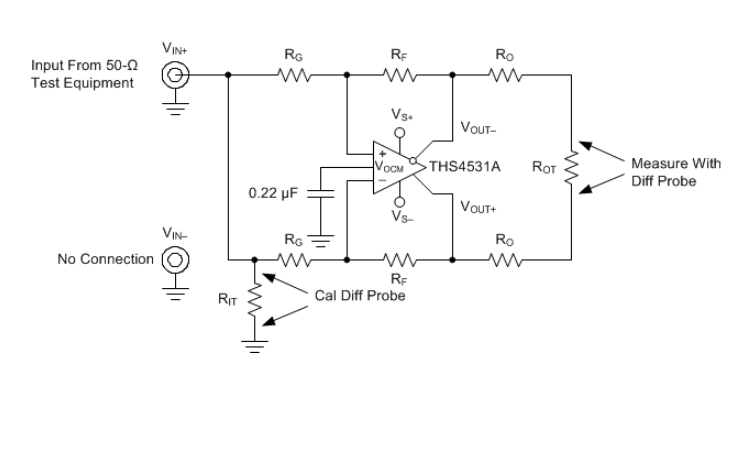

多個型號,THS4521是比較出色的一個型號,性能優異。但即使再好的差分驅動器,也必須配合合適的匹配電阻網絡才能發揮其優越性能。而實際上,電阻器的非理想性會對各種電路產生影響,例如:共模抑制比(CMRR

2019-05-22 08:53:17

影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

2024-09-09 07:32:22

此電路用來檢測腦電波的信號,性能要求此電路的共模抑制比要達到不低于80dB,而現在實測只能達到67dB,想知道,影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

2024-08-20 07:21:02

怎么根據共模抑制比Kcmr、最大共模輸入電壓Vic挑選運放

常見的集成運放推薦?

2024-08-19 06:22:13

怎么測ADS1299芯片的共模抑制比?將通道1的正負極輸入短接,接入一個0.5VP,共模電壓2.5V,F=50Hz,FFT圖像顯示輸出在50Hz時,為80dB。然而手冊是-110dB,應該怎么測出-110dB的共模抑制比呢?

2024-11-15 06:26:03

用到AD8227這款芯片,感覺共模抑制比有點低,請問怎么測定這個參數,我試過:將所有電極連在一起,相對于大地驅動這些電極。同樣,共模抑制的定義是20×log(VOUT/VIN),其中,VIN為共模

2023-11-21 06:24:20

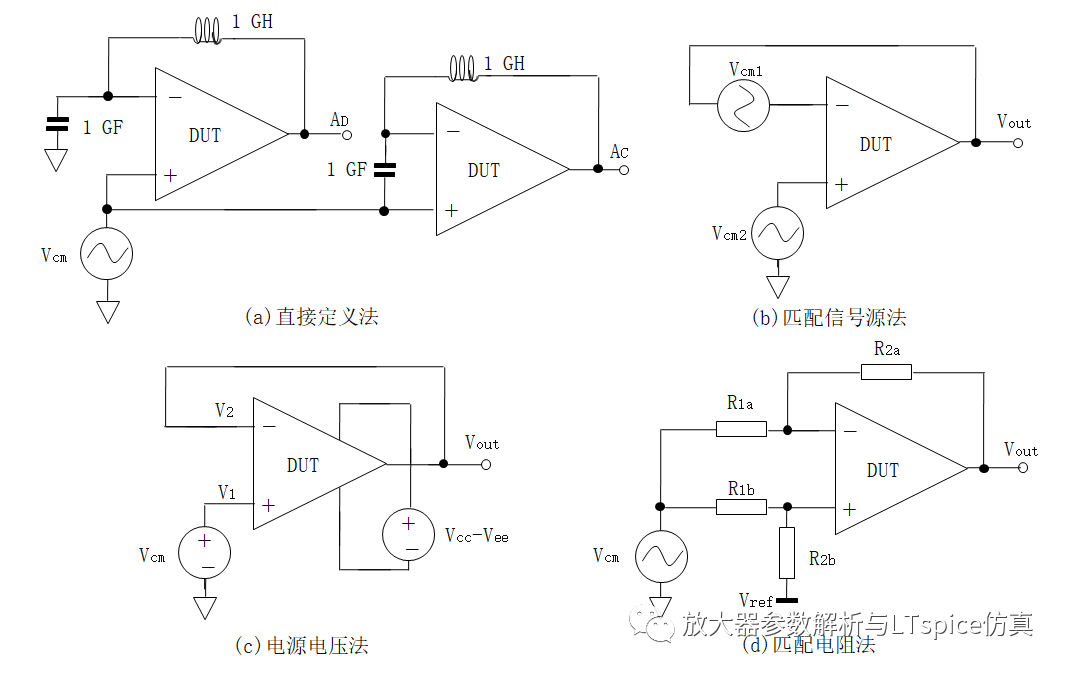

常被誤用的放大器共模抑制比測量方法會存在哪些不足?有沒有一種有效測量共模抑制比電路方案介紹?

2021-03-11 06:00:18

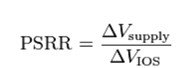

容易讓人想到,在高增益下產生任何輸出偏移,都需要電源的明顯變化!但一定要記住:共模抑制比 (CMRR) 和 PSRR 都是輸入參考參數:(1) PSRR 和 CMRR 定義為輸入失調電壓變化 ΔVOS

2018-09-19 11:00:26

、 共模抑制比CMRR

2013-11-18 22:44:46

50Hz的共模信號(相對REF),我該怎么判斷共模抑制比的大小才合理?

問題三:如果我對1.65V產生的共模信號進行軟件校準清零,再疊加1V 50Hz的共模信號(相對REF)上去,測得的值是否為真實的1V 50Hz 下的共模抑制比?

如果不正確,那怎樣才能測到正確的值?

2024-08-05 06:27:21

如圖所示,下面是一個交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(10V,10Hz),進行電路的共模抑制比(CMRR)測試,測試發現:

1、差分信號從INS+

2023-11-17 09:09:39

尋找一款超高共模抑制比的儀表運放,起碼高于120dB,越高越好

2018-08-03 07:12:09

如圖所示,如何設計AD8221交流耦合電路能:1、降低噪聲,提高信噪比(SNR);2、提高儀表運放輸入阻抗;3、提高共模抑制比(CMRR)。

2018-08-06 06:55:10

用到AD8227這款芯片,感覺共模抑制比有點低,請問怎么測定這個參數,我試過:將所有電極連在一起,相對于大地驅動這些電極。同樣,共模抑制的定義是20×log(VOUT/VIN),其中,VIN為共模

2018-09-13 11:52:30

(Common Mode Rejection Ratio) 共模抑制比定義為當運放工作于線性區時,運放差模增益與共模增益的比值。 共模抑制比是一個極為重要的指標,它能夠抑制共模干擾信號。由于

2019-12-26 14:44:23

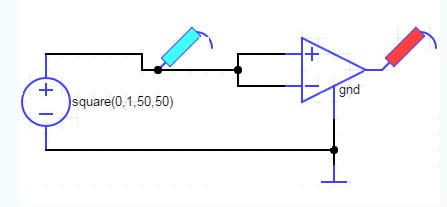

通過硬件和軟件的仿真實驗,總結出差分放大電路共模抑制比測定的正確方法關鍵詞:差分放大電路;共模抑制比;差模電壓放大倍數;共模電壓放大倍數;仿真

2010-04-13 11:07:33 91

91 共模抑制比(CMRR) 是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產生特定輸出所需輸入的共模電壓與產生同樣輸出所需輸入的差分電壓的比值。

2010-07-05 16:00:55 75

75 什么是共模抑制比

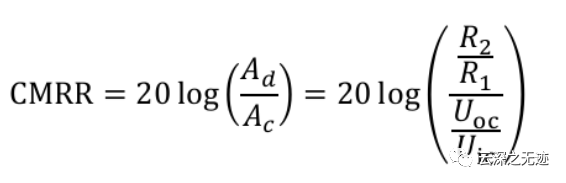

為了說明差動放大電路抑制共模信號的能力,常用共模抑制比作為一項技術指標來衡量,其定義為放大器對差模信號的電壓放大倍數Aud 與對共模信號的電

2007-10-15 17:37:51 9087

9087 放大器的共模抑制比的定義

共模抑制比(CMRR)是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產生特

2009-04-22 20:40:37 2542

2542 共模抑制比,共模抑制比是什么意思

共模抑制比的定義

為了綜合評價差動放大電路對共模信號的抑制能力和對差模信號的放大能力,特

2010-03-09 16:36:11 14810

14810 你或許知道“共模抑制比是差模增益與共模增益之比”,但你知道共模抑制比120dB與60dB區別多大嗎?你知道為什么要抑制共模信號嗎?

2015-10-01 15:00:00 23339

23339 華強盛電子導讀:網絡變壓器共模抑制比CMRR概念及原理 網絡變壓器共模抑制比CMRR? 在網絡變壓器工程圖紙中我們會看到一個參數 CMRR,它中文翻譯為共模抑制比,那么它是個什么概念呢

2019-02-25 17:55:54 2464

2464 在電子學中,差分放大器(或其他裝置)的共模抑制比(CMRR)是一個度量,用于量化裝置抑制共模信號的能力,即那些同時出現在兩個輸入端且同相出現的信號。一個理想的差分放大器將有無限的共模抑制比,但這在

2019-09-14 10:57:00 65839

65839

來源:羅姆半導體社區 共模抑制比(CMRR) 是指差分放大器對同時加到兩個輸入端上的共模信號的抑制能力。更確切地說,CMRR是產生特定輸出所需輸入的共模電壓與產生同樣輸出所需輸入的差分電壓的比值

2023-02-01 13:42:32 5689

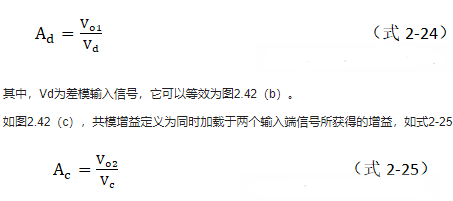

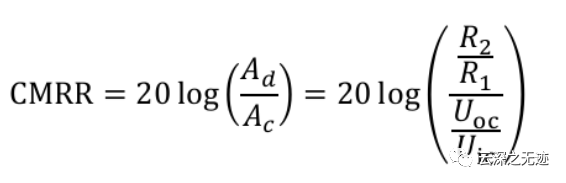

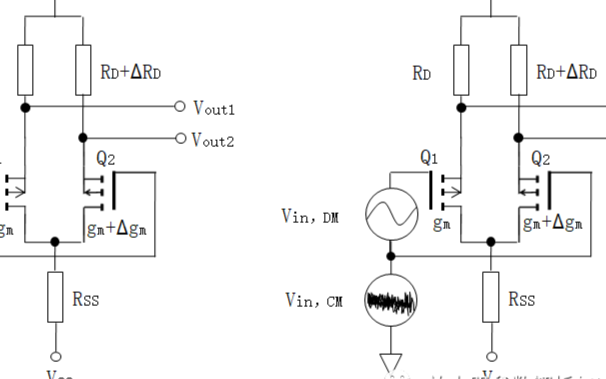

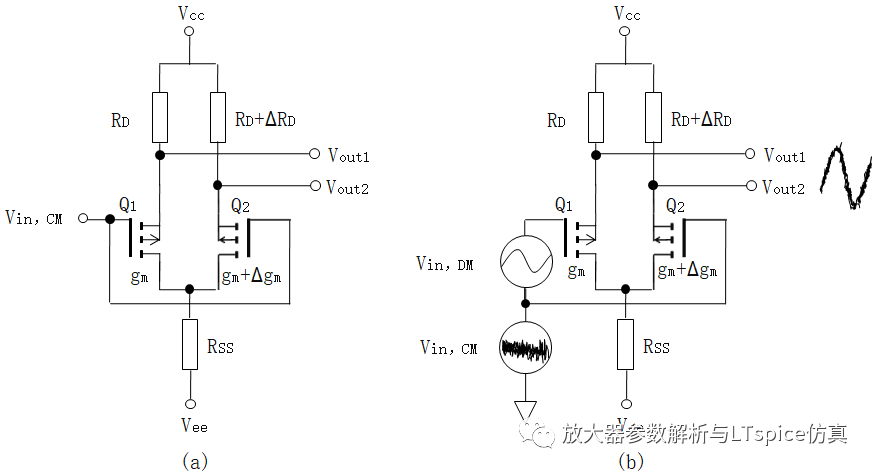

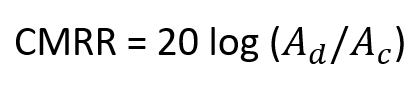

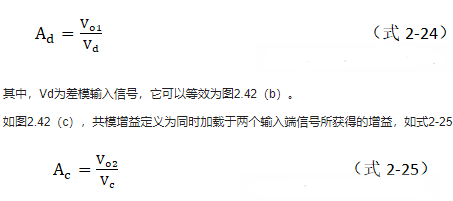

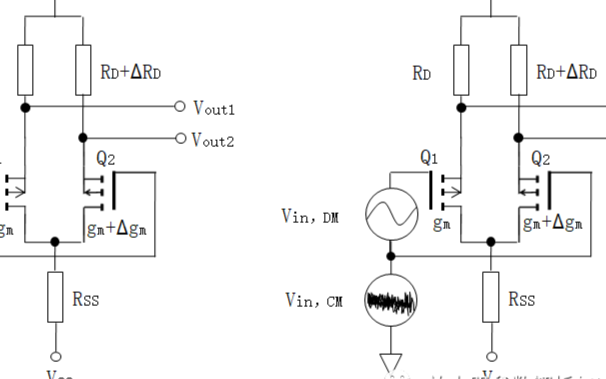

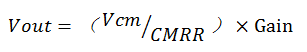

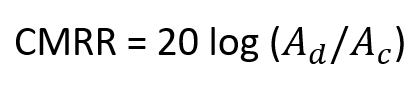

5689 放大器的差模增益是電路所需要的增益,而共模增益將放大直流噪聲。共模抑制比(Common Mode Rejection Ratio,CMRR),定義為差模增益與共模增益的比值,如式2-26。

2020-10-22 17:51:53 5298

5298

如《放大器共模抑制比(CMRR)參數評估與電路共模抑制能力實例分析》中案例,由于電阻誤差導致電路共模抑制能力下降,是使用通用放大器組建差動放大電路的常見問題之一。工程師常常疑惑1%誤差的電阻

2020-10-31 09:42:35 4820

4820

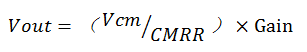

在《放大器共模抑制比(CMRR)參數評估與電路共模抑制能力實例分析》文中,介紹使用共模抑制比的倒數,將共模信號折算到輸入端評估所引起的誤差,有工程師認為這種方式在輸入共模信號為交流信號時的結果不準

2020-11-14 11:09:05 5371

5371

MT-042:運算放大器共模抑制比(CMRR)

2021-03-21 08:57:14 13

13 電子發燒友網為你提供共模抑制比(CMRR)取決于幾個放大器設計因素資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-05 08:48:01 16

16 通常直流精度要求較高,失調電壓,失調電流通常是我們關注的參數,然而還有一個非常重要的參數,CMRR,共模抑制比也會對儀表放大器的精度造成重要的影響。

共模抑制比,描述的是放大器共模電壓的變化導致

2021-11-10 09:37:56 2487

2487

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2022-01-05 14:22:58 6

6 理想情況下,差分放大器電路中的電阻應仔細選擇,其比值應相同 (R2/R1 = R4/R3)。這些比值有任何偏差都將導致不良的共模誤差。差分放大器抑制這種共模誤差的能力以共模抑制比(CMRR) 來表示。

2022-06-01 09:41:09 4460

4460 其實在共模信號為交流信號時,這種評估方法仍然實用,問題在于放大器的共模抑制比參數并非恒定不變,它隨共模信號頻率變化變化。本篇介紹共模抑制比隨共模交流信號變化的原因,評估示例,并通過仿真增強理解。

2023-02-22 14:30:55 2374

2374

測量放大器的失調電壓、偏置電流參數,可根據所設計的電路簡易調整就能完成測試。而共模抑制比參數的測試方法卻相對復雜,本篇分析幾種常被誤用的放大器共模抑制比測量方法的不足之處,以及提供一種有效測量共模抑制比電路以及提供仿真。

2023-02-22 14:33:45 4622

4622

電源抑制比的概念,接觸過運放的讀者應該知道,指的是運放對電源噪聲或者紋波的抑制能力,噪聲和紋波是交流的,所以運放的電源抑制比一般指的是AC PSRR。但是什么又是運放的直流電源抑制比(DC_PSRR)呢?是指運放供電電壓的變化,引起運放輸入失調電壓的變化,這兩個變化之比就是運放的直流電源抑制比。

2023-03-17 15:52:46 3346

3346

號,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調電壓,失調電流通常是我們關注的參數,然而還有一個非常重要的參數,CMRR,共模抑制比也會對儀表放大器的精度造成重要的影響。

2023-04-06 10:22:43 2483

2483

共模抑制比(CMRR):運放的共模抑制比等于其差模電壓增益減去共模電壓增益。

2023-04-17 17:28:26 4297

4297

關于運放的參數很多,常用的卻沒幾個。 本文講一下個人對輸入失調電壓、共模抑制比、軌至軌的理解。

2023-04-24 14:35:53 2743

2743

運放的共模擬制比,是常被大家關注的一個運放參數,尤其是在差分放大器和儀表放大器中。但這一小節只討論運放的共模抑制比,以及CMRR帶來給運放的誤差。關于差分放大器和儀表放大器,以后另文討論。在開始討論

2023-04-27 14:56:54 4

4 CMRR(Common Mode Rejection Ratio)的絕對值越大對共模電壓的抑制能力越強,本文主要討論在實際應用中OPA關于CMRR的計算具體案例。

2023-05-12 11:41:04 5559

5559

共模抑制比(CMRR):運放的共模抑制比等于其差模電壓增益減去共模電壓增益。

2023-07-12 11:27:57 3103

3103

什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和電源抑制比(power supply rejection

2023-10-29 11:45:48 10804

10804 通常運放datesheet手冊中所給出的CMRR值,是一個直流參數。它的好壞,會影響運放輸出誤差的大小。即CMRR越小,則運放對輸入端共模電壓所引起的輸出誤差抑制能力越差。

2023-11-02 10:23:13 2122

2122

等。在這些因素中,共模抑制比率(CMRR)是我們需要關注和了解的一個重要指標。 CMRR是運放的一個重要參數,它是指在輸入信號一致時,輸出信號與兩個輸入信號之間的差異,也就是共模電壓,之間的比率。這個比率越大,說明運放的共

2023-11-06 10:20:00 1113

1113 影響共模抑制比的主要因素 如何提高共模抑制比? 共模抑制比是一種衡量信號處理系統抑制共模干擾的能力的指標。它表示當輸入信號被共模干擾所擾動時,系統輸出信號中共模干擾的減弱程度。共模抑制比較大的系統

2023-11-08 17:46:26 3551

3551 運放的共模抑制比高有什么作用?共模抑制比比較高的運放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一個衡量運放的性能的重要指標,表示運放在輸入信號的共模

2023-11-20 16:35:53 3089

3089 電子發燒友網站提供《適合過程控制應用的完整高速、高共模抑制比(CMRR)精密模擬前端.pdf》資料免費下載

2023-11-24 15:33:30 0

0 同相比例放大器為什么對共模抑制比要求高?運放的共模抑制比如何仿真? 同相比例放大器是一種常見的放大電路,用于放大微弱信號。在應用中,通常需要對放大的信號進行差分測量,即對信號的差值進行放大,而抑制

2024-01-26 14:42:55 3544

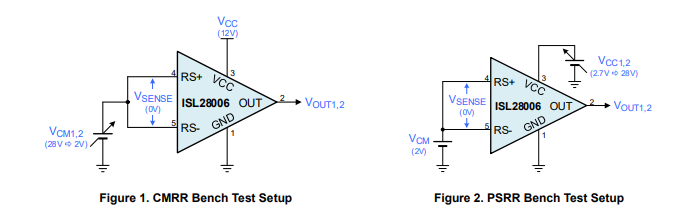

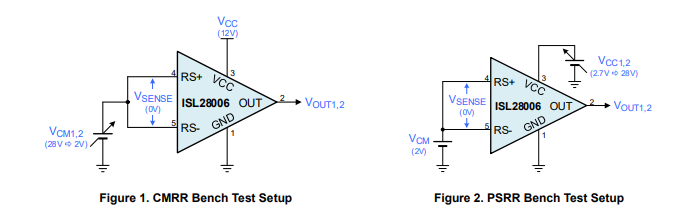

3544 雖然電流檢測放大器(如ISL28006)的數據手冊以電氣規格的形式展示了器件性能,但有時客戶需要通過基準測試來確認電氣參數。尤其重要的是共模抑制比(CMRR)和電源抑制比(PSRR),這些參數

2025-02-21 09:49:22 1055

1055

共模抑制比詳解在探頭的數據手冊上,共模抑制比性能參數是核心指標之一。共模抑制比又名CMRR,通常用分貝(dB)來表示,其計算公式為:其中其中本司光隔離產品CMRR在直流或低頻下能達到120dB以上

2025-06-23 09:45:17 1138

1138

儀表放大器最顯著的優勢之一在于其極高的共模抑制比(Common-Mode Rejection Ratio,CMRR),這一指標直接決定了系統在強共模干擾環境下對微弱差模信號的提取能力。因此,在儀表

2025-12-25 07:41:04 121

121

電子發燒友App

電子發燒友App

評論