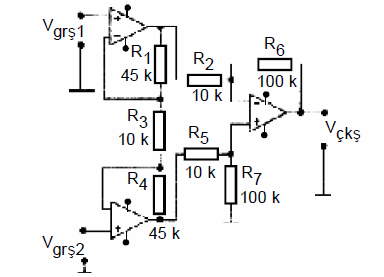

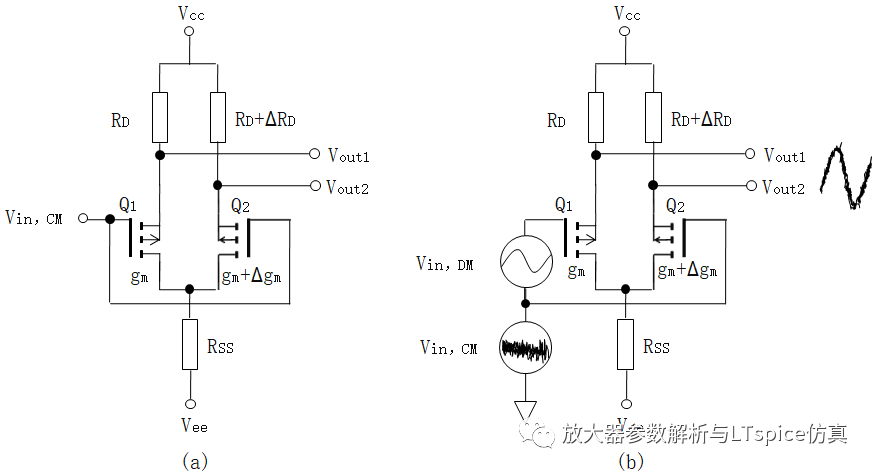

儀表放大器最顯著的優勢之一在于其極高的共模抑制比(Common-Mode Rejection Ratio,CMRR),這一指標直接決定了系統在強共模干擾環境下對微弱差模信號的提取能力。因此,在儀表放大器選型與電路設計階段,有必要通過仿真手段對其 CMRR 特性進行定量分析與驗證。下面以 AD8422 儀表放大器為例,介紹其共模抑制比的仿真分析方法。

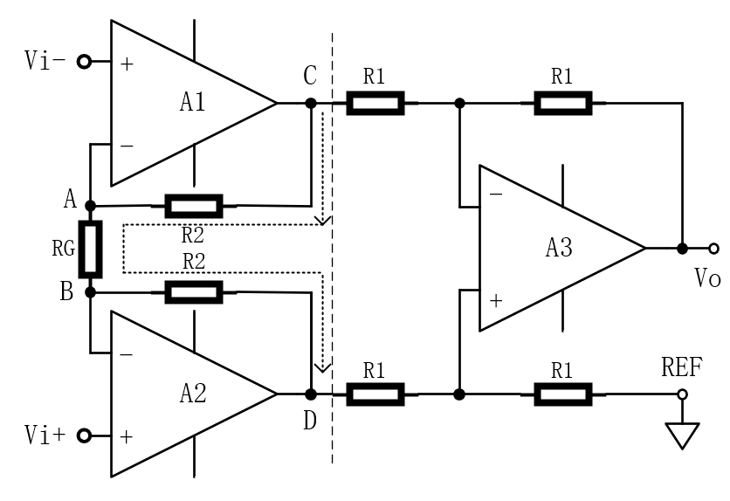

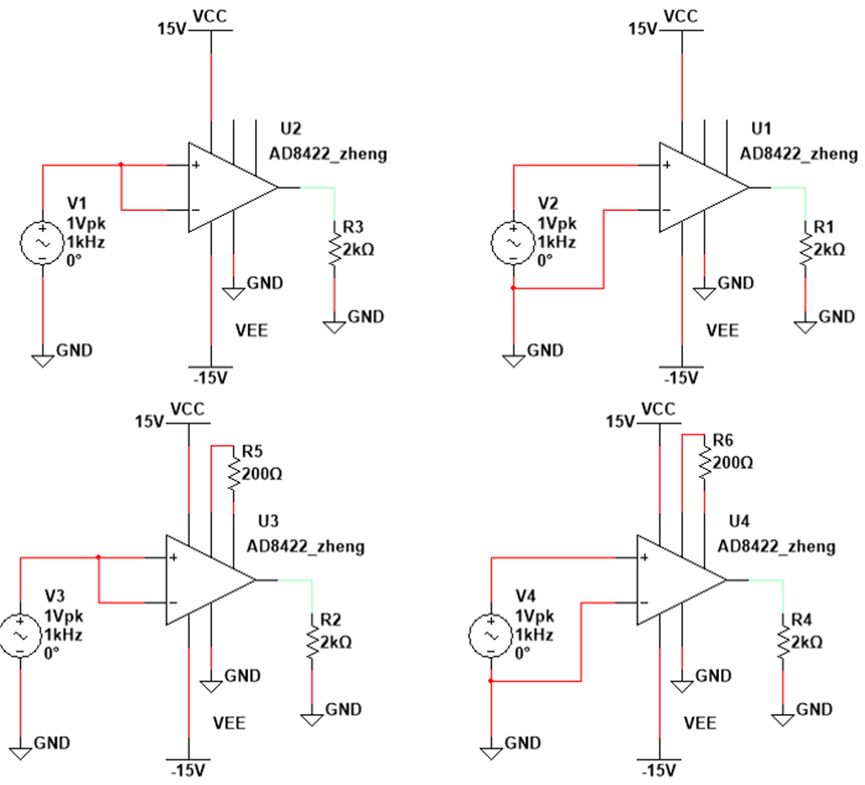

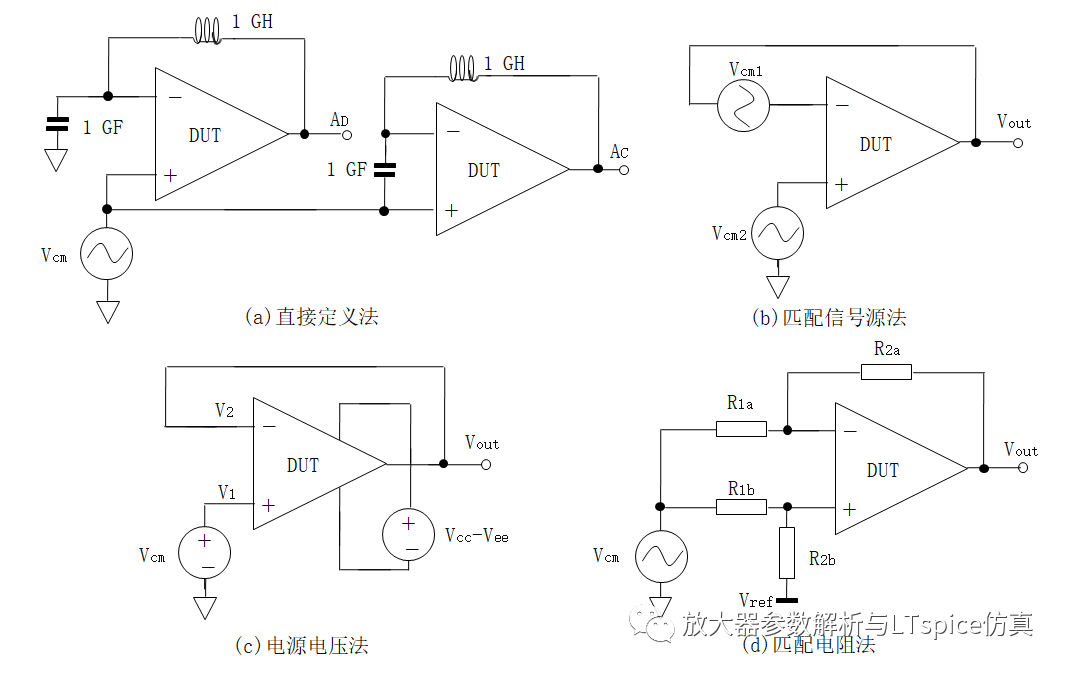

圖 2-29 所示為 AD8422 的 CMRR 仿真原理圖。左上角電路用于仿真在放大倍數為 1 條件下的共模放大倍數,即對兩個輸入端同時施加幅值與相位相同的共模信號,測量輸出端的響應;右上角電路用于仿真同樣放大倍數為 1 時的差模放大倍數,即對兩個輸入端施加等幅反相的差模信號。通過上述兩組仿真結果,并結合《運放密集》視頻課程中對共模抑制比定義及計算公式的介紹,即可得到 AD8422 在放大倍數為 1 時的 CMRR 隨頻率變化曲線。

采用相同的仿真思路,圖 2-29 左下角與右下角分別給出了放大倍數為 100 時的共模放大倍數與差模放大倍數仿真電路。通過對這兩種工況下輸出幅值的頻域分析,可進一步計算并得到 AD8422 在高增益條件下的 CMRR 與頻率關系曲線,從而評估其在不同增益設置下的共模抑制能力。

圖2-29 AD8422的CMRR仿真原理圖

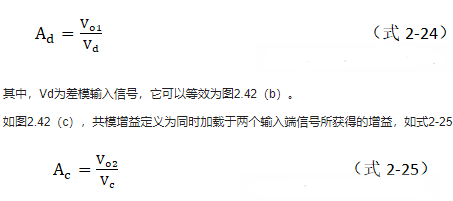

圖 2-30 給出了對應的仿真結果。可以看到,右圖仿真所得的 CMRR 曲線與 左圖AD8422 數據手冊中給出的典型特性曲線高度一致,驗證了仿真模型與分析方法的正確性。例如,在 10 kHz 頻率處,當放大倍數為 1 時,CMRR 約為 81 dB;當放大倍數提高至 100 時,CMRR 提升至約 100 dB,該結果與手冊參數基本一致。

圖2-30 AD8422的CMRR仿真結果

需要特別指出的是,儀表放大器的共模抑制比通常隨放大倍數的增加而提高,這一特性為高抗干擾模擬前端的設計提供了重要參考方向。在實際電路設計與系統優化過程中,應充分結合器件手冊中的性能曲線與應用建議,通過合理選擇放大倍數及外圍參數配置,最大限度地發揮儀表放大器的共模抑制性能,從而提升整體系統的信號質量與穩定性。

-

共模抑制比

+關注

關注

3文章

87瀏覽量

16402 -

儀表放大器

+關注

關注

18文章

515瀏覽量

73631 -

仿真分析

+關注

關注

3文章

115瀏覽量

34212

發布評論請先 登錄

放大器共模抑制比參數定義及影響電路共模抑制的因素分析

高共模抑制比(CMRR)儀表放大器電路原理圖講解

如何測定儀表放大器的共模抑制比?

放大器的電源抑制比和共模抑制比

儀表放大器AD620的共模輸入范圍超過電源電壓會影響共模抑制比嗎?

放大器的共模抑制比的定義

放大器共模抑制比參數與頻率的關系是什么

盤點放大器共模抑制比參數測量方法有哪些

仿真分析儀表放大器共模抑制比

仿真分析儀表放大器共模抑制比

評論