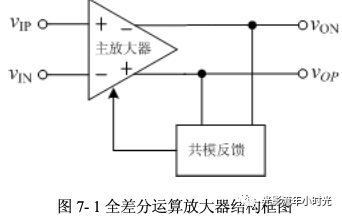

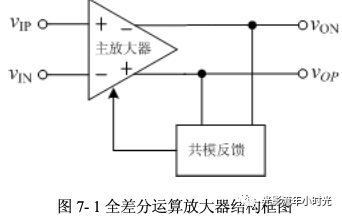

全差分運算放大器就是一種具有差分輸入,差分輸出結構的運算放大器。

2023-09-25 17:34:56 16365

16365

差分輸出是一種電路設計技術,主要用于提取信號的變化情況,以及對信號進行放大和處理。差分輸出將輸入信號通過差動放大器進行放大,然后輸出兩個相位相反的信號。

2024-01-31 18:17:12 6769

6769

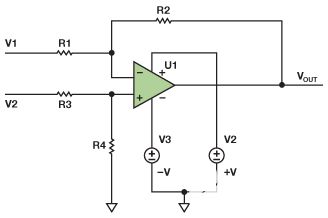

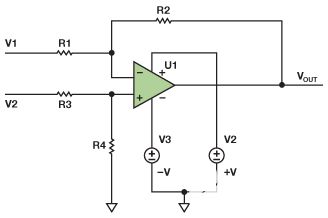

在一種相對常見的情況下,1%電阻器和一個較好的運算放大器便可以構建一個完全合格的差動放大器

2021-04-06 07:36:10

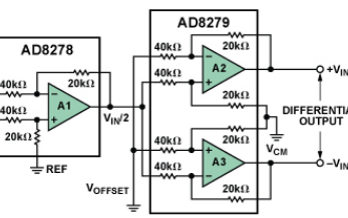

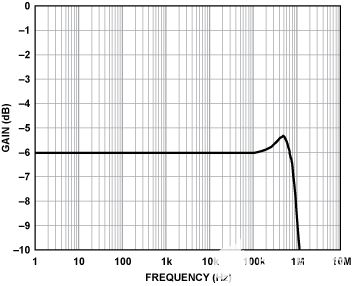

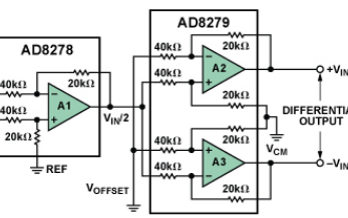

更有利。圖1顯示一個增益為1/2的差分輸出放大器系統。圖1. G = 1/2的差分輸出差動放大器功能框圖差分放大器A1的增益配置為1/2。 此放大器的輸出送到放大器A2的同相輸入端和放大器A3的反相輸入

2018-10-26 11:08:13

如何實現低功耗、低成本的差分輸入轉單端輸出放大器電路?

2019-07-22 07:49:38

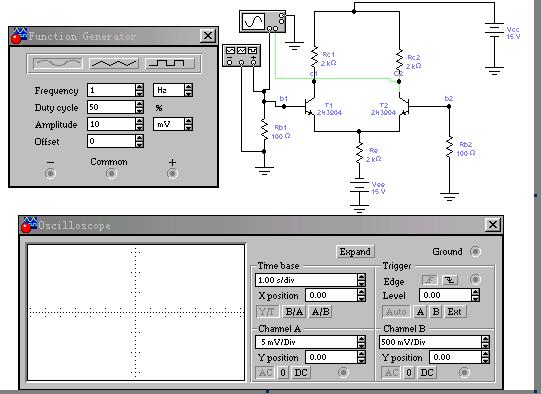

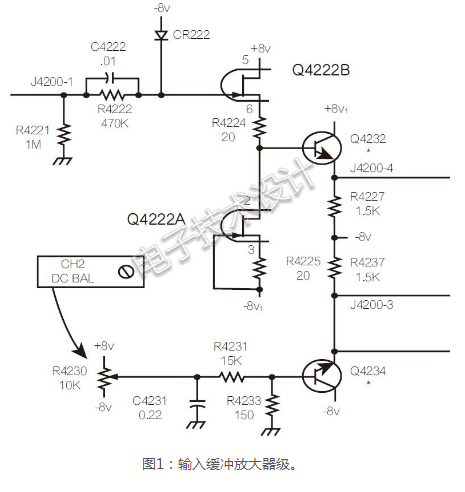

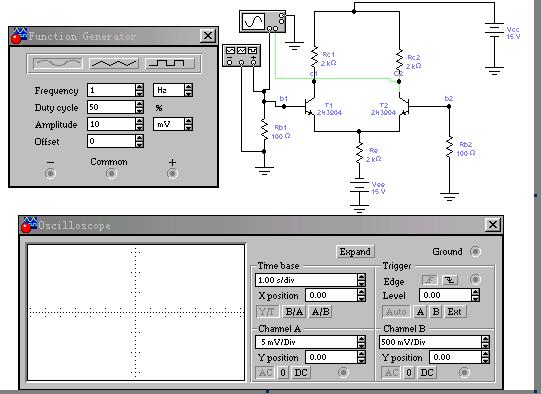

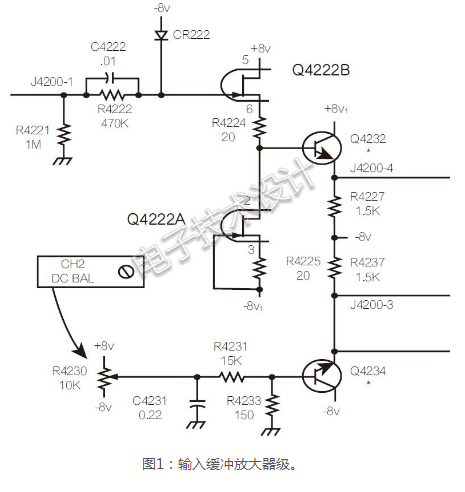

差動放大電路加深理解差動放大器的工作原理;學習差動放大器共模抑制比的測量方法;掌握提高差動放大器共模抑制比的方法;差動放大器是一種零點漂移非常小的直接耦合放大器。由于電路結構的盡可能對稱性,使其具有

2009-09-08 08:52:26

是否有差分輸入、單端輸出,300M帶寬的差動放大器

2012-06-10 21:00:29

轉換增益之比。 在理想的單端和全差分放大器中,只有輸入差分電平會影響輸出電壓。然而實際電路中,電阻器失配對可用CMRR造成了限制。對于上圖,當采用平匹配準確度為2%(1%容差)的表面貼裝電阻器

2019-05-22 08:53:17

差動放大器為什么能成精密電流源的核心?外圍器件有哪些?怎么去選擇晶體管?

2021-04-07 06:36:34

差動放大器和電流檢測放大器附件差動放大器和電流檢測放大器.pdf329.1 KB

2018-11-05 09:10:37

我想設計采集200~300MHz的信號的系統,首先2路反相的信號輸入差動放大器,然后差動放大器輸出接1G采樣率的高速采集卡,接著當采集到信號高于某一閾值時將其輸出到電腦里,其他時間采集的的信號不輸出。我想請問這樣設計是否合理,差動放大器應該怎么選擇,高速采集卡只輸出大于某一閾值的信號能否實現

2012-06-09 22:18:09

電流范圍。圖1. 差動放大器和運算放大器構成精密電流源輸出電流可以通過下式計算:如果 Rg1 = Rg2 = Rf1 = Rf2, 上式可簡化為:最大輸出電流受以下因素限制:運算放大器輸入范圍、差動

2018-10-24 09:55:44

是零.前置放大器是差動輸入, 單輸出. 后面接的 NI 9239 是差動輸入, 而且輸入端對地是懸浮的. 我的前置放大器是用3伏電池供電, 所以也是懸浮的.我考慮可能是: 1.我連接錯誤或者 NI

2013-10-23 01:18:36

的使用。下面就來分享構建差動放大器及其性能優化方法!儀表放大器可能不具備用戶要求的帶寬、直流精度或功耗。因而,在這種情況下,用戶可通過一個單放大器和外部電阻自行構建差分放大器,以替代儀表放大器。不過,除非

2019-07-24 06:36:28

基本非反相放大器配置結構(包括一種簡單的 G=1 緩沖器放大器)中,可以看到運算放大器電路的影響。下面來看一下一個正向輸入步進。輸出無法立即跟隨浪涌輸入電壓變化。如果輸入步進大于 0.7V,則 D1 導電

2018-09-26 11:47:31

ADC驅動器配置為差動放大器幾點需要注意

2021-03-17 06:16:32

ST25RU3993-eval PCB 內部放大器輸出差分走線看起來不適合首選阻抗。查看紅色圈出的痕跡。這些不應該是 100 歐姆差分與紫色混頻器反饋跡線相同嗎?布局中的跡線寬度顯然與紫色標記的 100 歐姆差異跡線不同。

2023-01-16 08:35:17

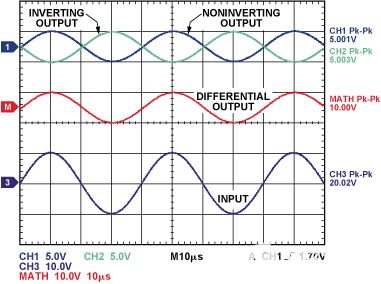

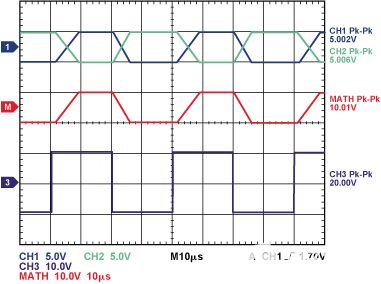

R2移至R3,電路的新增益為-1。現在Out_A與輸入反相,輸出之間的差值在幅度上等于輸入信號。 圖7.使用交叉連接技術生成差分儀表放大器輸出信號,在增益=-1的條件下測得的結果。 如前所述,其他技術

2019-08-05 04:00:00

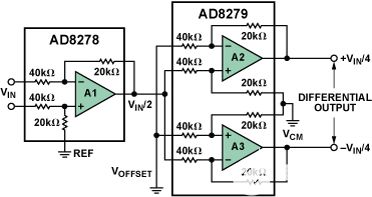

通常具有單端輸出,但為了獲得差分輸入ADC的全部優勢,包括更高動態范圍、更佳共模抑制性能和更低的噪聲敏感度,具有差分輸出會更有利。圖1顯示一個增益為1/2的差分輸出放大器系統。圖1. G = 1/2的差

2019-09-28 08:30:00

/R1的"理想"增益施加于 2 V。如果電阻非理想,則共模電壓的一部分將被差動放大器放大,并作為V1 和V2 之間的有效電壓差出現在VOUT,無法與真實信號相區別。差動放大器抑制這一部分

2018-06-07 15:52:08

為什么使用全差動放大器可以減少偶次諧波干擾相比單端輸出放大器?

2023-11-21 07:38:09

為什么使用全差動放大器可以減少偶次諧波干擾相比單端輸出放大器?

2018-08-24 11:12:15

達1G的,而差分放大器卻有很多,但是沒有找到有+-5V供電的,并且以3.3V/5.0V單電源供電為主,我想問一下之所以形成這樣的產品線是由集成電路的制造工藝決定的,還是由市場的應用決定的?為什么差分放大器的帶寬可以達到10G而非差分的放大器就達不到?

2019-03-07 09:01:45

VOUT_A,CH3為VOUT_B。輸出A和B匹配且反相,差值在幅度上等于輸入信號。圖6. 使用交叉連接技術生成差分儀表放大器輸出信號,在增益 = 1的條件下測得的結果接下來,將49.4kΩ增益電阻從R2

2021-10-15 06:30:00

請問什么是精密差分輸出儀表放大器?

2021-04-14 06:11:06

初學者向各位請教一些問題!

1.儀表放大器和普通運算放大器有什么不同呢?二者在組建電路上有什么區別呢?

2.使用儀表放大器對差分輸入信號自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是

2023-11-20 07:56:29

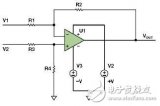

問題:如何實現低功耗、低成本的差分輸入轉單端輸出放大器電路?

2017-10-23 14:05:00

精密放大器,如圖1所示。此電路顯示了一種將差分輸入轉換為帶可調增益的單端輸出的簡單方式。系統增益可通過公式1確定:其中,增益= RF/1 kΩ,且 (VIN1 – VIN2) 是差分輸入電壓。圖1. 差

2018-10-11 10:44:09

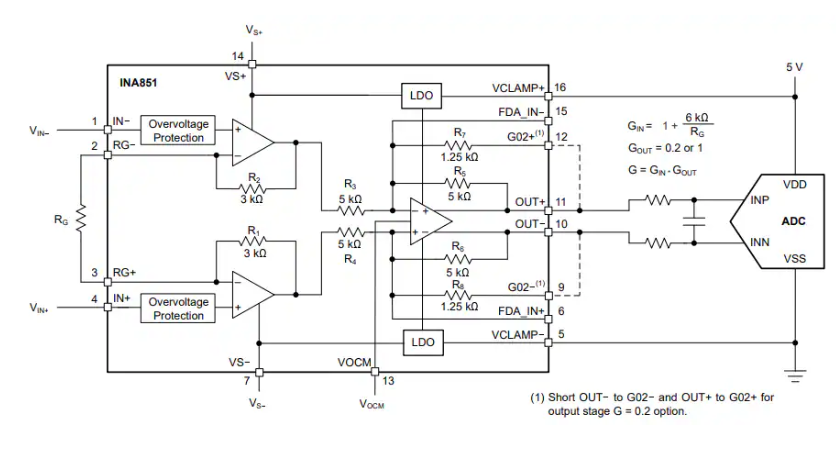

全差分儀表放大器具有其他單端輸出放大器所沒有的優勢,它具有很強的共模噪聲源抗干擾性,可減少二次諧波失真并提高信噪比,還可提供一種與現代差分輸入ADC連接的簡單方式。低功耗全差分儀表放大器電路怎么設計?

2021-04-06 08:11:07

為什么使用全差動放大器相比使用單端輸出放大器可以減少偶次諧波的干擾?

2024-08-30 07:50:31

全差分儀表放大器與其他單端輸出放大器相比有什么優勢?雙線遠程傳感器前置放大器有什么最佳實例?基于555定時器的D類耳機驅動器是理想的實用放大器嗎?八進制CMOS緩沖器的二象限乘法DAC是怎樣工作的?電阻器的非理想性會對精準放大器有什么影響嗎?

2021-04-06 09:01:33

基準電壓用作差分輸出的共模電壓,從而無需使用基準電壓源。因此,其輸出與ADC成比例,這 意味著ADC的VREF任何變化都不會影響系統的性能。此差動放大器抑制共模電壓的能力取決于AD629差動放大器內部

2018-10-19 10:30:35

分立差動放大器與集成解決方案

2021-01-08 06:21:56

用單端儀表放大器實現全差分輸出

2020-11-30 06:33:09

1,就是單端信號輸入差分放大器時,差分放大器的負輸入-IN該怎么接??

2,差分輸出接示波器該怎么阻抗匹配呢?看我原理圖畫的這樣正確嗎?

2024-08-26 06:18:21

比如一個傳感器的輸出是2個信號電壓,一正一負。其電壓差值與傳感器數值成一 一對應關系。所以要做一個雙端輸入單端輸出差分放大電路或是減法運算電路。應該怎么考慮?普通的運算放大器大多都是雙端差分輸入,那么在這個應用場景下,雙端輸入單端輸出差分放大電路和減法運算電路相同。

2019-08-13 12:40:28

交叉連接技術保持儀表放大器的所需特性,同時提供附加功能。盡管本文討論的所有示例都實現了差分輸出,但在交叉連接電路中,輸出的共模不會受電阻對失配的影響,與其他架構不同。因此,始終都能實現真正的差分輸出

2021-01-19 07:04:11

經典的分立差動放大器設計非常簡單,一個運算放大器和四電阻網絡有何復雜之處?經典的四電阻差動放大器性能可能不像設計人員想要的那么好。從實際生產設計出發,分立電阻有什么缺點?

2019-07-30 07:28:28

如何實現低功耗、低成本的差分輸入轉單端輸出放大器電路?

2021-03-18 06:48:59

(可調)增益;但是,在需要全差分輸出信號時,它就無能為力了。人們已經使用一些方法,用標準組件實現全差分儀表放大器。但是,它們有著各自的缺點。圖1.經典儀表放大器。

2019-09-11 11:51:20

問題:我們可以使用儀表放大器生成差分輸出信號嗎?

2019-02-28 14:52:09

,使用R2 = 98.8kΩ,電路會使輸入信號衰減兩倍。圖8. 使用交叉連接技術生成差分儀表放大器輸出信號,在增益 = 1/2的條件下測得的結果最后,為了證明高增益,選擇R2 = 494Ω以實現G = 100

2022-05-18 16:20:15

實現真正的零伏。特性 單電源 +3V 至 +5V將差動放大器輸出擴展至包含 0V低噪聲(約 100dB SNR)低功耗(5V 時為 2mW)36MHz 的帶寬該參考設計已經過實驗室測試,并具有設計文件和應用報告支持

2022-09-14 09:39:34

,圖 2 描述了一個低側測量案例。在這種情況下,您可能還會需要高精確電阻器匹配。此時,輸出電壓為偏移電壓,并且基準電壓應用于差動放大器的“參考”端。這樣做的目的一般是為了把輸出電壓升高至零以上,從而

2018-09-26 11:25:50

有一個放大器芯片有兩個輸出端口,說是叫差分輸出,我只接其中一個腳連單片機的adc相應的輸入引腳能采集到準確的信號嗎

2016-06-13 12:50:00

是In_A的輸入信號,CH2為VOUT_A,CH3為VOUT_B。輸出A和B匹配且反相,差值在幅度上等于輸入信號。 圖6.使用交叉連接技術生成差分儀表放大器輸出信號,在增益=1的條件下測得的結果。 接下來,將

2019-10-08 13:52:27

專家們好,因為PCB布線關系,能否將DAC5670的差分輸出P端和N端分別接到差分放大器LMH6554的N端和P端,也就是把DAC5670輸出差分對反向接到LMH6554的輸入,然后將LMH6554的輸出接到差分調制芯片?

2024-09-14 07:05:53

。如果電阻不理想,那么部分共模電壓將被差動放大器放大,并作為 V1 和 V2 之間的有效差壓出現在 VOUT 處,其無法與實際信號相區分。差動放大器抑制這一部分電壓的能力稱為共模抑制。該參數可以表示為

2020-03-30 10:59:53

AD的技術專家們,貴公司有沒有性能和AD8221差不多,差分輸入差分輸出的精密儀表放大器,求指教~

2018-10-26 09:31:10

初學者向各位請教一些問題!1.儀表放大器和普通運算放大器有什么不同呢?二者在組建電路上有什么區別呢?2.使用儀表放大器對差分輸入信號自身的性能有什么要求嗎?(比如共模電壓要到一定值,這是為什么呢

2018-08-19 07:02:41

將差分輸入轉換為帶可調增益的單端輸出的簡單方式。系統增益可通過公式1確定:其中,增益= RF/1 kΩ,且(VIN1 – VIN2)是差分輸入電壓圖1. 差分輸入單端輸出放大器通常,這種方法可以在出

2018-10-31 10:52:01

問:我們可以使用儀表放大器生成差分輸出信號嗎?

2019-07-30 07:31:54

供電軌、具有共模范圍的單電源器件。然而,單電源器件往往無法提供圖形數據(例如圖2所示的共模限值)但是會通過表格形式的額定電壓范圍來說明性能。運算放大器差分輸入電壓范圍在正常工作模式下,運算放大器連接至

2014-08-13 15:34:22

較為基礎的問題。 任何實際運算放大器輸入和輸出端的工作電壓范圍都是有限的。現代系統設計中,電源電壓在不斷下降,對運算放大器之類的模擬電路而言,3 V至5 V的總電源電壓現在已十分常見。這一數值和過去

2018-09-21 14:50:51

差動放大器實驗

2008-09-27 17:11:24 11648

11648

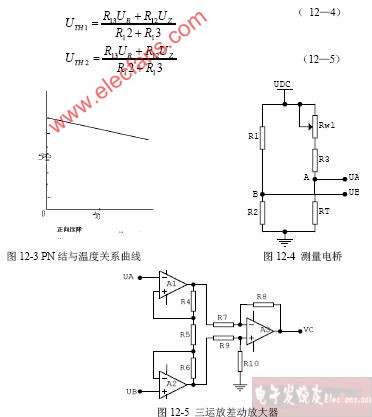

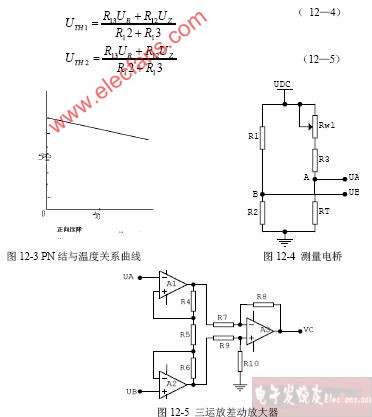

三運放差動放大器電路圖

差動放大器的作用是把橋路的差模小信號放大并轉換為單端輸出信號。為了提高運算放大器的

2009-03-09 11:41:20 9349

9349

差動放大器的主要性能指標都有那些?差動放大器都有那些優點?差動放大器為什么能較好的抑制零點漂移?

(1)差動放大器的主要性能指

2009-04-22 20:29:29 10859

10859 共基差分低噪聲放大器

2011-01-10 11:15:41 88

88 本文探討可以檢測并部署可將輸入信號放大到輸出相等信號的單端/差分音頻放大器的幾種方法。

2012-08-01 16:20:41 16221

16221

介紹了運算放大器的共模電壓的輸入輸出范圍和差分電壓輸入范圍。

2013-09-26 14:47:12 38

38 差動放大電路又叫差分電路,他不僅能有效地放大交流信號,而且能有效地減小由于電源波動和晶體管隨溫度變化而引起的零點漂移,因而獲得廣泛的應用。特別是大量的應用于集成運放電路,他常被用作多級放大器的前置級。

2017-05-15 14:55:18 42478

42478

二次諧波失真并提高信噪比,還可提供一種與現代差分輸入ADC連接的簡單方式。 圖1顯示了低功耗全差分儀表放大器電路的實現方式,該儀表放大器由OP2177精密低功耗雙運算放大器(IC1)和AD8476全差分放大器/ADC驅動器(IC2)級聯而成。該復合

2017-11-16 10:30:31 24

24

該電路示出了一款用于從一個單端輸入產生一個差分信號的電路。差分輸出噪聲是放大器噪聲、電阻器 R1 和 R2 的噪聲、以及噪聲帶寬的一個函數。例如:倘若 R1 和 R2 各為 200W,則差分輸出

2018-06-29 18:41:04 838

838 半導體公司提供全差分放大器只有幾年時間,但這種放大器在示波器等尖端電子領域已經使用幾十年了。這種差分放大器不僅在輸入端而且在輸出端都是差分,因此具有雙倍的輸出范圍。全差分單片放大器與地隔離,可明顯改善波形質量,用于驅動高分辨率ADC和其它高性能(高速和精密)放大器應用。

2018-11-02 17:19:14 2902

2902

和51Ω匹配電阻加到OPA660內部OTA的3腳和 1放大器輸入端5腳,由 1放大器6腳輸出到OTA的2腳,差分放大后由OPA660輸出端8腳送到緩沖放大器BUF600,經過緩沖放大器BUF601緩沖后輸出。

2019-01-09 18:37:02 868

868 采用小尺寸工藝設計的高性能ADC通常采用1.8V至5V單電源或±5V雙電源供電。

2019-04-12 15:19:58 5143

5143

的FDDI接收機和SONET/SDH接收機。這種高帶寬支持超過300mbps的數據速率。差分輸出直接驅動ECL,或驅動比較器/光纖后放大器。除了光纖應用外,這種低成本的硅替代GaAs基跨導放大器非常適合需要寬動態范圍前置放大器或單端到差分轉換的系統。該集成電路可與標準ECL電源(–

2020-04-09 08:00:00 1

1 ADA4830-1/ADA4830-2:高速差動放大器,輸入具有電池短路保護功能

2021-03-19 01:56:30 6

6 MT-068:差動放大器和電流檢測放大器

2021-03-21 01:48:59 11

11 MT-041:運算放大器輸入和輸出共模與差分電壓范圍

2021-03-21 10:37:32 5

5 AD8390A:低功耗、高輸出電流差動放大器數據表

2021-04-18 13:28:14 2

2 AD8015:寬帶/差分輸出跨阻放大器數據表

2021-04-28 15:38:59 7

7 LT1567演示電路-差動輸出放大器的單端輸入

2021-06-04 10:52:20 1

1 LT1567演示電路-差分輸入至單端輸出放大器

2021-06-08 08:28:04 47

47 大學電子課程說明了理想運算放大器的應用,包括反相和同相放大器。然后將這些組合在一起以創建一個差動放大器。經典的四電阻差動放大器(如圖1所示)非常有用,在教科書和文獻中已有40多年的描述。

2023-02-02 14:07:40 3227

3227

,我們將深入討論差動放大電路和差分放大電路的原理和應用。下面是詳實、細致的討論。 一、差動放大電路的原理 差動放大器是一種電路,它采用了差分放大器的前級和共模反饋電路的后級。差動放大器的主要特點是它可以提供高

2023-08-27 16:13:19 13918

13918 。 具體來說,雙差分放大電路由兩個差動放大器組成。每個差動放大器有兩個輸入端和一個輸出端。輸入端分別連接上兩個輸入信號,而輸出端則連接上電路的負載。其中,差動放大器的兩個輸入端中,一個被稱為正輸入,另一個則被稱為負輸入

2023-09-04 17:00:14 4857

4857 差動放大器怎樣進行靜態調零?? 差分放大器是一種電路,通常用于放大差分信號。它有許多應用場合,如放大傳感器的差分輸出信號、在放大線路中對共模噪聲進行抵消等。在進行差分放大器的操作時,靜態調整是非

2023-09-19 17:43:18 10254

10254 為什么差動放大器的輸出會受到共模輸入的影響? 差動放大器是一種常見的電子電路,它是由兩個輸入端口和一個輸出端口組成的。它通過對兩個輸入信號進行差分放大,將差分信號放大后輸出,從而實現信號的增益。然而

2023-11-20 16:28:54 2151

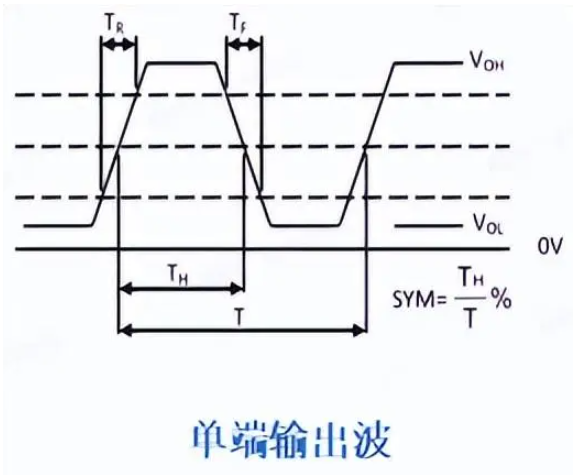

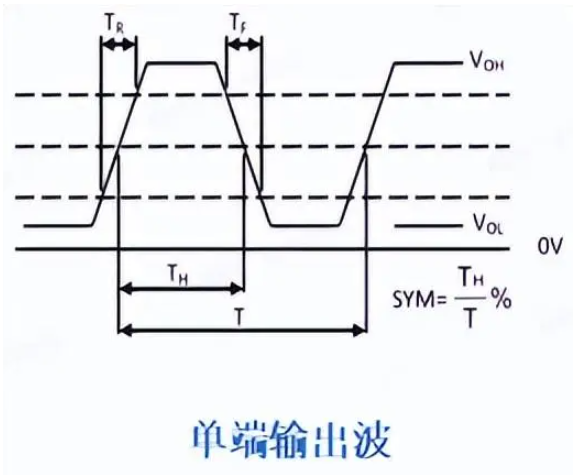

2151 什么是差分輸出方式?什么東西會影響差分輸出幅值呢? 差分輸出方式是一種電路設計技術,常用于提取信號的變化情況,以及對信號進行放大和處理。它可以將輸入信號通過差動放大器進行放大,然后輸出兩個相位

2023-11-20 16:36:00 3589

3589 電子發燒友網站提供《差動放大器和電流檢測放大器.pdf》資料免費下載

2023-11-23 11:10:20 2

2 運算放大器采用差分放大是因為差分放大器具有以下幾個優點

2024-01-04 18:16:18 1888

1888 不同的放大器也有對應的輸出接法及注意事項,本期就為此介紹說明:高壓放大器有三種輸出接法:差分輸出、單端輸出(可接地)、單端輸出(不可接地)差分輸出差分輸出接法如圖1所

2024-01-12 08:13:07 1018

1018

電子發燒友網站提供《將差分輸出(隔離式)放大器連接到單端輸入ADC.pdf》資料免費下載

2024-09-05 09:58:48 8

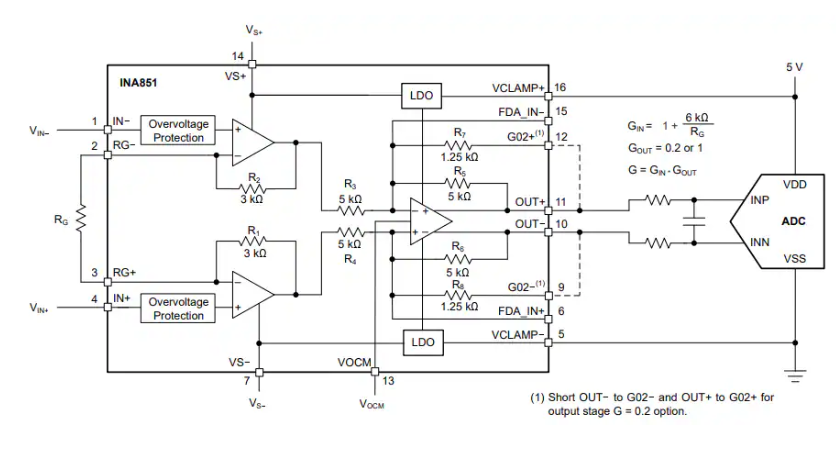

8 Texas Instruments INA851全差分儀表放大器是具有全差分輸出的高精度儀表放大器。INA851優化用于驅動具有全差分輸入的現代高性能模數轉換器 (ADC) 輸入。該放大器可在非常

2025-09-08 10:20:29 893

893

電子發燒友App

電子發燒友App

評論