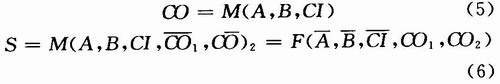

O 引言 加法運算是算術運算中最基本的運算。減法、乘法、除法及地址計算這些基于加法的運算已廣泛地應用于超大規(guī)模集成電路(VLSI)中。全加器是組成二進

2010-10-19 10:57:22 6716

6716

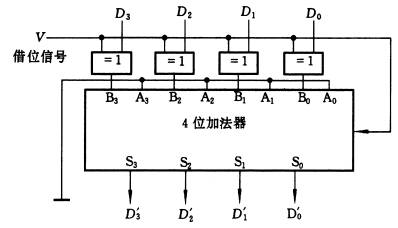

多位二進制減法器,是由加法電路構成的;在加法電路的基礎上,減法與加法采用同一套電路,實現(xiàn)加減法共用。

2020-09-01 16:02:09 24701

24701

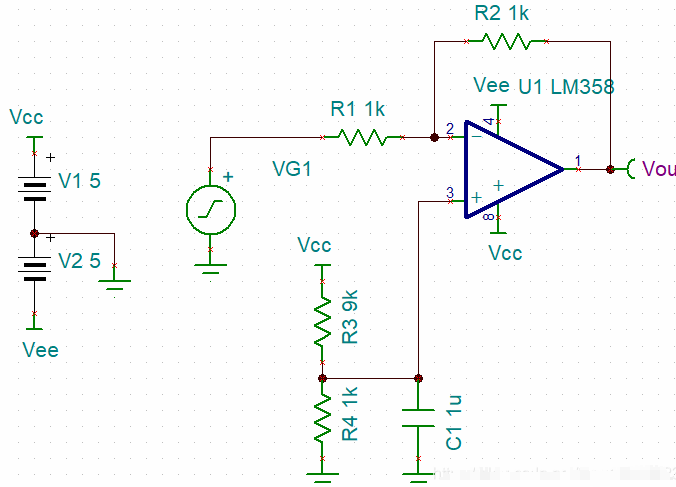

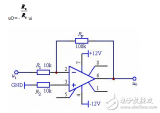

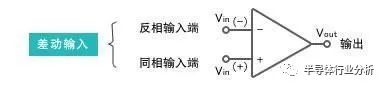

運算放大器之所以被稱為運算放大器,沒有叫A放大器或者B放大器,那是因為這種結構可以做運算,比如積分,微分,加法,減法呀等等。

2022-07-13 14:16:14 5887

5887 運算放大器之所以被稱為運算放大器,沒有叫A放大器或者B放大器,那是因為這種結構可以做運算,比如積分,微分,加法,減法呀等等。

2022-07-13 14:15:55 52084

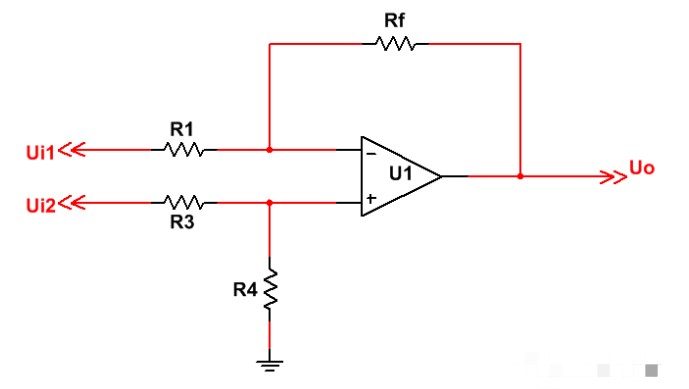

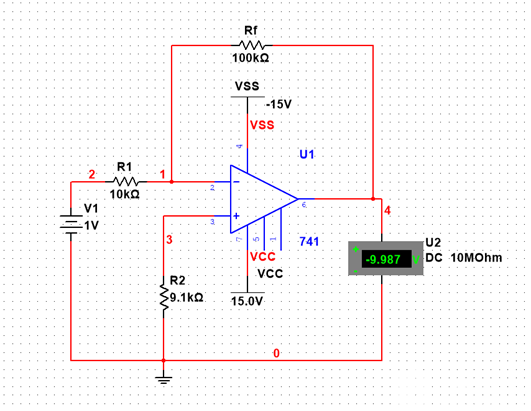

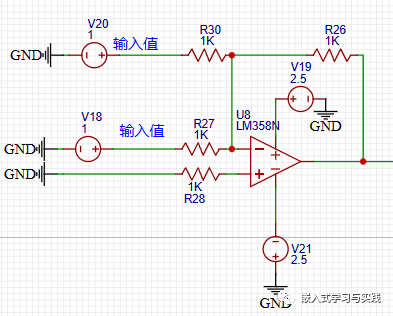

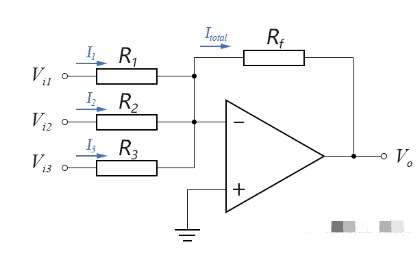

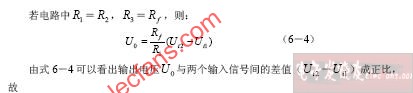

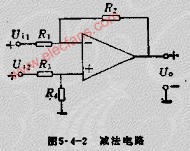

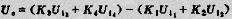

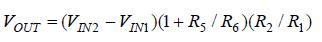

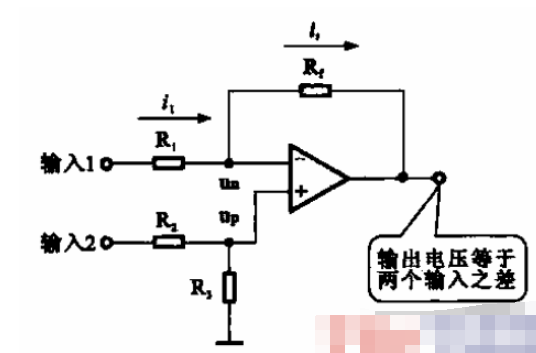

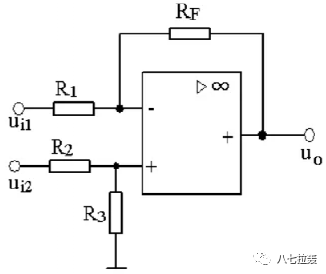

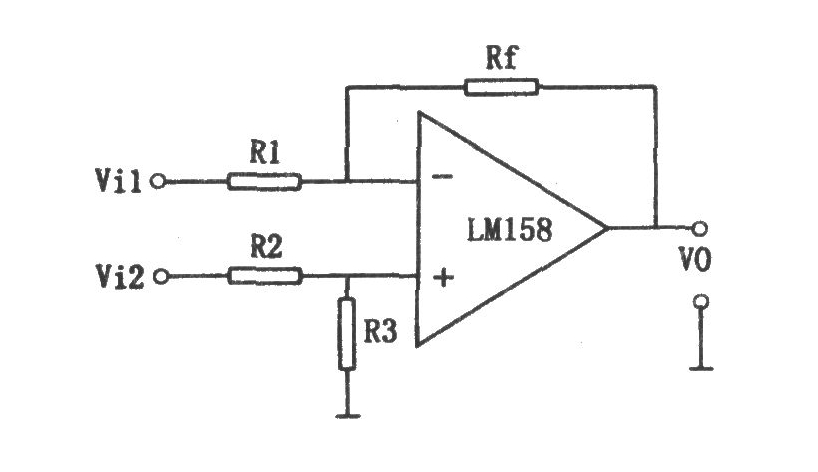

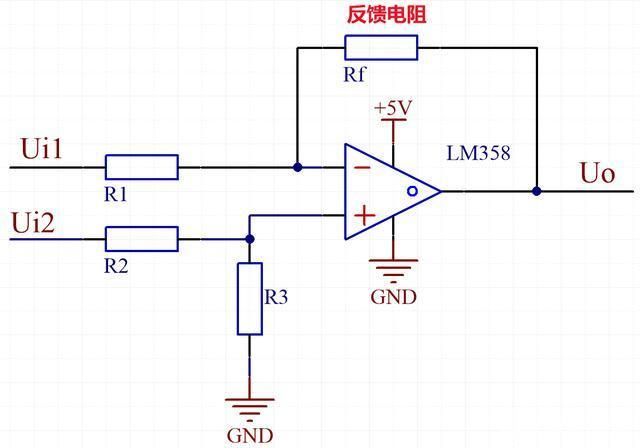

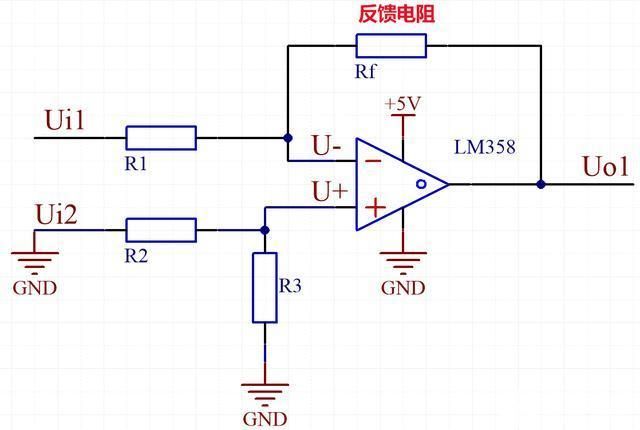

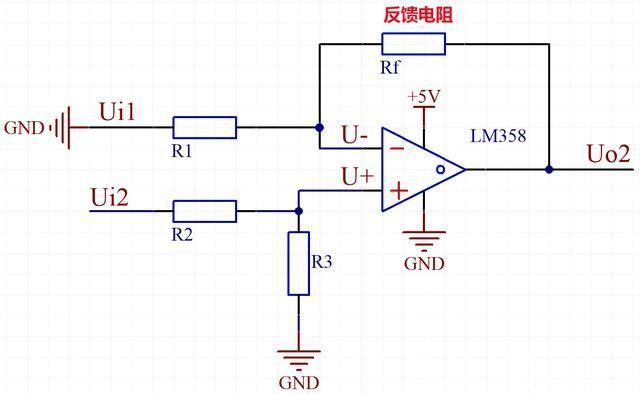

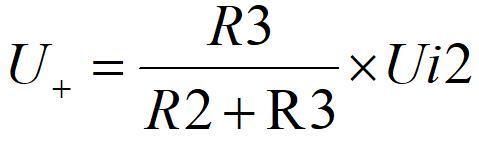

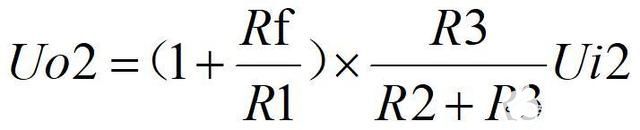

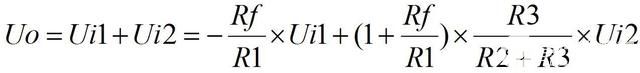

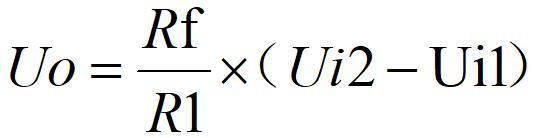

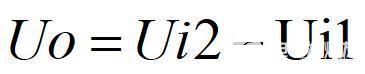

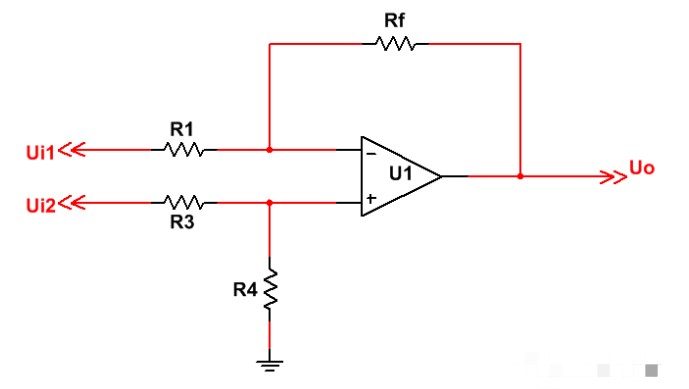

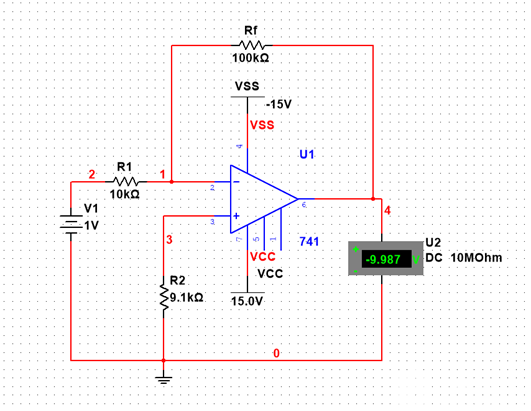

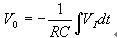

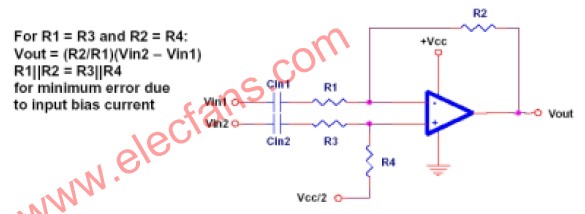

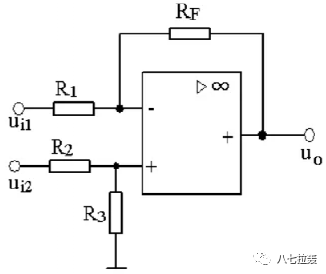

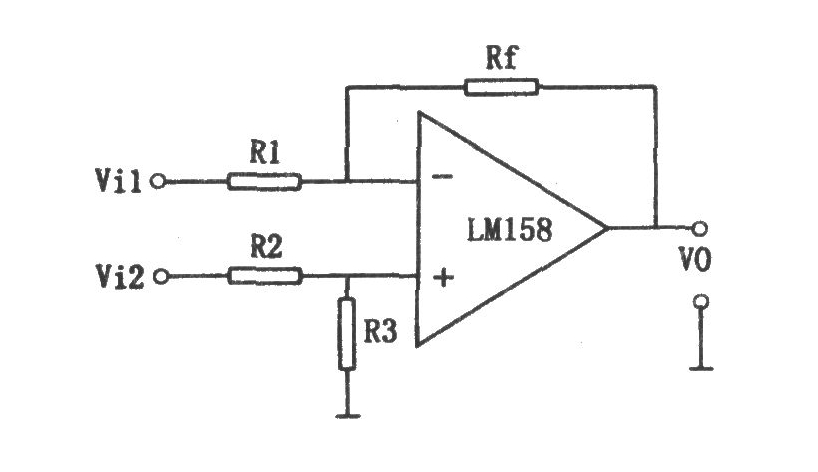

52084 兩個輸入信號 Ui1 和 Ui2 分別通過電阻 R1 和 R2 與運算放大器的反相輸入端、以及同相輸入端相連接;運算放大器的同相輸入端對地 接有電阻 R3;反饋電阻 Rf 使運放工作在線性區(qū),具有“虛短”、“虛斷”兩個特性。

2022-09-05 15:58:35 75968

75968

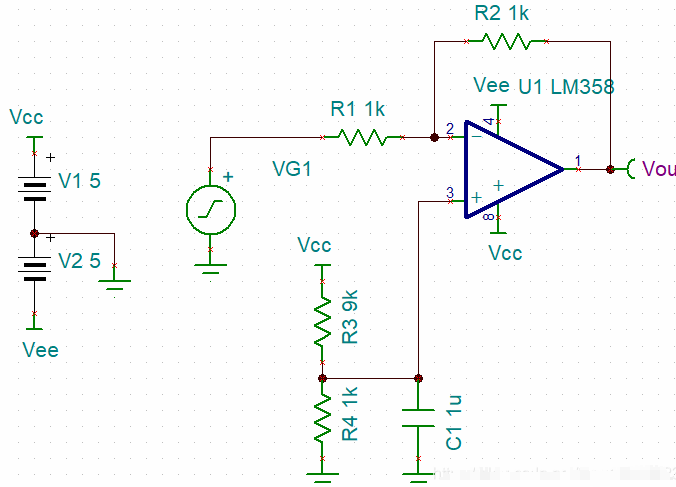

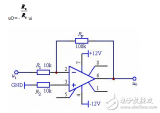

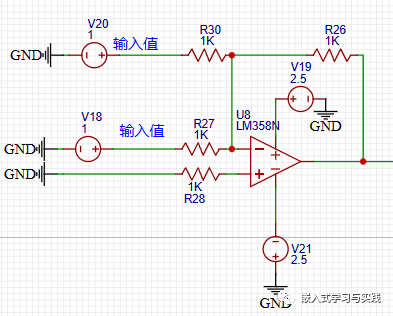

本文是采用運放構建減法電路來控制直流偏執(zhí)。

2022-11-07 16:33:57 3052

3052

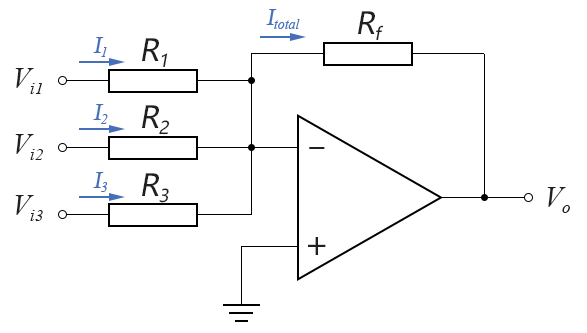

前面的反相放大器和同相放大器可以實現(xiàn)乘法運算的功能,這一小節(jié)我們來看如何用運放實現(xiàn)加減法運算。

2023-02-02 14:12:24 56025

56025

的加減法運算電路輸入輸出關系的一般計算公式。在此基礎上,利用Multisim 軟件輔助設計單運放結構的加減法運算電路。

2023-02-08 11:37:16 6397

6397

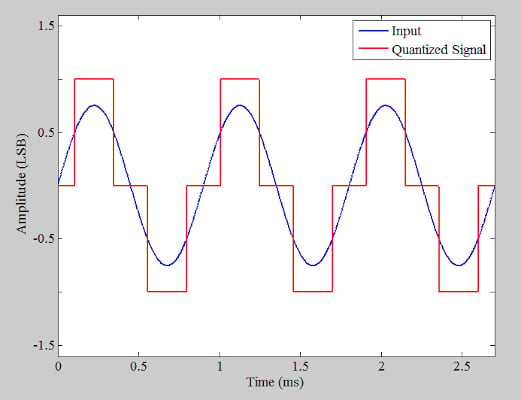

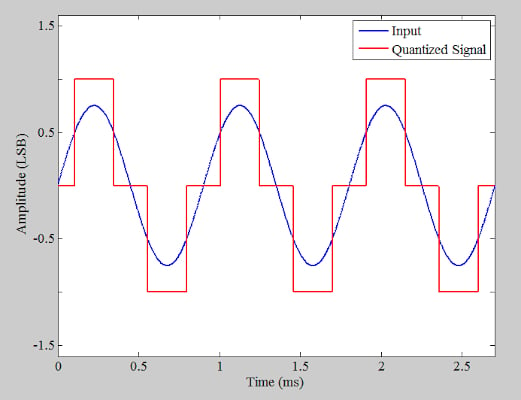

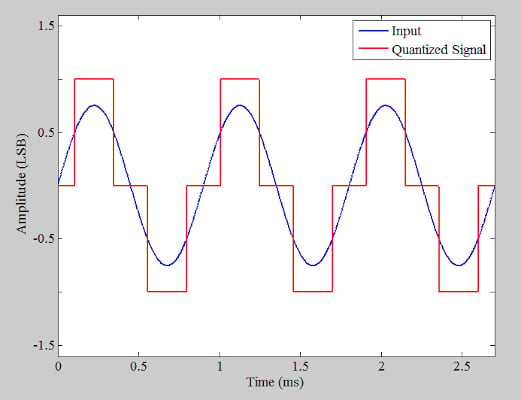

了解抖動如何抑制諧波和非諧波雜散以及兩種不同類型的抖動系統(tǒng):減法和非減法拓撲。

2023-02-27 14:25:08 2439

2439

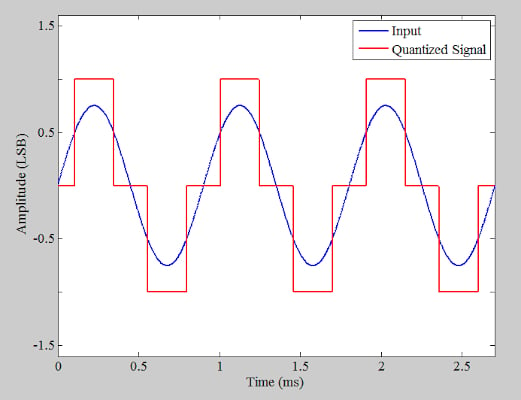

了解抖動如何抑制諧波和非諧波雜散以及兩種不同類型的抖動系統(tǒng):減法和非減法拓撲。 量化小幅度信號會在量化誤差和輸入之間產(chǎn)生相關性,從而導致明顯的諧波分量。高頻諧波可以混疊回奈奎斯特間隔,其頻率可能是

2023-05-03 11:14:00 2268

2268

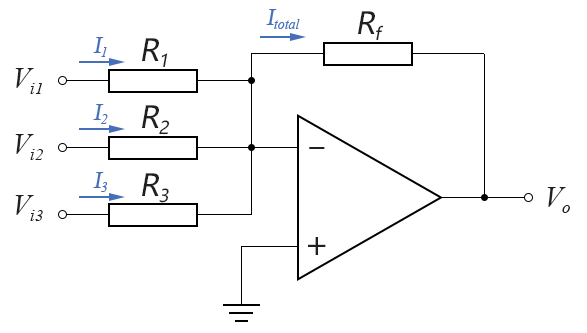

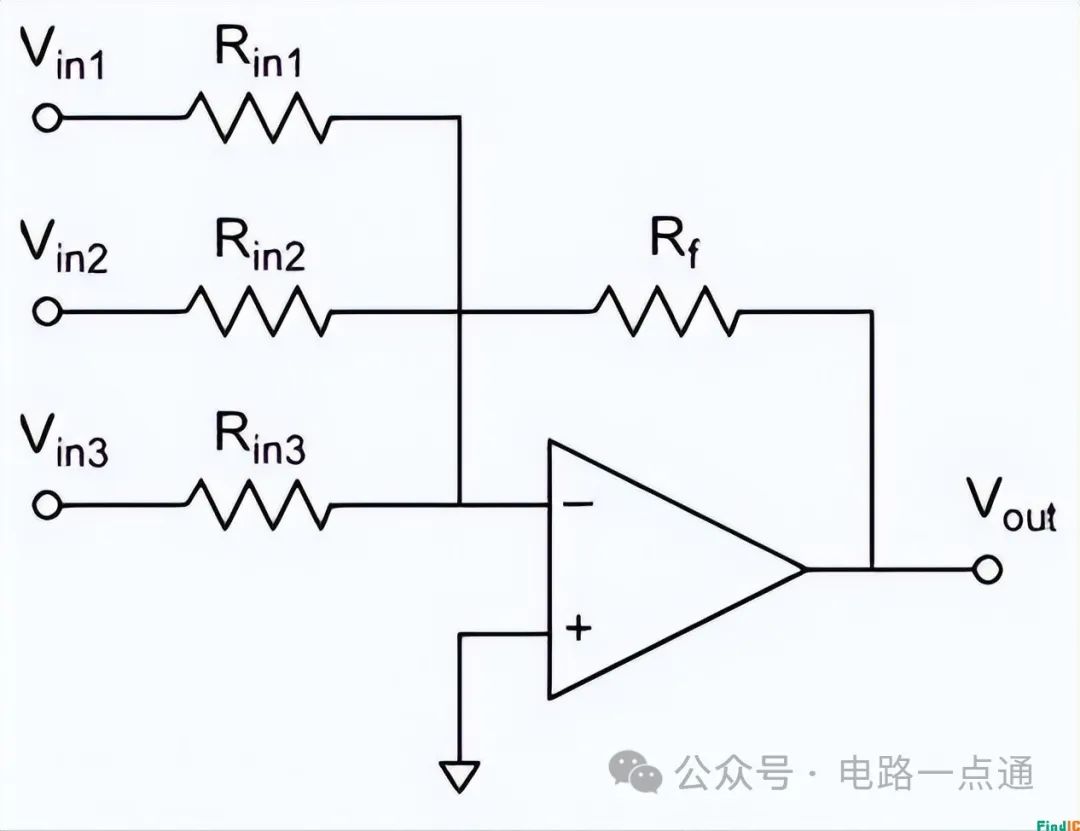

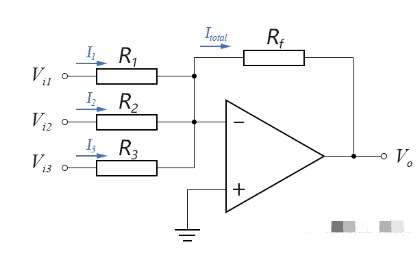

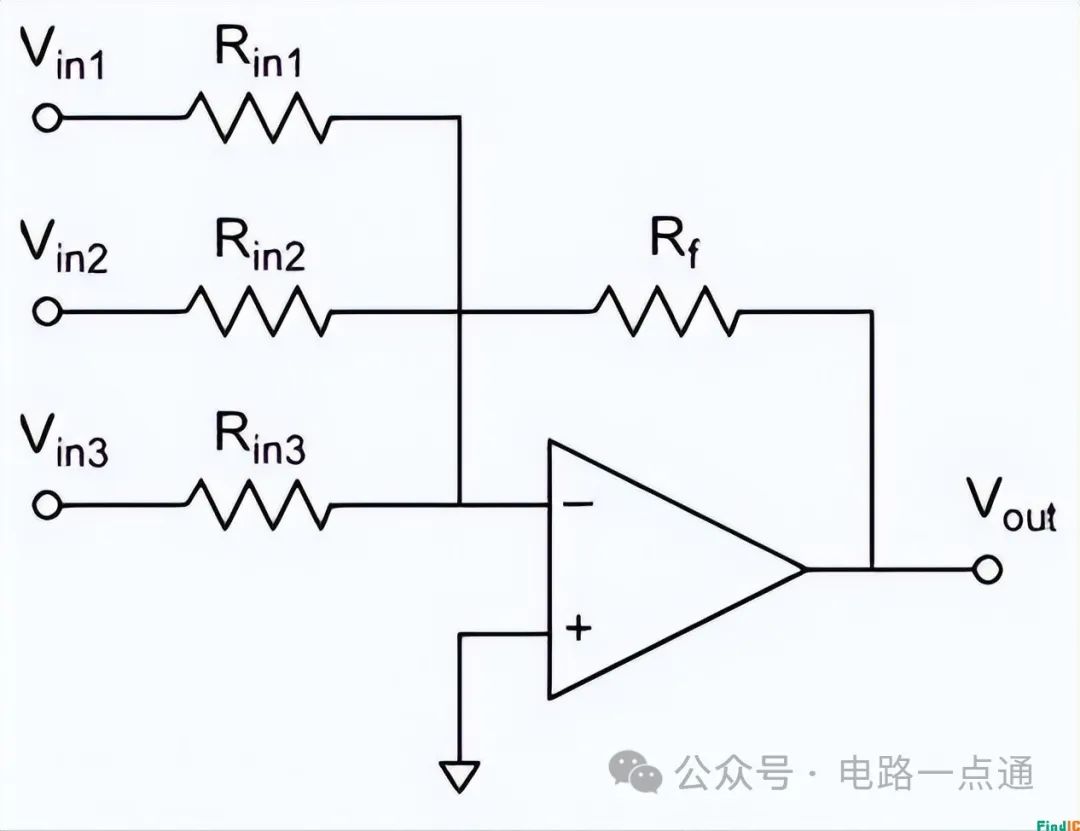

可看出輸出值與輸入值的和成反比關系,所以叫反相加法運算電路。

2023-08-08 15:41:56 15112

15112

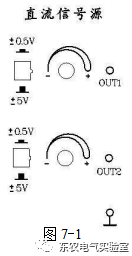

掌握用集成運算放大器組成的比例、加法、減法、積分等運算電路的性能及其測試方法。

2023-10-10 16:23:22 15328

15328

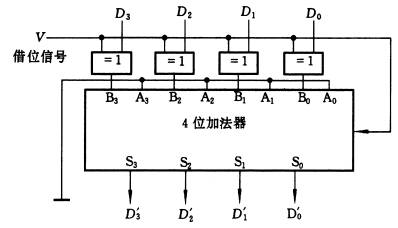

減法器是一種電路,它可以實現(xiàn)二進制數(shù)字的減法運算。減法器的工作原理基于位運算和進位/借位機制。

2024-02-19 09:36:37 12173

12173

加法運算的電路如下圖所示,輸出電壓為若干個輸入電壓的比例和

2024-02-19 09:52:06 11102

11102

減法電路是基本集成運放電路的一種,算術運算電路主要包括數(shù)字**加法器電路、數(shù)字減法器電路、數(shù)字乘法器電路和數(shù)字除法器電路。

2024-02-19 10:00:17 1795

1795

前段時間動手做了個小項目,跟大家分享一下!可實現(xiàn)4位帶進位加法/減法計算。目前負值無法顯示,只顯示負數(shù)絕對值。對實例1中的顯示部分有優(yōu)化。目前已實現(xiàn)計算器功能,但程序有待優(yōu)化。遙控板測試說明(紅外):—:表示減法+: 表示加法EQ:表示計算/等于

2015-01-20 17:15:24

,51單片機處理浮點數(shù)會浪費大量時間。2、本例使用單片機的P0口和P1口分別顯示兩個無符號字符型數(shù)據(jù)的加法和減法的運算結果3、在kei c51中新建工程文件ex6,輸入如下的程序代碼,編譯并生成

2012-03-21 16:55:33

動態(tài)顯示子程序流程圖(3)鍵盤掃描子程序流程圖(4)溢出報錯子程序(5)清零子程序(6)運算數(shù)值輸入計算子程序(7)加法計算子程序(8)減法計算子程序(9)乘法計算子程序(10)除法計算子程序(11)顯示子程序(五)結束語(一)前言本文是簡單計算器的設計。使用的是AT89S52芯片,C語言

2021-11-09 08:03:10

).所以我被搞蒙了減法器應該是差分比例運算電路中,當放大倍數(shù)為1時的情況下才是減法器吧,如果要倍數(shù)為1,不就是R1= R2=Rf=R3了。我的理解對嗎???各路英雄

2017-02-25 19:16:55

接地,輸出才是0但是現(xiàn)在我想的是能夠做成一個減法運算放大電路,使得我的傳感器的輸出2.1~2.7V經(jīng)過運放后 轉(zhuǎn)換為0~3.3V 的然后給我的單片機經(jīng)行AD轉(zhuǎn)換大家有誰給我一個方案?或者是其他的運放也行

2015-04-25 21:35:50

如圖所示運算放大電路,SW1為IO口控制信號,VREF電源電壓為2.495V,請問FB1處電壓范圍為多少,如何計算的?麻煩各位大神了

2022-03-09 12:00:58

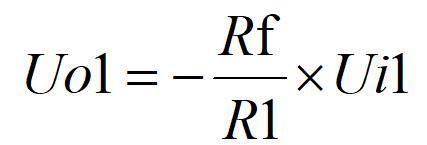

請高手分析以下圖片中集成運算放大電路的Uo1, Uo2, Uo3的電壓如何計算, 直流成份即可.

2023-03-17 10:27:58

DN15- 運算放大器電路中的噪聲計算

2019-08-02 14:22:18

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-17 08:10:29

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-10 07:04:46

在FPGA中一般減法是怎么處理的呢?比如A-B是采用A+B的補碼,還把A和B都定義成有符號的類型,直接進行減法運算呢?

2014-12-24 09:46:57

TVS的作用,R5和R105的作用,及驅(qū)動的電路的工作原理運算放大的輸出電壓計算公式

2017-08-13 10:09:29

請教大家怎么用VHDL語言實現(xiàn)減法運算?在FPGA設計時又該怎么操作呢?

2012-05-17 20:07:12

Windows -編程-數(shù)值運算Rust 支持所有數(shù)字類型的基本數(shù)學運算:加法、減法、乘法、除法和余數(shù)。以下代碼顯示了如何在let語句中使用每一個:誠接Windows驅(qū)動開發(fā)外包文件名:src

2021-08-24 14:36:35

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-17 07:11:32

所需運算放大器增益帶寬積進行基本穩(wěn)定性分析,我們將獲得本步驟背后的邏輯,如果您只想進行計算,可以直接跳到公式 5。圖 1 是用于分析的 TINA-TI? 電路。反饋環(huán)路使用大電感器 (L1) 中斷,而

2018-09-13 15:10:54

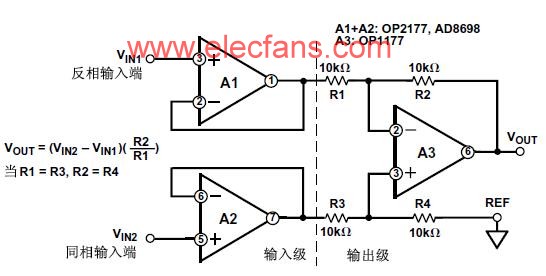

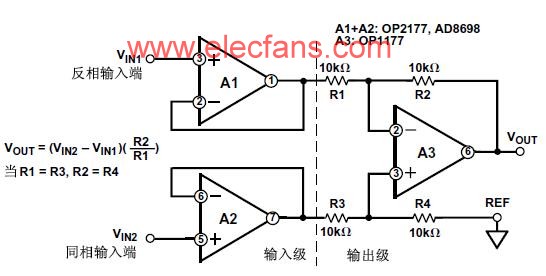

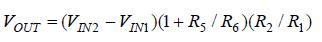

比如一個傳感器的輸出是2個信號電壓,一正一負。其電壓差值與傳感器數(shù)值成一 一對應關系。所以要做一個雙端輸入單端輸出差分放大電路或是減法運算電路。應該怎么考慮?普通的運算放大器大多都是雙端差分輸入,那么在這個應用場景下,雙端輸入單端輸出差分放大電路和減法運算電路相同。

2019-08-13 12:40:28

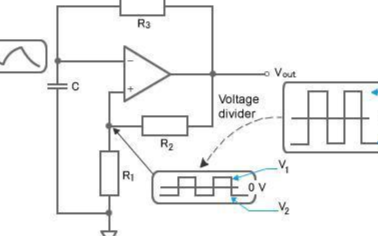

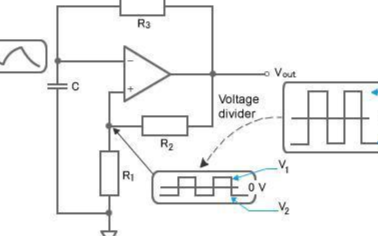

下圖哪一個電路是減法器?按照書上的電路,減法器應該構成負反饋,可是把運放接成正反饋之后,輸出卻沒有變化,那么負反饋或者正反饋在電路中的作用是什么呢?問題來自論壇里的這個電路,看到構成的是正反饋

2017-08-31 19:46:42

馮·諾依曼機工作方式的基本特點是什么?計算機系統(tǒng)中采用補碼運算的目的是什么?在定點二進制運算器中,減法運算一般通過什么來實現(xiàn)?在定點數(shù)運算中產(chǎn)生溢出的原因是什么?和外存儲器相比,內(nèi)存儲器的特點是什么?

2021-08-11 08:44:26

模信號不為0,等于Ui電壓,這就要求運放應有較高的最大共模輸入電 壓和較高的共模抑制比。 在實際應用的電路復雜多變,但萬變不離其宗,判定運算類型,可記住公式直接套用,不知道的情況下,根據(jù)運算的虛斷與虛短進行計算。

2021-02-20 16:29:04

差分運算放大電路,對共模信號得到有效抑制,而只對差分信號進行放大,因而得到廣泛的應用。差分電路的電路構型圖1 差分電路目標處理電壓:是采集處理電壓,比如在系統(tǒng)中像母線電壓的采集處理,還有像交流電

2021-02-25 11:06:01

要求:由2-10進制編碼器編碼,加法電路構成減法電路,用一個發(fā)光二極管表示正負狀態(tài),數(shù)碼管顯示減法結果。

2018-05-02 15:46:46

比例求和運算電路實驗實驗目的1. 掌握用集成運算放大器組成比例,求和電路的特點及功能;2. 學會上述電路的測試和分析方法。實驗儀器1. 數(shù)字萬用表;2. 示波器;3. 信號發(fā)生器。預習要求1. 計算

2009-05-15 00:38:13

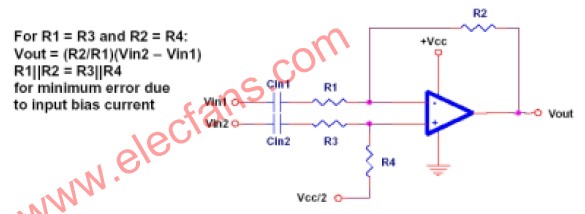

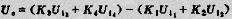

/ R2)+等)電壓加法運算放大器電路電壓減法器 減法器也稱為差分放大器,它使用反相和同相輸入來產(chǎn)生輸出信號,該信號是兩個輸入電壓V1和V2之差,從而允許一個信號與另一個信號相減。如果需要,可以添加

2022-04-25 10:24:44

加法運算放大器電路電壓減法器減法器也稱為差分放大器,它使用反相和同相輸入來產(chǎn)生輸出信號,該信號是兩個輸入電壓V1和V2之差,從而允許一個信號與另一個信號相減。如果需要,可以添加更多的輸入以將其減去

2021-01-07 09:38:43

有一個電流,用電流傳感器實時采樣得到的對應轉(zhuǎn)換電壓范圍為2.5~3.2V,但是我現(xiàn)在想得到的輸出信號為0 ~ 1.4V,所以用了如圖這個減法電路,請大家看看是否可行?此外,假如可行的話用這個運放是否

2019-01-16 16:44:26

矩陣運算中的初始化/加法/逆矩陣和減法,看完你就懂了

2021-11-19 07:02:39

,最終變量b的值是152.減法運算符 或 負值運算符 - 1 1> 在第1行利用減法運算符 - 進行了減法運算,再將差賦值給了變量b,最終變量b的值是52> 在第3行中,這個 - 并不是什么...

2021-11-30 06:09:47

FPGA如何實現(xiàn)32位減法運算

2019-02-28 04:59:09

hValue = (u16)(-Theta);hValue = 0x166-hValue;//我想在這一步實現(xiàn)減法運算,但是使用ST-link 進行仿真的時候發(fā)現(xiàn),hValue 的值并沒有發(fā)生變化?請教大家一下,在STM32中,如何實現(xiàn)減法運算呢?

2019-01-17 01:04:46

8位單片機能夠?qū)崿F(xiàn)超長數(shù)計算嗎?我說:"只要存儲器夠大,按照下面的方法設計的加減法運算器及指令,就能夠編寫程序完成。"1。用全加器搭建一個8位加法器;2。將最低下進位前連接一個1位寄存器,輸入端連接

2014-09-22 03:09:55

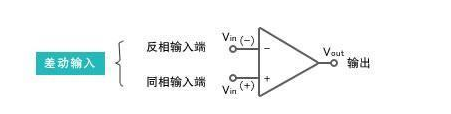

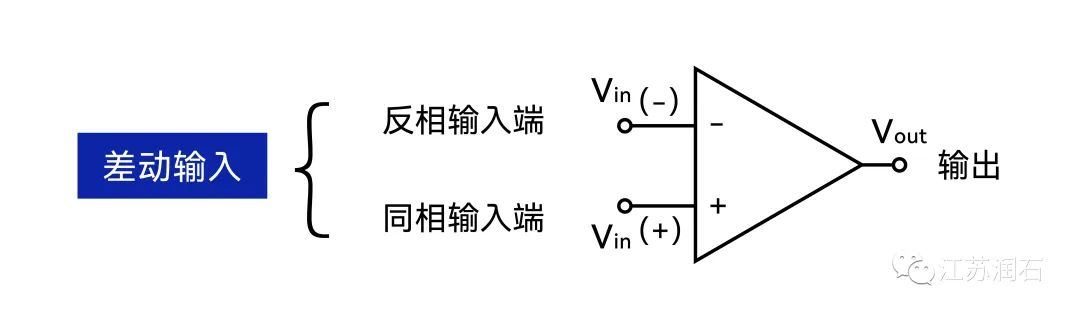

集成運算放大電路實驗實驗目的1. 了解集成運算放大器的特點。2. 掌握集成運算放大器在信號運算方面的應用。實驗原理集成運算放大器按照輸入方式可以分為同相、反相、差分三種接法,按照輸入電壓與輸出電壓

2008-09-25 17:25:06

集成運算放大電路實驗實驗目的1. 了解集成運算放大器的特點。2. 掌握集成運算放大器在信號運算方面的應用。實驗原理集成運算放大器按照輸入方式可以分為同相、反相、差分三種接法,按照輸入電壓與輸出電壓的運算關系可以分為比例、加法、減法、積分、微分等,輸入方式和運算關系組合起來,可以構成各種運算放大器。

2008-12-11 23:27:49

集成運算放大電路實驗實驗目的1. 了解集成運算放大器的特點。2. 掌握集成運算放大器在信號運算方面的應用。實驗原理集成運算放大器按照輸入方式可以分為同相、反相、差分三種接法,按照輸入電壓與輸出電壓的運算關系可以分為比例、加法、減法、積分、微分等,輸入方式和運算關系組合起來,可以構成各種運算放大器。

2008-09-22 12:18:59

1.運放的傳輸特性2.比例器、加法器、減法器、跟隨器等運算電路3.含理想運放的運算電路的分析計算 難點 熟練計算含理想運放的思路 運放的電路模型

2009-07-08 09:09:19 0

0 集成運算放大器是一種高增益的直流放大器。它有兩個輸入端,一個輸出端。外接負反饋電路后能夠完成反相比例,同相比例,加法、減法、乘法,微分、積分等運算功能。現(xiàn)

2008-09-24 22:07:42 19421

19421

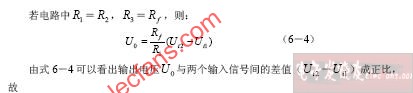

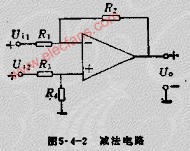

減法運算電路

圖6-4 減法運算電路

2009-03-09 10:11:43 6372

6372

減法運算

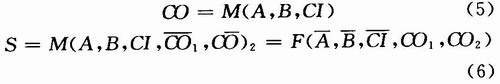

同加法運算一樣,減法運算可采用減法器來實現(xiàn)。半減器和全減器的設計方法和步驟與設計加法器相同。實用上,為了簡化系統(tǒng)結構,通常不另外設計減

2009-04-07 10:38:39 14489

14489

補碼加、減運算規(guī)則

在計算機中,通常總是用補碼完成算術的加減法運算。其規(guī)則是: [X+Y]補= [X]補 + [Y]補 ,[X-Y]

2009-10-13 22:46:58 11442

11442

補碼減法,補碼減法原理是什么? 負數(shù)的減法運算也要設法化為加法來做,其所以使用這種方法而不使用直接減法,是因為它可以和常規(guī)的加法運算使用同一

2010-04-13 11:45:46 7231

7231 浮點運算與浮點運算器

浮點加減法的運算步驟 設兩個浮點數(shù) X=Mx※2Ex Y=My※2Ey 實現(xiàn)X±Y要用如下5步完成: ①對階操作:小階

2010-04-15 13:42:32 7293

7293 減法電路

減法電路和加法電路實質(zhì)相同,在求和電路中預先將某些信號倒相就可以成為求差電路或混合電路。

差動輸入運算放大器

2010-04-22 17:46:36 20750

20750

加減法電路

利用一個差動輸入的運放就可同時實現(xiàn)加減法運算,這種運算電路如圖5.4-3所示。

2010-04-22 17:50:08 11134

11134

減法器電路

一個通常的應用就是用于去除立體聲磁帶中的原唱而留下伴音(在錄制時兩通道中的原唱電平是一樣的,但是伴音是略有不同的)。

2010-04-24 10:45:35 10142

10142

由輸入端選擇運算方式的加、減法運算電路

電路的功能

這是一種配

2010-05-08 11:32:23 2057

2057

高輸入電阻減法運算電路(A-B)

電路功能

因為輸入電阻高,所以信

2010-05-08 13:16:38 6121

6121

用于比率計算的除法運算電路

電路的功能

本電路是用X除輸入信號Z

2010-05-08 15:29:01 2003

2003

帶輸入緩沖的減法器電路

2010-09-04 21:32:57 3223

3223

帶增益緩沖放大器的緩沖減法器電路

2010-09-04 21:40:59 3554

3554

基于改進譜減法的語音

2011-01-06 16:53:23 32

32 運算放大器是一種有著十分廣泛用途的電子器件。最早開始應用于1940年,主要用于模擬計算機,由于可以模擬加法、減法、積分等運算而得名。1960年后,隨著集成電路技術的發(fā)展,運

2011-03-30 17:14:40 178

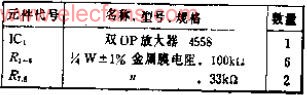

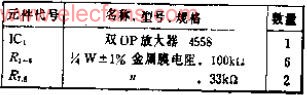

178 本文給出了從同相端輸入的兩運放減法電路,以及1458/1558系列的主要參數(shù)典型值。

2011-11-24 13:55:42 11060

11060

比例運算電路的輸出電壓與輸入電壓之間存在比例關系,即電路可實現(xiàn)比例運算。比例電路是最基本的運算電路,是其他各種運算電路的基礎,本章隨后將要介紹的求和電路、積分和微分電路、對數(shù)和指數(shù)電路等等,都是在比例電路的基礎上,加以擴展或演變以后得到的。

2017-05-14 09:18:23 91291

91291

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網(wǎng)絡所構成的運算電路來實現(xiàn)。

2017-08-16 11:09:48 169731

169731

集成運算放大器是一種具有高電壓放大倍數(shù)的直接耦合多級放大電路。當外部接入不同的線性或非線性元器件組成負反饋電路時,可以靈活地實現(xiàn)各種特定的函數(shù)關系。在線性應用方面,可組成比例、加法、減法、積分、微分、對數(shù)等模擬運算電路。

2017-08-18 17:26:18 27408

27408

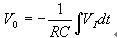

運算電路是集成運算放大器的基本應用電路,它是集成運放的線性應用。討論的是模擬信號的加法、減法積分和微分、對數(shù)和反對數(shù)(指數(shù))、以及乘法和除法運算。

2017-11-27 15:55:10 0

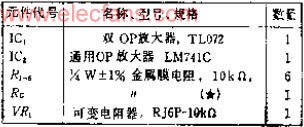

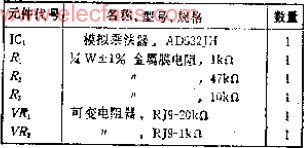

0 本文為大家?guī)砦宸N減法器電路設計方案介紹。

2018-01-17 11:29:44 95059

95059

4.1.3加法和減法運算電路

2019-04-18 06:03:00 17188

17188

本文檔的主要內(nèi)容詳細介紹的是模擬電路實驗教程之基本運算電路的詳細資料說明。一。實驗目的1.掌握反相比例運算、同相比例運算、加法、減法運算電路的原理,設計方法及測試方法。2.能正確分析運算精度與運算電路中各元件參數(shù)之間的關系。

2019-05-27 17:26:51 24

24 運算放大器是一種可以進行數(shù)學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現(xiàn)放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2019-06-23 11:15:15 7599

7599

所示是減法運算電路,訛通過Ri加到運算放大器的反相輸入端,蚰通過R2、R3分壓后加到同向輸入端,而抽通過Rf反饋到反相輸入端。為了使運算放大器兩輸入端平衡,則}Rl/,RrRzllR3。

2020-09-10 11:07:12 34006

34006

運算放大器是一種可以進行數(shù)學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現(xiàn)放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2021-01-01 18:10:00 38245

38245

運算放大器電路中的DN15噪聲計算

2021-04-19 21:15:54 7

7 運算放大器之所以被稱為運算放大器,沒有叫A放大器或者B放大器,那是因為這種結構可以做運算,比如積分,微分,加法,減法呀等等。

2023-02-19 10:00:57 2326

2326 運算放大器是一種可以進行數(shù)學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現(xiàn)放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2023-04-24 14:57:58 8641

8641

運算放大器是一種可以進行數(shù)學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現(xiàn)放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2023-04-24 15:05:39 3265

3265

運算放大器起源于模擬計算機時代,用于進行加、減法、微分、積分等數(shù)學運算,因此被稱為運算放大器,簡稱“運放”。

2023-05-15 18:25:10 10453

10453

本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:13:57 7212

7212

真空衰減法是一種無損、定量的檢測非多孔、剛性或柔性包裝泄漏的方法。壓力衰減測試是一種用于檢測無孔、剛性或柔性包裝中泄漏的定量測量方法。如果加壓氣體的引人導致包裝壁或密封件破裂,則該測試是破壞性

2023-07-27 15:21:41 2253

2253

FPGA實現(xiàn)加法和減法運算非常簡單,實現(xiàn)乘法和除法可以用IP,那實現(xiàn)對數(shù)和指數(shù)運算該用什么呢?

2023-08-05 09:37:05 2191

2191

真空衰減法是一種無損、定量的檢驗非多孔、剛性或柔性外包裝泄漏的方法。壓力衰減檢測是一種用于檢驗無孔、剛性或柔性外包裝中泄漏的定量測量方法。假如增壓氣體的讓人造成外包裝壁或密封材料裂開,那么該檢測

2023-08-29 14:14:37 1226

1226

在電子技術的海洋中,有一種電路如同數(shù)學中的加法器一樣,能夠?qū)⒉煌男盘栠M行相加處理。這就是被廣泛應用于信號處理領域的反相加法運算電路。

2024-02-17 15:34:00 9188

9188

元器件的限制。當時,計算機的電路設計主要采用位操作(二進制)來實現(xiàn)。為了能夠有效地表示負數(shù),人們引入了反碼的概念。使用反碼可以使計算機系統(tǒng)在進行加法和減法運算時使用相同的邏輯電路,從而降低了硬件成本和復雜度。 2.

2024-02-19 15:10:32 1809

1809 Unit)是CPU中負責執(zhí)行算術和邏輯運算的部分。它的主要作用包括: 1.1 算術運算:運算器可以執(zhí)行各種算術運算,如加法、減法、乘法、除法等。這些運算是計算機處理數(shù)據(jù)的基礎。 1.2 邏輯運算:運算器還可以執(zhí)行邏輯運算,如與(AND)、或(OR)、非(NOT)、異或(XOR)等

2024-06-30 11:15:58 5487

5487 運放減法電路是一種常見的模擬電路,它利用運算放大器(Operational Amplifier,簡稱Op-Amp)的特性來實現(xiàn)兩個模擬信號的減法運算。 一、運放減法電路的工作原理 運算

2024-07-12 11:44:12 2999

2999 運放減法電路是一種常見的模擬電路,它利用運算放大器(Operational Amplifier,簡稱Op-Amp)的特性來實現(xiàn)兩個模擬信號的減法運算。這種電路在信號處理、數(shù)據(jù)采集、傳感器信號調(diào)理等

2024-07-12 11:48:34 3690

3690 運放減法電路是模擬電路中的一種基本電路,廣泛應用于信號處理、數(shù)據(jù)轉(zhuǎn)換、濾波器等領域。在運放減法電路中,兩個輸入信號經(jīng)過運算放大器(Op-Amp)進行減法運算,得到輸出信號。本文將詳細介紹運放減法電路

2024-07-15 09:40:58 2346

2346

電子發(fā)燒友App

電子發(fā)燒友App

評論