減法器電路與原理

減法器是一種電路,它可以實現二進制數字的減法運算。減法器的工作原理基于位運算和進位/借位機制。

常見的減法器有硬件實現的二進制減法器和軟件實現的程序減法器。硬件實現的減法器通常是由一組異或門(XOR)、與門(AND)和或門(OR)組成,而軟件實現的減法器則可以在計算機程序中實現。

在二進制減法中,如果第二個操作數是被減數,則第一個操作數是減數。減數和被減數的每一位分別被進行異或運算,然后再進行與運算,以確定是否需要進位/借位。通過這種方式,減法器可以實現二進制數的減法運算。

減法器是一種用于實現二進制數減法運算的電路,它通過使用異或門、與門和或門來實現二進制減法運算的進位/借位機制。

減法器電路圖分享

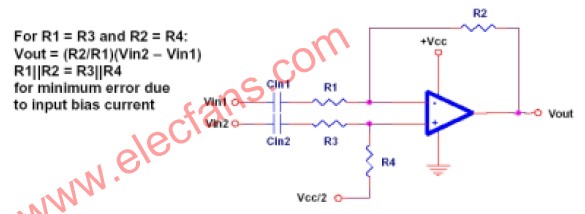

通用減法器電路

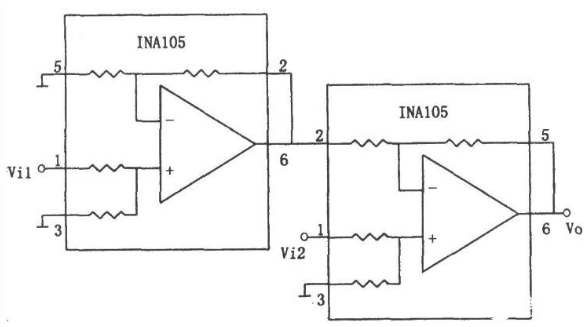

圖(a)電路輸入輸出關系為:V0=Vi2-Vi1圖中放大器的輸出信號電壓極性通常與輸入電壓極性相同。如果要求反相輸出,則采用圖(b)所示電路。其輸入輸出關系為:Vo=Vi1-Vi2。

INA105構成的減法電路

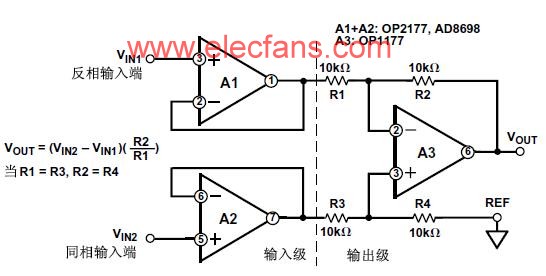

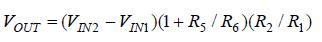

如圖所示為其他器件組成的減法電路(2)。該電路輸入輸出關系為:Vo=Vi2-Vi1。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

放大器

+關注

關注

146文章

14345瀏覽量

222033 -

二進制

+關注

關注

2文章

809瀏覽量

43029 -

減法器

+關注

關注

1文章

26瀏覽量

17380

發布評論請先 登錄

相關推薦

熱點推薦

8位減法器求解?

給出1位全減器的Verilog描述。要求: (1) 首先設計1位半減器,然后用例化語句將它們連接起來,圖3-32中h_suber是半減器,diff是輸出差,s_out是借位輸出,sub_in是借位輸入。 (2) 以1位全減器為基本硬件,構成串行借位的8位減法器,要求用例

發表于 10-08 19:59

哪一個是減法器?負反饋在減法器電路中的原理?

下圖哪一個電路是減法器?按照書上的電路,減法器應該構成負反饋,可是把運放接成正反饋之后,輸出卻沒有變化,那么負反饋或者正反饋在電路中的作用是

發表于 08-31 19:46

本的二進制加法/減法器,本的二進制加法/減法器原理

本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸

發表于 04-13 11:11

?5508次閱讀

減法器電路與原理 減法器電路圖分享

減法器電路與原理 減法器電路圖分享

評論