靜態(tài)技術(shù)規(guī)格中,我們探討了靜態(tài)技術(shù)規(guī)格以及它們對DC的偏移、增益和線性等特性的影響。這些特性在平衡雙電阻 (R-2R) 和電阻串?dāng)?shù)模轉(zhuǎn)換器 (DAC) 的各種拓?fù)浣Y(jié)構(gòu)間是基本一致的。

2015-12-09 15:16:32 4895

4895

在使用數(shù)模轉(zhuǎn)換器 (DAC) 進(jìn)行設(shè)計時,您肯定希望輸出能夠從一個值向另一個值單調(diào)轉(zhuǎn)換,但實際電路并不總是以這種方式工作的。在某些特定代碼范圍內(nèi)出現(xiàn)過沖與下沖(即干擾脈沖)也很平常。這些脈沖會以

2018-04-10 09:04:54 9779

9779

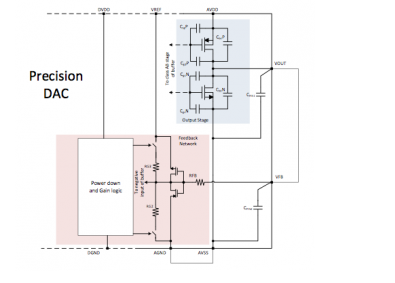

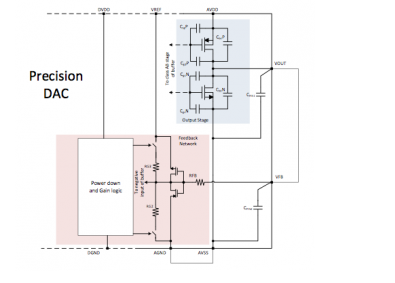

該篇將分析對象限定為一個DAC,其中的輸出緩沖器在正常模式下被加電:零量程或中量程。文章將分析一下DAC輸出在高阻抗模式中被加電的情況。同時提出一個針對加電毛刺脈沖的數(shù)學(xué)模型,隨后給出一個盡可能

2020-10-23 15:11:12 5990

5990

和AIN2.

2、DAC輸出的CE0引腳受工頻干擾(正常波形為1Vp-p 1Khz),采取如下三個方案:

a、ADUCM內(nèi)部開關(guān)N9接通,SE0短接地,此時波形只有正半波;但數(shù)值穩(wěn)定,信號被壓縮

b

2024-09-09 08:06:01

使用DAC1220作為基準(zhǔn)源,在我公司一臺高壓脈沖電源上工作,50kV電壓通過閘流管放電產(chǎn)生4us的電壓和電流脈沖,因此地線存在較大干擾。整個DAC輸出電平上都會疊加一個高頻振蕩,在加到20kV

2025-01-14 07:18:26

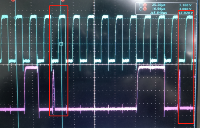

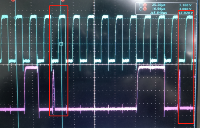

(脈沖上升沿),ALIGN1、ALIGN2信號對齊(脈沖上升沿),模擬輸出存在相差。Datasheet上對于ALIGN信號如何使用不太清楚,想實現(xiàn)兩片DAC同步輸出,是不是使用上有什么問題?

其中DAC

2024-11-20 06:24:39

DAC8568輸出電壓較低時(低于3mV),輸出引腳懸空、無負(fù)載,輸出端出現(xiàn)尖峰脈沖,如下圖所示。請問各位前輩,是否正常,怎么解決?

輸出電壓在3mV以內(nèi)變化時,尖峰脈沖的周期和幅值都在變化。

2024-12-20 12:30:43

DAC8760無故損壞電流輸出。

一批產(chǎn)品,用了400片DAC8760,在工廠生產(chǎn)老化、調(diào)試及客戶在使用的過程中(有的接了負(fù)載,有的沒有接負(fù)載),2個月內(nèi)陸陸續(xù)續(xù)出現(xiàn)10%無規(guī)律電流輸出功能損壞

2024-12-10 07:43:27

乘法 DAC 是波形發(fā)生應(yīng)用的理想構(gòu)建模塊。因為乘法數(shù)模轉(zhuǎn)換器 (DAC) 的 R-2R 架構(gòu)非常適合低噪聲、低毛刺、快速建立的應(yīng)用。從固定參考輸入電壓產(chǎn)生波形時,必須考慮一些重要的交流規(guī)格,包括建立時間、中間電平毛刺和數(shù)字 SFDR。今天我們就來分析下這些與波形發(fā)生相關(guān)的重要 DAC 規(guī)格。

2019-07-18 08:17:48

在測試AD9117時,用FPGA給DAC一個正弦波的數(shù)字信號,在輸出端發(fā)現(xiàn)有脈沖毛刺出現(xiàn),在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認(rèn)為是毛刺造成,請問是否知道關(guān)于這個毛刺生成的有關(guān)原因

2019-01-17 08:19:07

在測試AD9117時,用FPGA給DAC一個正弦波的數(shù)字信號,在輸出端發(fā)現(xiàn)有脈沖毛刺出現(xiàn),在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認(rèn)為是毛刺造成,請問是否知道關(guān)于這個毛刺生成的有關(guān)原因

2023-12-13 06:19:05

無毛刺 。 可 ADuM3200 的輸出 卻總是 存在 10nS 到20nS 的毛刺。 急求 AD 公司 技術(shù)專家 給予 解答 ,萬分感謝 。。急。。

2018-08-17 06:59:53

,采取的措施是換用低溫漂的電阻,并試圖降低阻值。

CA3140的輸出端2和6并聯(lián)輸出,干擾信號有工頻,還有高頻毛刺信號。

現(xiàn)在的問題:怎樣解決工頻紋波和高頻毛刺疊加的信號干擾

2024-09-25 07:56:56

冒險出現(xiàn)在變量發(fā)生變化的時刻,如果待信號穩(wěn)定之后加入取樣脈沖,那么就只有在取樣脈沖作用期間輸出的信號才能有效。這樣可以避免產(chǎn)生的毛刺影響輸出波形。一般說來,冒險出現(xiàn)在信號發(fā)生電平轉(zhuǎn)換的時刻,也就是說在

2023-11-02 17:22:20

所需的慣性角速率測量信息;增加數(shù)字預(yù)濾器,以濾除陀螺脈沖輸出信號中的尖峰或毛刺干擾,可以進(jìn)一步提高解調(diào)精度;為滿足實時性要求,該方法采用FPGA來實現(xiàn);實驗表明,相對整周期采樣解調(diào),此方法提高了解調(diào)精度

2018-08-30 09:21:12

的瞬間,組合邏輯的輸出常常產(chǎn)生一些小的尖峰,即毛刺信號,這是由FPGA內(nèi)部結(jié)構(gòu)特性決定的。毛刺現(xiàn)象在FPGA的設(shè)計中是不可避免的,有時任何一點毛刺就可以導(dǎo)致系統(tǒng)出錯,尤其是對尖峰脈沖或脈沖邊沿敏感

2012-09-06 14:37:54

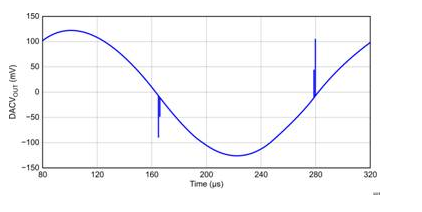

STM32的DAC上電時輸出一個幅值100mV,脈寬5ms的脈沖,影響后面電路的工作,怎么去掉這個脈沖呢?

2023-10-28 06:08:55

輸出如圖所示。

高頻是沒問題(1M-100M).但是輸入100Khz以下正弦時,輸出會有很多毛刺。輸入同頻率方波、脈沖則沒問題。

PCB如下:

求解如何解決這個問題?

額外說一句:用手觸碰330K電阻及其附近時。毛刺明顯改善。按理說人手算是一個小電容,在哪加入電容會不會改善呢?

2024-08-26 08:23:55

的C101電容的波形,發(fā)現(xiàn)它們的毛刺都一模一樣,下圖是我測的DAC8830的Vout引腳的波形:

波形測量方式:

請問為什么DAC8830輸出100mV正弦波的時候毛刺這么大?

2024-11-15 06:30:12

我是參考16位DAC的代碼配置的,會不會是我的輸出程序錯了呢?

2022-11-04 11:25:10

使用dac的dma模式輸出一定數(shù)目的脈沖波形,dac使用定時器觸發(fā),dma環(huán)形緩沖,在dma中斷中判斷已經(jīng)輸出的波形數(shù)目,達(dá)到設(shè)定數(shù)目時停止dac,使用示波器觀察波形數(shù)量與設(shè)定的不一致,請問是什么原因造成的?

2023-08-07 08:47:39

使用dac的dma模式輸出一定數(shù)目的脈沖波形,dac使用定時器觸發(fā),dma環(huán)形緩沖,在dma中斷中判斷已經(jīng)輸出的波形數(shù)目,達(dá)到設(shè)定數(shù)目時停止dac,使用示波器觀察波形數(shù)量與設(shè)定的不一致,請問是什么原因造成的?

2024-03-18 07:16:56

,但是將程序下載到電路板上發(fā)現(xiàn)輸出端的信號為:

這個圖是通過示波器直接測芯片DAC0輸出端的波形,而且該輸出端未接任何東西,2.5v電壓正常,但是會出現(xiàn)周期性的毛刺,毛刺大致值為180mV左右

2024-01-12 07:44:18

使用adc08200 100M采樣,低電壓時工作正常,但是當(dāng)有高壓脈沖干擾時,AD輸出出錯,但重新上電就工作正常

2025-01-23 08:36:33

最經(jīng)在TLC7524的DAC產(chǎn)生一個正弦波,但是輸出波形有些異常

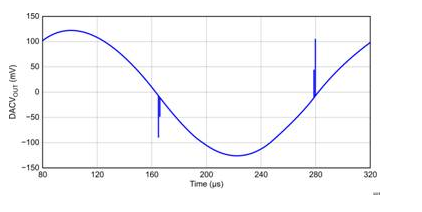

上圖圖是100hz的正弦波,在每個電平的跳變間隙都會出現(xiàn)小的毛刺;

上圖是100hz的局部放大圖,

上圖是1Khz的波形

2024-12-24 08:10:39

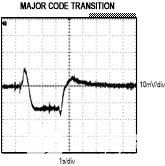

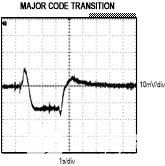

的辦法是繞過去。昨天,在我減速通過一條討厭的減速帶時,突然想到了我的那個精密型16 位R-2R DAC。它在中間刻度時存在短時脈沖波形干擾問題(請參見圖1)。我想,在選擇使用具有較大短時脈沖波形干擾特性

2019-06-20 06:23:38

我正在使用THP210做一些差分采樣的設(shè)計。

原理圖如圖所示:

在測試時發(fā)現(xiàn)輸出電壓A1_P與A1_N之間存在毛刺,如下圖所示:

通道1為數(shù)字電源的輸入電壓,通道2為差分放大器的輸出電壓

2024-07-30 06:52:36

如何解決電路中短時脈沖波形失真的所謂“毛刺”現(xiàn)象?并提出相應(yīng)的解決辦法。

2021-04-08 06:25:08

現(xiàn)在項目設(shè)計,需要用到8路輸出的DAC,每一路都可以配置成10KHZ的脈沖波輸出(0-2.5V),dac128s085是3V供電,2.5V參考電壓,請問這個DAC可以用嗎?如何計算DAC的輸出帶寬,從那些參數(shù)可以看出?如果能提供計算方法,那就更好了,謝謝!

2024-11-21 08:25:57

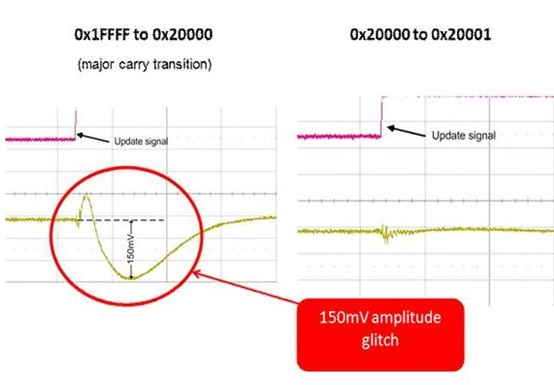

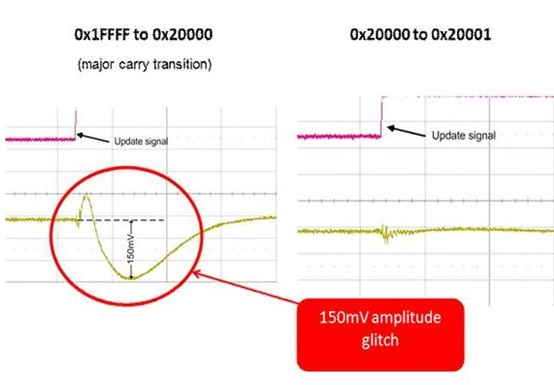

011 的 3 個 MSB。DAC 輸出進(jìn)入主要進(jìn)位轉(zhuǎn)換后,會導(dǎo)致所有 R-2R 開關(guān)短時間接地。短期開關(guān)電荷注入之后,DAC 恢復(fù),同時輸出開始趨穩(wěn)。通過比較主要進(jìn)位轉(zhuǎn)換與非主要進(jìn)位轉(zhuǎn)換的輸出干擾

2018-09-14 15:29:05

在使用數(shù)模轉(zhuǎn)換器 (DAC) 進(jìn)行設(shè)計時,您肯定希望輸出能夠從一個值向另一個值單調(diào)轉(zhuǎn)換,但實際電路并不總是以這種方式工作的。在某些特定代碼范圍內(nèi)出現(xiàn)過沖與下沖(即干擾脈沖)也很平常。這些脈沖會以

2022-11-22 06:14:59

在上一篇 DAC 基礎(chǔ)知識博文中,我們對高精度數(shù)模轉(zhuǎn)換器 (DAC) 中的輸出干擾源進(jìn)行了探討。若您希望在增加代碼的過程中獲得線性轉(zhuǎn)換,那么這些輸出脈沖可能會擾亂系統(tǒng)運行。讓我們快速回顧一下我在上

2022-11-22 06:20:07

作者:Tony Calabria德州儀器在上一篇 DAC 基礎(chǔ)知識博文中,我們對高精度數(shù)模轉(zhuǎn)換器 (DAC) 中的輸出干擾源進(jìn)行了探討。若您希望在增加代碼的過程中獲得線性轉(zhuǎn)換,那么這些輸出脈沖

2018-09-14 14:53:24

我用DAC8562輸出一個三角波測試,用示波器發(fā)現(xiàn)輸出的三角波有些毛刺,負(fù)載是XTR111,電路圖按照datasheet提供的電路設(shè)計,采用同步模式,將LDAC接地,CLR上拉,SPI通信和輸出

2025-01-23 06:21:15

問題。

競爭冒險:在組合電路中,當(dāng)邏輯門有兩個互補輸入信號同時向相反狀態(tài)變化時,輸出端可能產(chǎn)生過渡干擾脈沖的現(xiàn)象,稱為競爭冒險。

那么 FPGA 產(chǎn)生競爭冒險的原因是什么呢?

信號在

2023-05-30 17:15:28

描述DAC R-2R 架構(gòu)在噪音和精確度方面展現(xiàn)出了很高的性能,但代價是干擾區(qū)域較大。該設(shè)計專注于減少 DAC R-2R 架構(gòu)中特定于代碼的轉(zhuǎn)換所引起的主要攜帶干擾。該設(shè)計可縮小此干擾區(qū)域,從而

2018-11-07 16:40:50

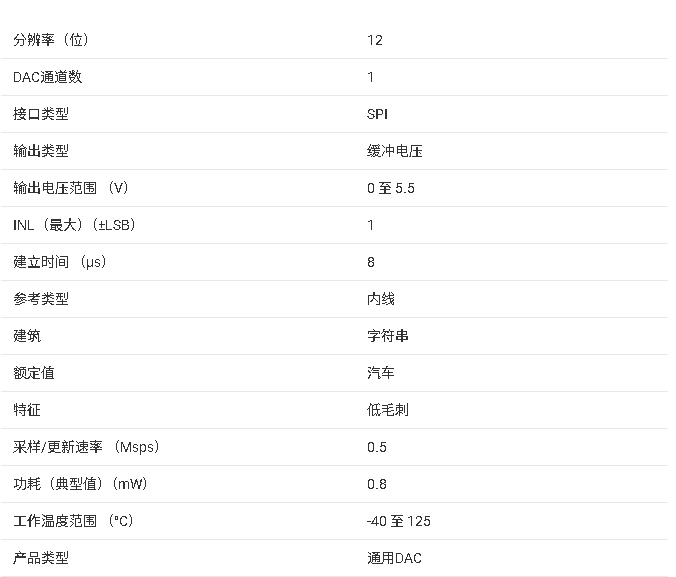

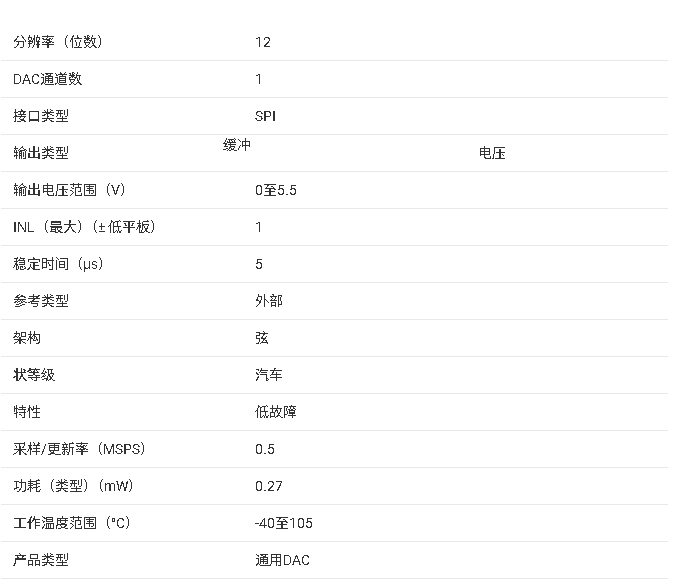

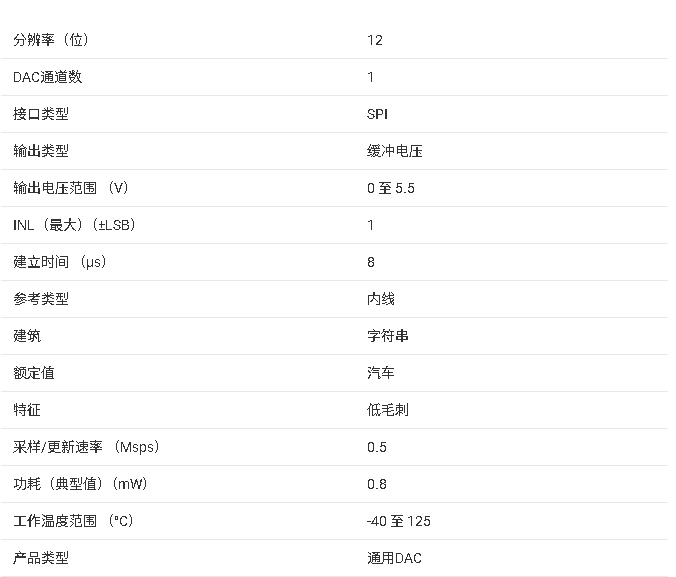

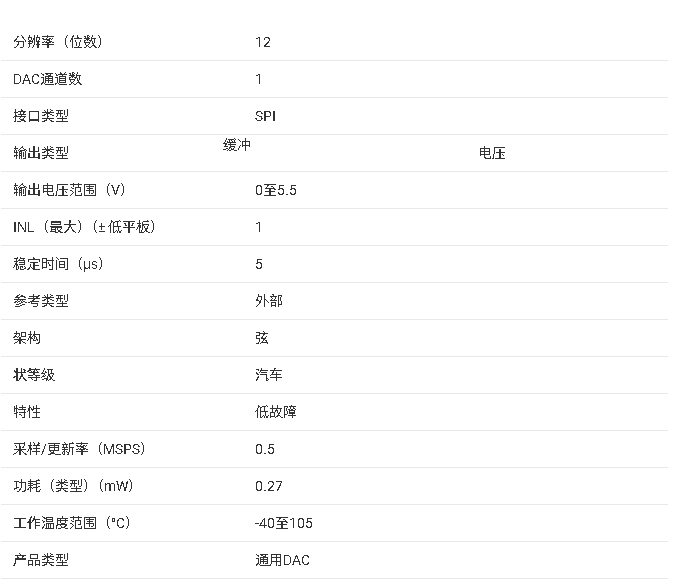

DAC6551-Q1 汽車類 12 位、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC channels (#) 1

2022-12-06 09:49:25

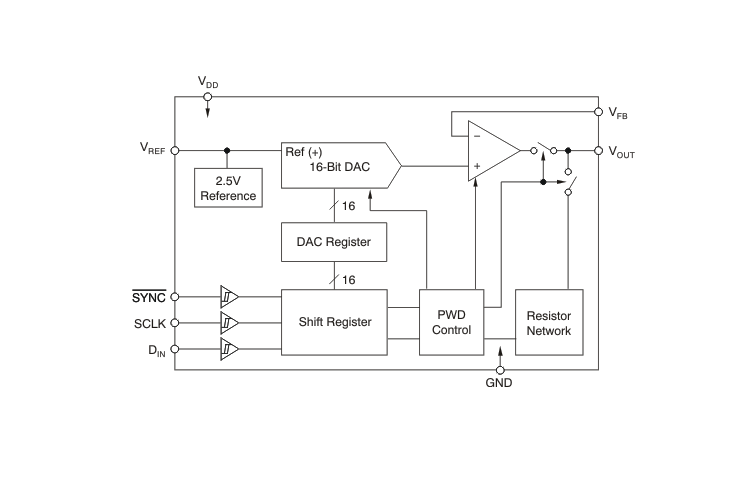

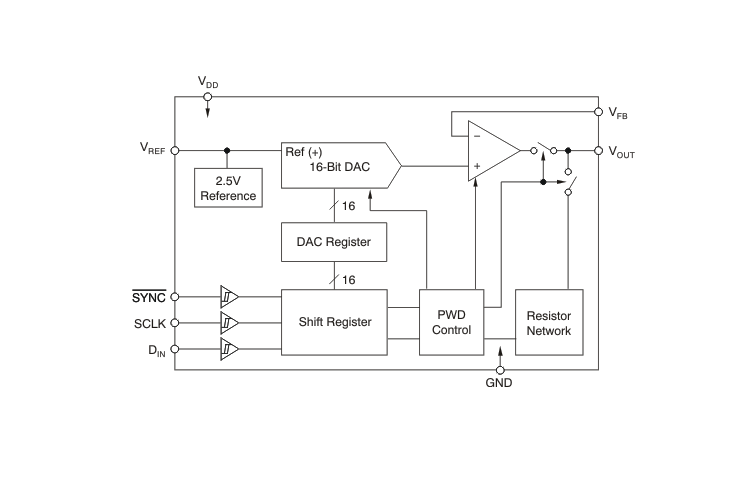

具有 2.5V、4ppm/°C 基準(zhǔn)的 16 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 16 Number of DAC

2022-12-06 09:49:56

具有 2.5V 內(nèi)部參考的 12 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 12 Number of DAC channels

2022-12-06 09:50:01

12 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 12 Number of DAC channels (#) 8

2022-12-06 09:50:02

具有 2.5V、2ppm/℃ 內(nèi)部參考的 12 位、八通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC channels

2022-12-06 09:50:11

具有 2.5V、2ppm/°C 內(nèi)部基準(zhǔn)電壓和復(fù)位功能的 12 位、四通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC

2022-12-06 09:50:17

具有 2.5V、2ppm/C 內(nèi)部基準(zhǔn)的 16 位、四通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels

2022-12-06 09:50:22

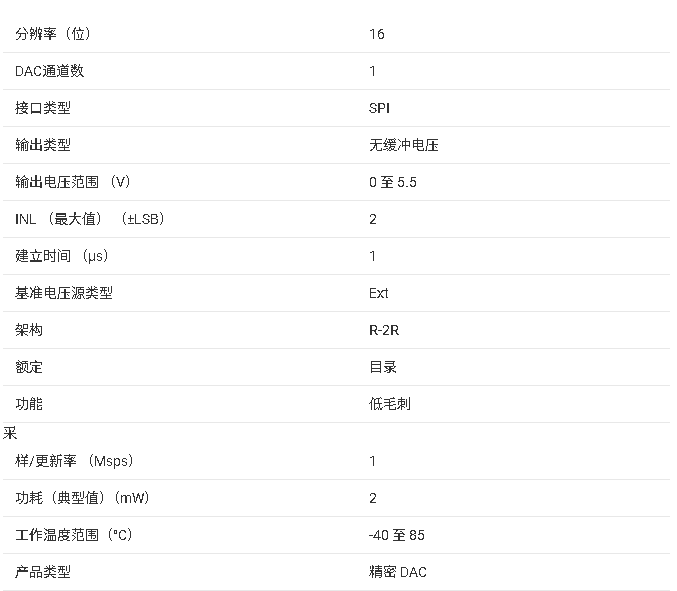

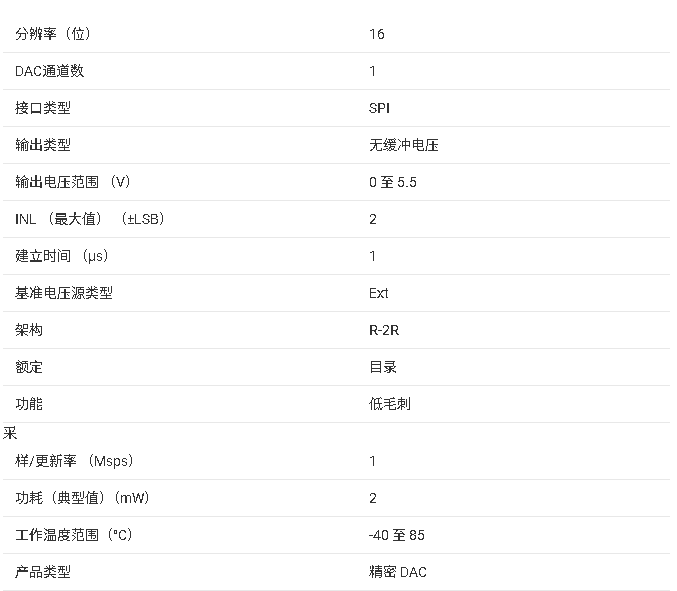

16 位超低毛刺脈沖電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels (#) 1 Interface type

2022-12-06 09:50:38

脈沖修復(fù)儀輸出波形真的是脈沖嗎?

要了解脈沖修復(fù)儀輸出的是什么波形,我們可以直截了當(dāng)?shù)膶κ忻嫔纤械?b class="flag-6" style="color: red">脈沖修復(fù)儀(器)的輸出做一個測試。

2009-11-17 10:08:53 3540

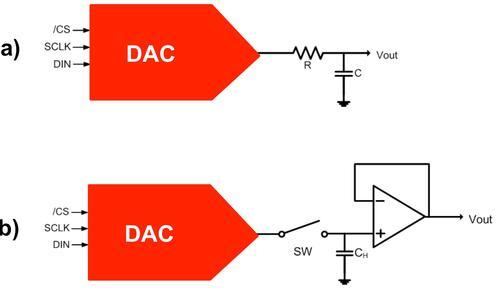

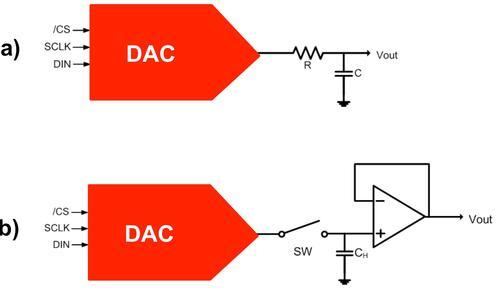

3540 最簡單的DAC去干擾方法是在DAC 放大器輸出端 (VOUT) 使用一個 R/C 濾波器。這種濾波器可以降低干擾的振幅,但增加了建立時間。

2012-01-04 14:35:42 4936

4936

噪聲干擾對線性調(diào)頻脈沖壓縮濾波器的干擾效果分析

2017-01-10 21:35:20 6

6 高重頻脈沖對脈沖多普勒雷達(dá)的干擾效應(yīng),下來看看

2016-12-26 17:18:36 5

5 機載脈沖多普勒(PD)雷達(dá)的抗干擾措施,下來看看

2016-12-26 17:20:23 16

16 脈沖多普勒雷達(dá)干擾技術(shù)研究,有需要的下來看看,

2016-12-24 23:21:48 22

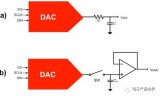

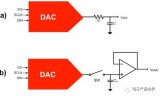

22 與下沖(即干擾脈沖)也很平常。這些脈沖會以這兩種形式中的一種出現(xiàn),如圖 1 所示。 圖 1:DAC 干擾行為 圖 1a 是一種可產(chǎn)生兩個代碼轉(zhuǎn)換誤差區(qū)的干擾,在 R-2R 高精度 DAC 中很常見。圖 1b 是單波瓣干擾脈沖,在電阻串 DAC 拓?fù)渲休^常見。干擾脈沖可通過能量測量

2017-04-18 05:28:13 667

667

在上一篇 DAC 基礎(chǔ)知識文中,我們對高精度數(shù)模轉(zhuǎn)換器 (DAC) 中的輸出干擾源進(jìn)行了探討。若您希望在增加代碼的過程中獲得線性轉(zhuǎn)換,那么這些輸出脈沖可能會擾亂系統(tǒng)運行。讓我們快速回顧一下我在上篇博文中介紹的干擾脈沖情況:

2018-07-10 14:04:00 5319

5319

(DAC) 驅(qū)動電機驅(qū)動器,以控制電機旋轉(zhuǎn)。如果毛刺脈沖幅度高于電機驅(qū)動器的靈敏度閾值,當(dāng)系統(tǒng)加電/斷電時,電機會在沒有任何方向控制的情況下旋轉(zhuǎn)。 圖1.經(jīng)簡化的輸出級和加電毛刺脈沖 之前已經(jīng)分析了高精度DAC經(jīng)緩沖輸出

2017-11-14 14:20:15 1

1 干擾方面的表現(xiàn)卻有著顯著的不同。 我們可以在DAC以工作采樣率運行時觀察到其動態(tài)不是線性。造成動態(tài)非線性的原因很多,但是影響最大的是短時毛刺脈沖干擾、轉(zhuǎn)換率/穩(wěn)定時間和采樣抖動。 用戶可以在DAC以穩(wěn)定采樣率在其輸出范圍內(nèi)運行時觀察短時毛刺脈沖干擾

2017-11-29 14:59:02 2403

2403

針對欺騙干擾信號常在時域、頻域和空域與真實信號重疊,導(dǎo)致識別欺騙干擾難度較大的問題,本文假定真實發(fā)射機與欺騙干擾機射頻前端器件除數(shù)模轉(zhuǎn)換器(DAC)外均工作于理想狀態(tài),提出了一種基于DAC建模的欺騙

2017-12-26 19:02:00 0

0 最簡單的 DAC 去干擾方法是在 DAC 放大器輸出端 (VOUT) 使用一個 R/C 濾波器(圖 2 底部)。這種濾波器可以降低干擾的振幅,但增加了建立時間。

2018-03-13 16:29:00 3201

3201

DAC8930和DAC8931是單、16位、串行輸入、電壓輸出的數(shù)模轉(zhuǎn)換器(DAC),由單個3-V T0 5V電源供電。這些轉(zhuǎn)換器提供了良好的線性度、低毛刺、低噪聲、以及在指定溫度范圍--151C T01251 C上的快速穩(wěn)定。

2018-05-16 08:58:15 3

3 DAC101S101-Q1 – 10 位微功耗、RRO 數(shù)模轉(zhuǎn)換器DAC7551-Q1 – 汽車類 12 位超低毛刺脈沖電壓輸出數(shù)模轉(zhuǎn)換器DAC7551-Q1 器件是一款單通道電壓輸出數(shù)模轉(zhuǎn)換器(DAC),它具有優(yōu)異的線性和單調(diào)性,并且采用一種專有架構(gòu) 可以最大限度減小毛刺脈沖能量。

2020-03-15 20:12:00 1426

1426

的辦法是繞過去。昨天,在我減速通過一條討厭的減速帶時,突然想到了我的那個精密型16 位R-2R DAC。它在中間刻度時存在短時脈沖波形干擾問題(請參見圖1)。我想,在選擇使用具有較大短時脈沖波形干擾特性的DAC 時,可以在DAC 輸出端

2020-07-31 18:52:00 1

1 電子發(fā)燒友網(wǎng)為你提供DAC的短時毛刺脈沖干擾資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-13 08:44:06 11

11 電壓輸出DAC

2021-04-17 09:10:35 9

9 LTC1591/LTC1597:帶4象限電阻器的14位并行低毛刺乘法DAC數(shù)據(jù)表

2021-04-18 20:58:22 0

0 LTC1599:帶4象限電阻器的16位字節(jié)寬、低毛刺乘法DAC數(shù)據(jù)表

2021-05-20 09:38:24 2

2 測試線纜在課本中通常被認(rèn)為是理想導(dǎo)體,但現(xiàn)實中如果忽略線纜的影響,往往會得到錯誤的測試結(jié)果。比如變頻器輸出電壓上的毛刺信號,可能就是線纜帶來的。 工程師在變頻器電機測試中偶然會發(fā)現(xiàn)電壓的PWM波形上

2021-10-28 16:14:44 3023

3023 輸出脈沖可能會擾亂系統(tǒng)運行。讓我們快速回顧一下我在上篇博文中介紹的干擾脈沖情況:

DAC 輸出干擾的“能量”由脈沖(以綠色顯示)的寬度和高度定義。可根據(jù)系統(tǒng)要求對干擾的形狀進(jìn)行很好的控制。在

2021-11-10 09:43:00 2268

2268

當(dāng)DAC輸出模擬值發(fā)生變化時,在DAC輸出端觀察到動態(tài)現(xiàn)象,表現(xiàn)為毛刺,如圖1所示。該毛刺能量定義為電壓曲線下的面積與示波器上捕獲的時間圖的關(guān)系。該毛刺能量的單位是nV × s。

2022-12-15 11:53:04 4859

4859

在電源電壓超過±5V的R-2R DAC設(shè)計中,DAC的主要進(jìn)位轉(zhuǎn)換期間可能會出現(xiàn)較大的電壓毛刺(高達(dá)1.5V)。這些毛刺會傳播到輸出緩沖放大器,并出現(xiàn)在輸出端。控制頂部 (VREF+) 和底部 (VREF-) 單刀雙擲開關(guān)(S0 至 SN)的電平轉(zhuǎn)換器的回轉(zhuǎn)會導(dǎo)致毛刺(圖 1)。

2023-02-24 17:10:06 4813

4813

什么是毛刺?毛刺的大小和方向 如何測量毛刺的尺寸?如何檢查已去除的毛刺? 毛刺是指由于加工工藝或其他原因產(chǎn)生的金屬表面上的不平整區(qū)域或小尖刺。毛刺通常形成于金屬的切削或沖壓過程中,可能會影響產(chǎn)品

2023-12-07 14:24:36 8635

8635 如何最小化毛刺尺寸?如何控制毛刺方向? 為了得到高質(zhì)量的產(chǎn)品或工藝品,我們通常需要把毛刺的尺寸最小化,并控制其方向。毛刺會影響制品的外觀質(zhì)量、功能性能以及使用壽命。本文將介紹毛刺的形成原因、影響因素

2023-12-07 14:24:39 1683

1683 脈沖干擾的產(chǎn)生 脈沖干擾的解決方法? 脈沖干擾的產(chǎn)生 脈沖干擾是指在電路或系統(tǒng)中,因突然的電流或電壓變化而引起的暫時性干擾。這種干擾一般會導(dǎo)致電子設(shè)備的誤操作、數(shù)據(jù)丟失、系統(tǒng)崩潰等問題,嚴(yán)重的甚至

2024-01-05 14:31:34 6374

6374 在I2C的波形中,經(jīng)常會發(fā)現(xiàn)有這樣的脈沖毛刺,會被認(rèn)為是干擾或者器件不正常。

2024-03-02 09:33:54 4809

4809

電子發(fā)燒友網(wǎng)站提供《DAC7568、DAC8168、DAC8568 8通道、超低毛刺、電壓輸出數(shù)模轉(zhuǎn)換器數(shù)據(jù)表.pdf》資料免費下載

2024-06-20 15:40:48 0

0 電子發(fā)燒友網(wǎng)站提供《DAC82002 16位、低毛刺脈沖、雙通道電壓輸出、非緩沖DAC數(shù)據(jù)表.pdf》資料免費下載

2024-07-15 10:07:59 0

0 電子發(fā)燒友網(wǎng)站提供《DAC82001 16位、低毛刺脈沖、單通道電壓輸出、非緩沖DAC數(shù)據(jù)表.pdf》資料免費下載

2024-07-15 10:09:02 2

2 電子發(fā)燒友網(wǎng)站提供《DAC8551-Q1汽車類16位、超低毛刺脈沖、電壓輸出DAC數(shù)據(jù)表.pdf》資料免費下載

2024-07-16 11:47:30 0

0 電子發(fā)燒友網(wǎng)站提供《DAC7551-Q1 12位、超低毛刺脈沖、電壓輸出數(shù)模轉(zhuǎn)換器數(shù)據(jù)表.pdf》資料免費下載

2024-07-19 11:39:36 0

0 芯片的DAC(數(shù)模轉(zhuǎn)換器)輸出端(如DACL腳)出現(xiàn)時,其根源往往直指兩大關(guān)鍵環(huán)節(jié):電源純凈度與信號通路完整性。一、DAC底噪:并非“天生”,實乃“環(huán)境干擾”語音芯

2025-06-13 09:07:14 1154

1154

在數(shù)字音頻播放系統(tǒng)中,音頻毛刺和信號丟失無疑是最令人困擾的問題之一。當(dāng)一個設(shè)備丟失一個采樣點時,這意味著什么?這意味著一個采樣點被跳過,從那一刻起,整個波形在時間上向左平移了一個采樣瞬間。如果播放

2025-10-20 09:02:23 397

397

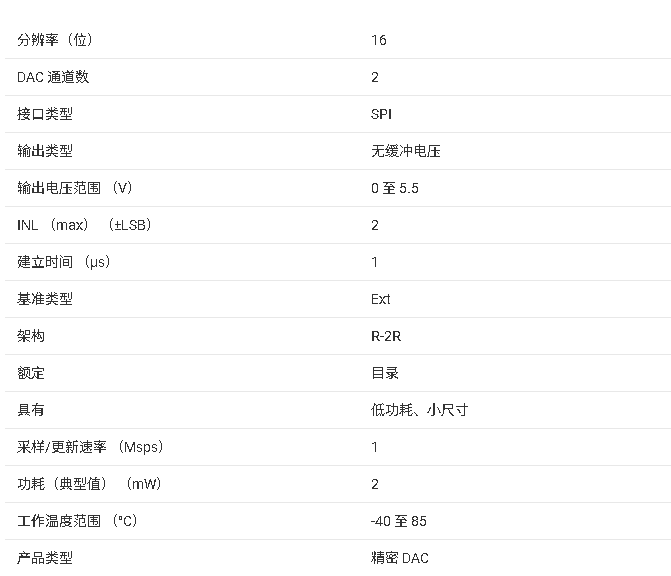

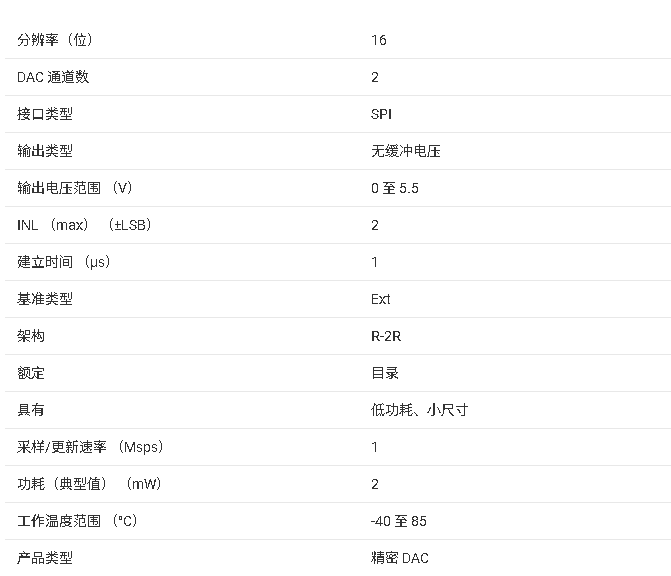

16位DAC82001是一款高精度、低功耗、單通道數(shù)模轉(zhuǎn)換器(DAC),具有無緩沖電壓輸出。

該DAC82001采用3.3V和5V電源,提供1LSB DNL和2LSB INL的線性度。高精度

2025-10-29 15:08:17 438

438

16位DAC82002是一款高精度、低功耗、雙通道數(shù)模轉(zhuǎn)換器(DAC),具有無緩沖電壓輸出。

該DAC82002采用3.3 V和5 V電源,提供1LSB DNL和2LSB INL的線性度

2025-10-29 15:15:18 516

516

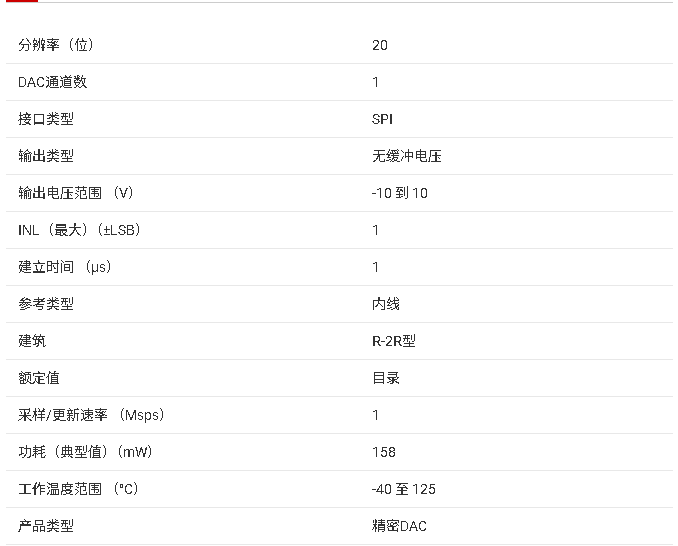

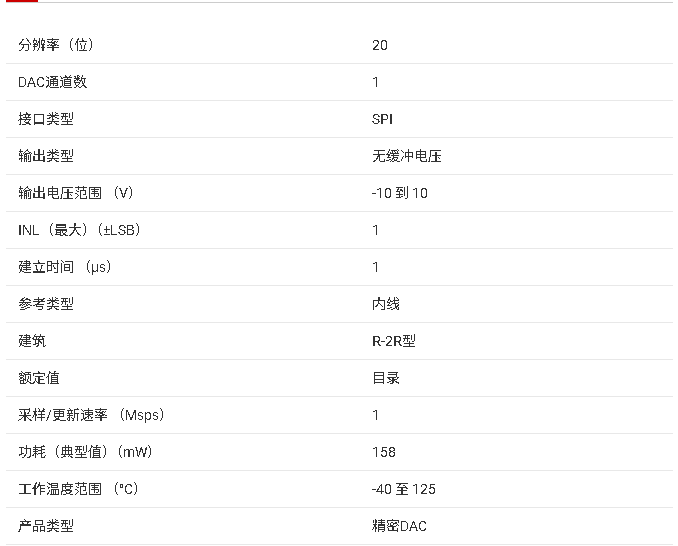

20位DAC11001B是一款高精度、低噪聲、電壓輸出、單通道、數(shù)模轉(zhuǎn)換器(DAC)。該DAC11001B設(shè)計為單調(diào),并在所有輸出范圍內(nèi)提供出色的線性度。

無緩沖電壓輸出提供低噪聲性能 (7

2025-10-31 09:47:27 435

435

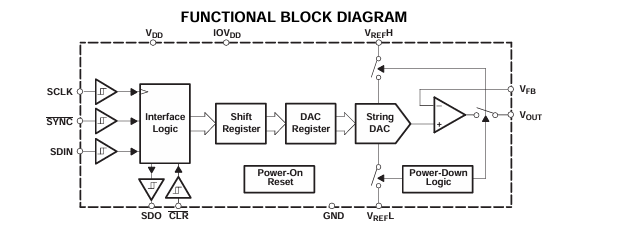

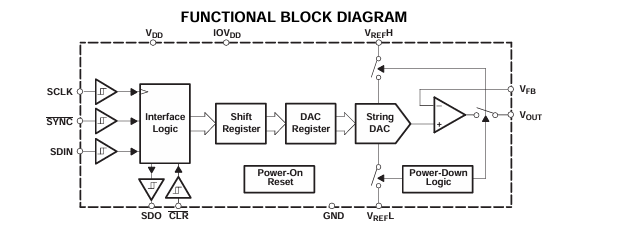

DAC8551-Q1 和 DAC6551-Q1 是小型、低功耗、電壓輸出、16 位和 12 位 符合汽車應(yīng)用標(biāo)準(zhǔn)的數(shù)模轉(zhuǎn)換器 (DAC)。DACx551-Q1 器件 提供良好的線性度,并最大

2025-11-10 09:43:31 425

425

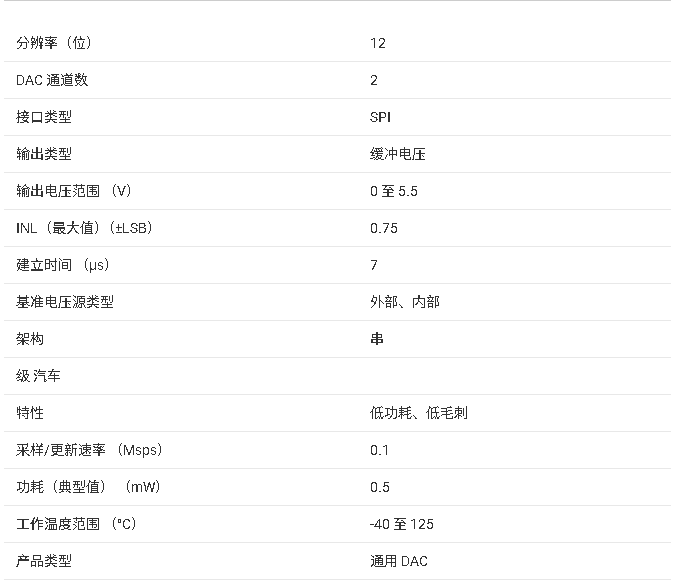

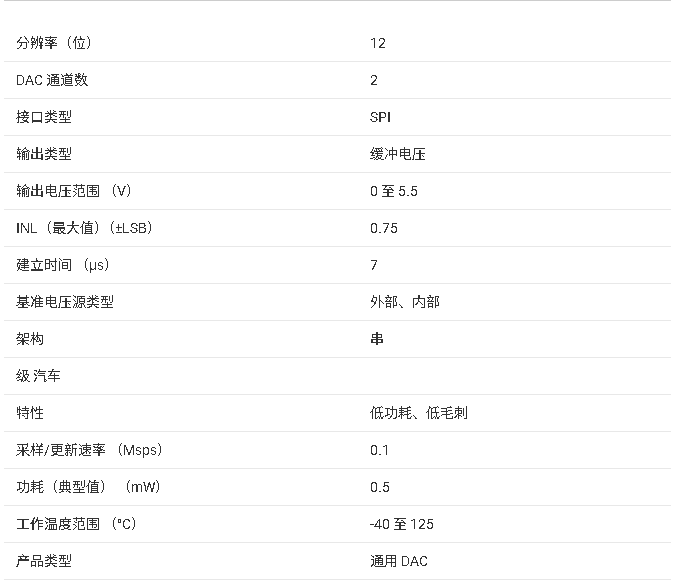

DAC756x-Q1、DAC816x-Q1 和 DAC856x-Q1 (DACxx6x-Q1) 器件具有低功耗、 電壓輸出、雙通道、12位、14位和16位數(shù)模轉(zhuǎn)換器(DAC), 分別。這些器件包括一

2025-11-12 09:29:10 478

478

DAC7551-Q1 設(shè)備是一種單通道、電壓輸出的數(shù)模轉(zhuǎn)換器 (DAC)具有卓越的線性和單調(diào)性,以及一種最小化的專有架構(gòu) 故障能量。低功耗DAC7551-Q1器件由單一2.7至5.5伏電源供電。這

2025-11-19 10:42:46 440

440

? 在電子設(shè)計領(lǐng)域,數(shù)模轉(zhuǎn)換器(DAC)是連接數(shù)字世界和模擬世界的關(guān)鍵橋梁。今天,我們將深入探討TI公司的DAC8560,這是一款16位、超低毛刺、電壓輸出的數(shù)模轉(zhuǎn)換器,具有諸多出色的特性,適用于

2025-11-28 13:44:34 380

380

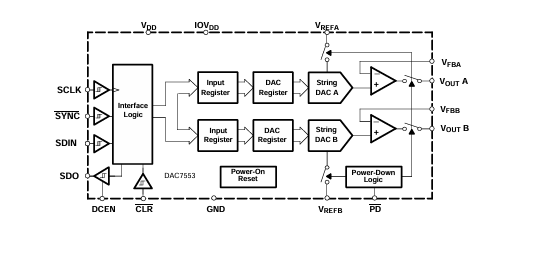

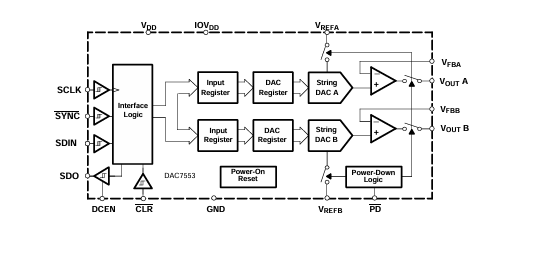

? 在電子設(shè)計領(lǐng)域,數(shù)模轉(zhuǎn)換器(DAC)是連接數(shù)字世界與模擬世界的關(guān)鍵橋梁。今天我們要深入探討的是德州儀器(TI)的DAC7553,一款具有卓越性能的12位雙路超低毛刺電壓輸出數(shù)模轉(zhuǎn)換器。 文件下載

2025-11-30 10:10:56 376

376

、電壓輸出的數(shù)模轉(zhuǎn)換器,具有眾多出色的特性和廣泛的應(yīng)用場景。 文件下載: dac7551.pdf 1. 關(guān)鍵特性解析 高精度與低毛刺 相對精度 :DAC7551的相對精度(INL)達(dá)到±0.35LSB,這意味著它能夠提供非常精確的模擬輸出,減少了轉(zhuǎn)換誤差,保證了信號的準(zhǔn)確性。 超低毛刺能量 :僅為0.

2025-11-30 10:33:45 465

465

電子發(fā)燒友App

電子發(fā)燒友App

評論