16位DAC82001是一款高精度、低功耗、單通道數模轉換器(DAC),具有無緩沖電壓輸出。

該DAC82001采用3.3V和5V電源,提供1LSB DNL和2LSB INL的線性度。高精度與微型封裝相結合,使該器件成為增益和失調校準、電壓設定點生成和電源控制等應用的絕佳選擇。該DAC82001集成了上電復位 (POR) 電路。POR電路確保DAC輸出根據RSTSEL引腳的狀態以零刻度或中量程上電,并保持該刻度,直到將有效代碼寫入器件。RESET引腳拉低后,所有內部寄存器均異步復位。

*附件:dac82001.pdf

該DAC82001使用多功能三線串行外設接口 (SPI),工作時鐘速率高達 50 MHz。

特性

- 16 位性能:1-LSB DNL 和 2-LSB INL

- 低毛刺能量:0.5 nV-s

- 快速建立:1 μs

- 寬電源:2.7 V 至 5.5 V

- 寬基準電壓源范圍:2.0 V 至 V

DD - 低功耗:5.0 V 時為 250 μA

- 高達 50 MHz 的 3 線串行外設接口 (SPI)

- 重置為零比例或中比例

- 1.62伏伏

IH的帶 VDD= 5.5 伏 - 溫度范圍:–40°C 至 +85°C

- 封裝:微型 10 引腳 WSON

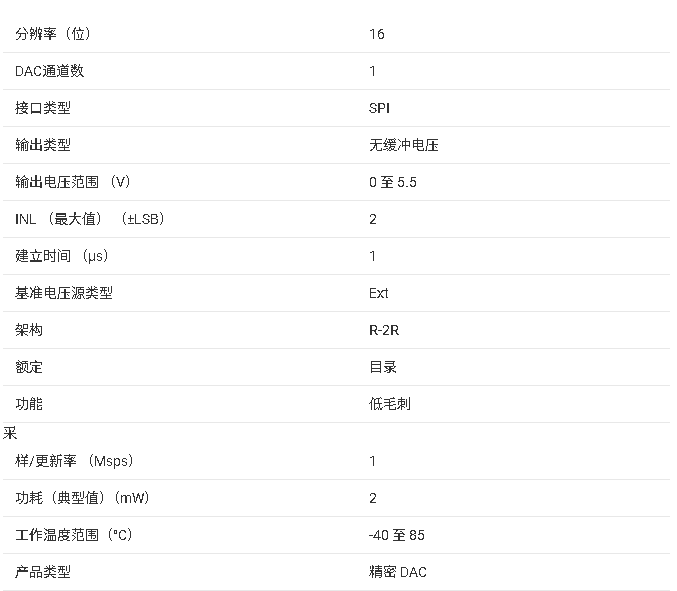

參數

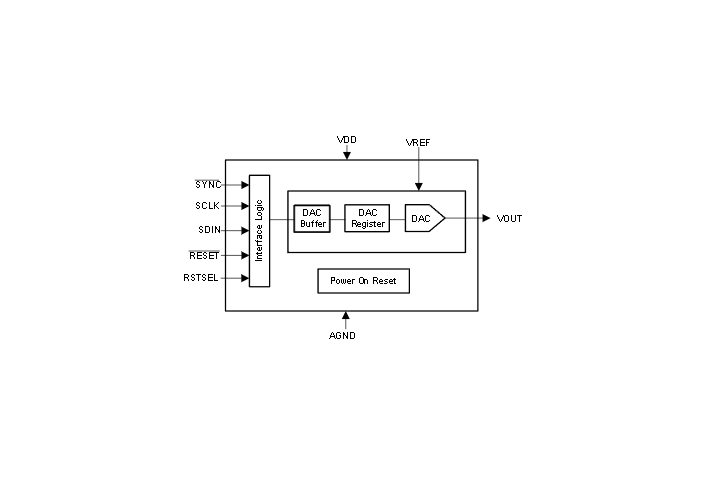

方框圖

一、產品核心定位與基礎參數

DAC82001 以 “高線性度 + 低毛刺 + 小封裝” 為核心優勢,通過分段 R-2R 架構與優化電源管理,平衡精度與系統適配性,適配 2.7V~5.5V 寬供電場景。

1. 核心基礎參數總覽

| 類別 | 關鍵指標 | 說明 |

|---|---|---|

| 核心規格 | 分辨率 / 通道數 / 輸出類型 | 16 位,單通道,無緩沖電壓輸出(需外部運放緩沖時需額外配置) |

| 供電與功耗 | 供電范圍 / 靜態電流 | 2.7V~5.5V 單電源;5V 時靜態電流 250μA(典型值),功耗低至 1.25mW |

| 封裝與溫域 | 封裝類型 / 尺寸 / 工作溫度 | 10 引腳 WSON(2.5mm×2.5mm),超小尺寸適配高密度布局;-40℃~+85℃寬溫 |

| 參考電壓 | 輸入范圍 / 阻抗 | 2.0V~VDD(與供電電壓匹配),輸入阻抗 5kΩ,輸入電容 75pF |

| 數字接口 | 接口類型 / 最高速率 | 3 線 SPI(SYNC/SCLK/SDIN),最高 50MHz 時鐘,24 位移位寄存器幀格式 |

二、核心性能參數

1. 靜態性能(TA=-40+85℃,VDD=2.7V5.5V)

(1)線性度與精度

- 積分非線性(INL) :±2 LSB(最大值),典型值 ±0.6 LSB,保障全量程輸出線性;

- 微分非線性(DNL) :±1 LSB(最大值),典型值 ±0.5 LSB,無失碼,避免輸出臺階失真;

- 總未調整誤差(TUE) :±0.06% FSR(最大值),典型值 0.04% FSR,減少系統級校準需求;

- 零碼 / 增益誤差 :零碼誤差 ±2.6 LSB,溫度系數 ±0.02 ppm/℃;增益誤差 ±20 LSB,溫度系數 ±0.1 ppm/℃,全溫域精度穩定性高。

(2)輸出特性

- 輸出范圍 :0

VREF(與參考電壓匹配,如 VREF=5V 時輸出 05V),輸出阻抗 6.25 kΩ(典型值); - 電源抑制比(PSRR) :DC 模式 5 μV/V(典型值),AC 模式 - 72 dB(10kHz 時),減少供電噪聲對輸出的影響;

- 輸出噪聲 :0.1Hz~10Hz 低頻噪聲 0.1 μVPP(典型值),10kHz 噪聲密度 10 nV/√Hz,保障微弱信號輸出純凈度。

2. 動態性能(關鍵指標決定瞬態輸出質量)

DAC82001 的動態性能在測試測量、波形生成場景中至關重要,核心指標如下:

| 動態特性 | 關鍵指標 | 說明 |

|---|---|---|

| 建立時間 | 至 1/2 LSB 精度(CL=10pF) | 1 μs(典型值),快速響應數字碼值變化,適配高頻波形生成(如 200 kSPS 更新率) |

| 毛刺能量 | ±1 LSB 跳變(大進位附近) | 0.5 nV?s(典型值),大幅減少碼值切換時的輸出擾動,適配精密電壓設定 |

| 無雜散動態范圍(SFDR) | 1kHz 正弦波輸出(40kHz 低通濾波) | -96 dB(典型值),含 7 次諧波以內雜散,波形失真小 |

| 總諧波失真(THD) | 1kHz 正弦波輸出(40kHz 低通濾波) | -91 dB(典型值),保障模擬輸出波形純度,適配超聲掃描等信號生成場景 |

| 上電 / 掉電毛刺 | 負載 CL=10pF | 上電毛刺幅度 0.8V(典型值),掉電無明顯過沖,避免系統上電沖擊 |

3. 復位與初始化功能

器件支持硬件復位與 上電復位(POR) ,靈活適配系統啟動與故障恢復場景:

| 復位模式 | 觸發方式 / 輸出狀態 | 關鍵特性 |

|---|---|---|

| 上電復位(POR) | VDD 低于 0.7V 并維持 1ms 以上觸發,無需外部信號 | 輸出狀態由 RSTSEL 引腳決定:RSTSEL 接 AGND 時輸出 0 刻度(0V),接 VDD 時輸出中刻度(VREF/2) |

| 硬件復位 | RESET 引腳拉低(低電平有效),異步觸發 | 復位后所有內部寄存器初始化,輸出狀態同 POR;復位引腳需先拉高再進行 SPI 通信,需等待 250μs 穩定時間 |

| 軟件復位 | 向 TRIGGER 寄存器(0x5h)寫入 0x1010 指令 | 等效 POR 效果,無需硬件引腳操作,適配軟件控制場景(如遠程系統校準) |

三、關鍵功能模塊詳解

1. DAC 架構與傳輸函數

器件采用 分段 R-2R 架構 ,兼顧精度與動態性能,核心架構與數據處理流程如下:

(1)架構設計

- 分段結構 :16 位數據分為 “4 位 MSB+12 位 LSB”,MSB 解碼為 15 路匹配電阻開關(E1

E15),LSB 驅動 12 位 R-2R 梯形網絡(S0S11),減少電阻失配導致的線性誤差; - 傳輸函數 :輸出電壓由數字碼值與參考電壓共同決定,公式為:VOUT ? =216**?1DAC**_DATA ? ×VREF?

其中,DAC_DATA 為 065535 的 16 位二進制碼值(直二進制格式),VREF 為外部參考電壓(2.0VVDD)。

(2)寄存器與輸出更新模式

器件內置 4 個核心寄存器,支持異步更新與 同步更新 ,適配不同時序需求:

| 寄存器名稱 | 地址 / 功能 | 關鍵配置 |

|---|---|---|

| NOOP 寄存器 | 0x0h | 空操作指令,寫入后無寄存器變化,用于 SPI 通信測試 |

| SYNC 寄存器 | 0x2h | 配置輸出更新模式:DAC_SYNC_EN=0(默認,異步更新,寫緩沖后立即更新輸出);DAC_SYNC_EN=1(同步更新,需 LDAC 觸發) |

| TRIGGER 寄存器 | 0x5h | 含 LDAC 觸發位(同步更新時觸發輸出)與軟件復位位(0x1010 指令觸發 POR) |

| DAC 寄存器 | 0x8h | 16 位數據寄存器,復位時默認 0x0000(RSTSEL=AGND)或 0x8000(RSTSEL=VDD) |

2. 數字接口與通信協議

3 線 SPI 接口是器件與控制器(如 MCU/FPGA)的核心交互通道,需嚴格遵循時序要求以保障數據傳輸正確性:

(1)SPI 幀格式與時序

- 幀結構 :24 位數據幀(Bit23

Bit0),Bit23 為寫使能位(固定為 0,僅支持寫操作),Bit22Bit16 為寄存器地址,Bit15~Bit0 為 16 位 DAC 數據(MSB 對齊); - 關鍵時序參數 :SCLK 高電平時間≥9ns、低電平時間≥9ns;SDIN 建立時間≥5ns、保持時間≥10ns;SYNC 拉低到 SCLK 下降沿 setup 時間≥13ns,確保數據穩定鎖存;

- 中斷處理 :若 SYNC 在 24 個 SCLK 下降沿前拉高,視為無效寫操作,移位寄存器復位,避免錯誤數據寫入。

(2)接口防護與配置

- 數字輸入引腳(SYNC/SCLK/SDIN)支持 1.62V 高電平(VDD=5.5V 時),輸入電流 ±5μA,引腳電容 10pF,兼容 3.3V/5V 邏輯電平;

- 建議在 SYNC/SCLK 引腳配置下拉電阻(如 10kΩ),避免懸空時噪聲干擾;SDIN 引腳需確保數據在 SCLK 下降沿穩定輸入。

四、典型應用場景與設計建議

1. 核心應用場景

DAC82001 的核心價值在于 “高線性度 + 低毛刺”,典型應用包括:

- 任意波形發生器(AWG) :1μs 建立時間 + 96dB SFDR,支持 200kSPS 更新率,適配測試測量設備的正弦波、三角波生成;

- 雙極性模擬輸出 :通過外部運放(如 OPA210)將 0~VREF 單極性輸出轉換為 ±10V 雙極性,適配 PLC 模擬輸出模塊;

- 精密電壓設定 :0.06% FSR 總未調整誤差,用于半導體測試中的精準偏置電壓生成,或電池測試的充放電電壓控制;

- 超聲掃描儀時間增益補償(TGC) :低噪聲與高線性度,保障超聲信號放大過程中的增益校準精度。

典型應用電路示例(雙極性輸出)

- 電路結構 :DAC82001 輸出(0~2.5V)經 OPA210 運放構成差分放大電路,配合 8.25kΩ/33.2kΩ 電阻網絡,將單極性信號轉換為 ±10V 雙極性輸出;

- 關鍵器件 :參考電壓采用 REF5025(2.5V 低噪聲基準,漂移 ±5ppm/℃),運放供電 ±15V 避免輸出鉗位,VREF 引腳并聯 100pF 電容抑制高頻噪聲;

- 性能指標 :輸出噪聲 < 3nV/√Hz(100Hz~1MHz),壓擺率 2.5V/μs,滿足快速電壓切換需求。

2. 關鍵設計建議

(1)電源與參考電壓設計

- 電源濾波 :VDD 引腳就近并聯 0.1μF 陶瓷電容(X7R/NP0 dielectric)+1μF 鉭電容,抑制高頻噪聲;若使用開關電源,需在電源入口增加 LC 濾波(如 10μH 電感 + 10μF 電容);

- 參考電壓配置 :VREF 需小于 VDD,建議使用低噪聲基準(如 REF50xx 系列),并在 VREF 引腳并聯 100nF+47pF 電容(前者抑制低頻噪聲,后者優化動態響應)。

(2)PCB 布局與輸出緩沖

- 布局分區 :模擬區(VOUT/VREF/AGND)與數字區(SYNC/SCLK/SDIN)嚴格分離,AGND 與數字地單點連接,避免串擾;VOUT 引腳布線短而直,減少寄生電容(建議 < 10pF);

- 輸出緩沖 :因器件無內置輸出緩沖,VOUT 阻抗較高(6.25kΩ),需外部運放緩沖時,優先選擇低噪聲、高帶寬型號(如 OPA328,適合 AWG 場景;OPA210,適合雙極性輸出場景),運放輸入失調電壓需 < 10μV 以避免精度損失。

(3)復位與校準設計

- 復位配置 :RSTSEL 引腳根據需求接 AGND(上電零刻度)或 VDD(上電中刻度),建議通過 0Ω 電阻跳帽可配置,適配不同系統初始化需求;

- 系統校準 :若需更高精度,可在系統上電后通過軟件寫入校準碼值(如測量 VOUT 實際值后調整 DAC_DATA),或利用外部 ADC 監測輸出并閉環校準。

-

dac

+關注

關注

44文章

2713瀏覽量

197080 -

數模轉換器

+關注

關注

14文章

1296瀏覽量

85748 -

電壓輸出

+關注

關注

0文章

153瀏覽量

26185 -

POR電路

+關注

關注

0文章

3瀏覽量

5619

發布評論請先 登錄

AD5758:單通道16位電流和電壓輸出DAC,支持動態電源控制和HART連接數據表

UG-1268:評估采用動態電源控制和HART連接的AD5758單通道16位電流和電壓輸出DAC

UG-442:評估AD5422單通道、16位、電流源和電壓輸出DAC、HART連接

UG-1554:使用HART連接評估AD5423單通道16位電流或電壓輸出DAC

DAC7571低功耗、單通道、12位緩沖電壓輸出DAC數據表

DAC5571低功耗、單通道、8位緩沖電壓輸出DAC數據表

DAC82001 16 位低毛刺單通道電壓輸出 DAC 技術文檔總結

DAC82001 16 位低毛刺單通道電壓輸出 DAC 技術文檔總結

評論