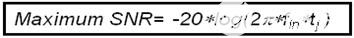

本文介紹了如何準(zhǔn)確地估算采樣時鐘抖動,以及如何計算正確的上下整合邊界。

2012-04-01 10:19:38 2333

2333

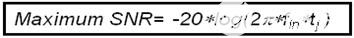

本文即第2部分中,這種組合抖動將用于計算ADC的信噪比 (SNR),之后將其與實(shí)際測量情況進(jìn)行比較。

2012-05-07 11:31:22 2027

2027

為了正確理解時鐘相關(guān)器件的抖動指標(biāo)規(guī)格,同時選擇抖動性能適合系統(tǒng)應(yīng)用的時鐘解決方案,本文詳細(xì)介紹了如何理解兩種類型時鐘驅(qū)動器的抖動參數(shù),以及從鎖相環(huán)輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 19925

19925

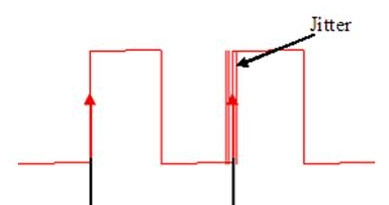

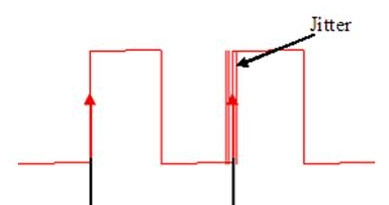

抖動一般定義為信號在某特定時刻相對于其理想位置的短期偏移。這個短期偏移在時域的表現(xiàn)形式為抖動(下文的抖動專指時域抖動),在頻域的表現(xiàn)形式為相噪。本文主要探討下時鐘抖動和相噪以及其測量方法,以及兩者之間的關(guān)系。

2016-01-18 10:54:11 31583

31583

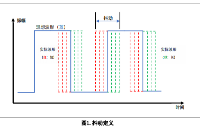

時鐘抖動是相對于理想時鐘沿實(shí)際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 3278

3278

頻域和時域分析是分析信號的基本方法,是從不同的角度來描述信號的特性。信號的特性可以在時域上和頻率域上得到反映。

2024-01-03 10:16:47 9043

9043

/Cadence,指導(dǎo)預(yù)加重/去加重參數(shù)調(diào)整。

時鐘分配網(wǎng)絡(luò)優(yōu)化

問題:時鐘抖動(Jitter)過大(如RMS抖動>2ps),導(dǎo)致ADC采樣誤差。

TDNA方案:通過眼圖分析提取時鐘信號的確定性抖動

2025-04-28 14:49:21

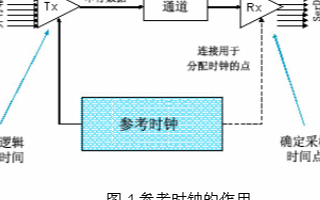

圖1強(qiáng)調(diào)了噪聲源而不是固有抖動會引起定時抖動錯誤。更快的邊沿速率減少了時鐘信號上的電壓噪聲對時鐘抖動性能的影響。這種現(xiàn)象并非是僅屬于時鐘信號的特點(diǎn)。在接收時鐘信號或測量抖動性能的設(shè)備內(nèi),這種機(jī)理也表現(xiàn)得很明顯。…

2022-11-23 07:59:49

轉(zhuǎn)時鐘抖動的理解

2016-10-05 12:08:25

什么是抖動?時鐘抖動有哪幾種測量方法?時域測量方法和頻域測量方法的原理分別是什么?TIE抖動和相噪抖動之間的關(guān)系是什么?

2021-05-08 06:32:56

求時域頻域分析

2012-05-04 13:21:46

了解VNA時域分析

2019-09-16 10:55:31

量大幅降低到百fs(飛秒)級別,囿于實(shí)時示波器的固有抖動及本底噪聲等指標(biāo)采用傳統(tǒng)的時域抖動分析和測試已經(jīng)顯得捉衿見肘,頻域的角度漸漸成為業(yè)界前沿討論的方向然而對于數(shù)字信號測試基于傳統(tǒng)的頻域設(shè)備如頻譜分析

2020-03-09 13:52:45

表示。抖動分為確定性和隨機(jī)性抖動。確定性抖動是可識別的干擾信號造成的,這種抖動的幅度有限。總抖動的構(gòu)成如下:在時域中,噪聲是非周期的函數(shù)。而傅里葉分析可以把此函數(shù)分解成多個正弦周期的函數(shù),如下。相位噪聲

2020-06-10 17:38:08

一般考量采樣時鐘抖動對ADC ENOB的影響都是用相位噪聲的隨機(jī)抖動Rj計算,想請教周期性抖動例如電源上的抖動造成時鐘的Dj對 ENOB有影響嗎?如何計算這部分的影響?

2024-11-13 08:15:51

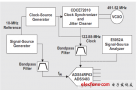

本文針對全方位的信號路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術(shù)。研究選用雙級聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實(shí)現(xiàn)了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

采樣時鐘抖動對ADC信噪比的性能有什么影響?如何實(shí)現(xiàn)低抖動采樣時鐘電路的設(shè)計?

2021-04-14 06:49:20

。這工作正常,直到我決定董事會所做的測量不夠準(zhǔn)確(在時間軸上)。因此,我將生成的時鐘使能信號(2MHz)輸出到IO-Pin,并使用示波器測量頻率抖動。抖動似乎具有高斯分布,標(biāo)準(zhǔn)偏差約為28ns。我還測量

2020-08-19 06:09:57

我們這里有一個E4411B,我們想測量典型CMOS邏輯電平ADC時鐘的抖動。當(dāng)然,頻譜分析儀有75歐姆的N型射頻連接器。好像我需要一個適配器,它將采用典型的示波器探頭并將其與分析儀的輸入配對。這樣

2019-01-30 07:29:56

達(dá)到所需的系統(tǒng)抖動性能,一定要保持盡可能低的時鐘抖動,并在整個分配網(wǎng)絡(luò)上分配低抖動時鐘源。隨著系統(tǒng)要求的不斷提升,問題也隨之而來:時鐘線路上添加的簡單緩沖器會不會讓時鐘抖動變得更差?如果會,在添加簡單

2018-09-13 14:38:43

抖動。

抖動是對信號時域變化的測量結(jié)果,它從本質(zhì)上描述了信號周期距離其理想值偏離了多少。在絕大多數(shù)文獻(xiàn)和規(guī)范中,時間抖動(jitter)被定義為高速串行信號邊沿到來時刻與理想時刻的偏差,所

2023-06-02 17:53:10

一塊音視頻處理芯片輸出1080i的數(shù)據(jù)Data及其同步時鐘Clk,但是時鐘clk的抖動很大,我該如何處理呢?另外,抖動很大的時鐘源能否在后面接入一個模擬鎖相環(huán)降低時鐘的抖動呢?

2018-11-12 09:12:43

時鐘抖動或結(jié)束時鐘抖動的最佳方法是什么?

2021-03-17 07:04:07

的收發(fā)器時,由于該器件不提供與數(shù)據(jù)同時傳輸?shù)娜?b class="flag-6" style="color: red">時鐘,因此必須產(chǎn)生一個10GHz的時鐘信號。抖動分析儀用時鐘信號同步輸入數(shù)據(jù),所以時鐘上的任何相位噪聲都將影響抖動測試結(jié)果。當(dāng)然,如果選用頻譜分析儀的話

2014-12-09 14:36:58

閉環(huán)系統(tǒng)的時域分析

2013-04-10 21:22:58

什么是頻譜分析儀?頻譜儀一般是一種非時域工具,主要描述信號在頻域上的變化(用于信號失真度、調(diào)制度、譜純度、頻率穩(wěn)定度和交調(diào)失真等信號參數(shù)的測量),在時域上使用得并不廣泛,那么有誰知道具體有哪些方面的應(yīng)用嗎?

2019-08-09 06:31:03

頻譜儀一般是一種非時域工具,主要描述信號在頻域上的變化(用于信號失真度、調(diào)制度、譜純度、頻率穩(wěn)定度和交調(diào)失真等信號參數(shù)的測量),在時域上使用得并不廣泛。不過,RIGOL DSA1000系列頻譜儀提供

2019-08-07 07:37:32

高階系統(tǒng)的時域分析

2013-04-10 20:58:01

隨著數(shù)據(jù)速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數(shù)據(jù)鏈路中,時鐘抖動會影響發(fā)射機(jī)、傳輸線和接收機(jī)的數(shù)據(jù)抖動。保證時鐘質(zhì)量的測量也在不斷發(fā)展

2008-12-27 12:24:05 6

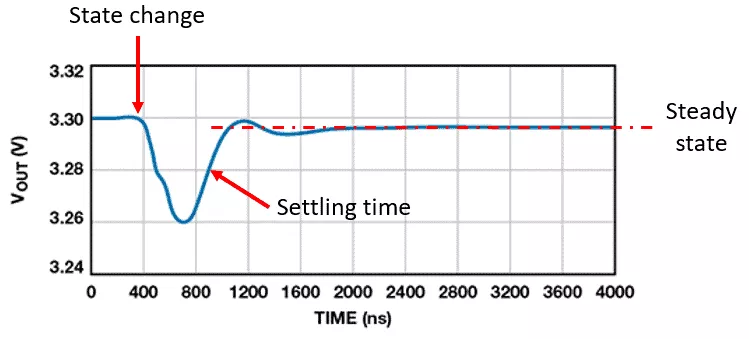

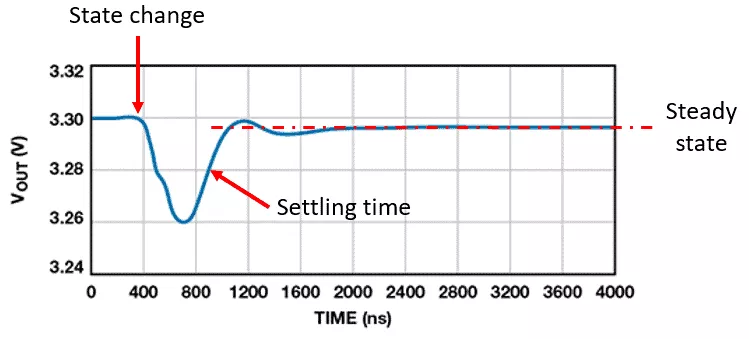

6 時域分析法:3-1 控制系統(tǒng)的時域指標(biāo)控制系統(tǒng)的時域性能指標(biāo),是根據(jù)系統(tǒng)在單位階躍函數(shù)作用下的時間響應(yīng)——單位階躍響應(yīng)確定的,通常以h(t)表示。

2009-05-26 15:29:17 0

0 隨著數(shù)據(jù)速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數(shù)據(jù)鏈路中,時鐘抖動會影響發(fā)射機(jī)、傳輸線和接收機(jī)的數(shù)據(jù)抖動。保證時鐘質(zhì)量的測量也在不斷發(fā)展。目前

2009-07-07 14:01:21 20

20 連續(xù)時間系統(tǒng)的時域分析:一、引言1.經(jīng)典時域分析法經(jīng)典時域分析法¡ 求解微分方程。線性時不變連續(xù)時間系統(tǒng)用n 階線性常系數(shù)微分方程來描述式中,r(t)為響應(yīng)函

2009-10-04 09:21:02 0

0 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設(shè)計。

2009-11-27 11:24:07 15

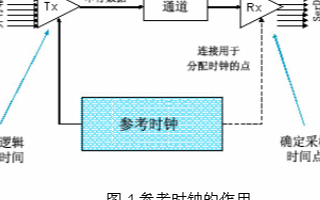

15 高速互聯(lián)鏈路中參考時鐘的抖動分析與測量

在高速互聯(lián)鏈路中,發(fā)送器的參考工作時鐘的抖動是影響整個

2010-04-15 14:01:39 19

19 什么是時域分析?

指控制系統(tǒng)在一定的輸入下,根據(jù)輸出量的時域表達(dá)式,分析系統(tǒng)的穩(wěn)定

2009-01-08 14:01:07 5336

5336

該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)期。關(guān)

2009-04-21 23:14:05 1036

1036

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-22 09:35:13 410

410

摘要:這是一篇關(guān)于時鐘(CLK)信號質(zhì)量的應(yīng)用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加抖動。本文還描述了周期抖動和相位噪聲譜之間的關(guān)系,并介紹

2009-04-22 10:16:50 4761

4761

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-25 09:54:26 638

638

摘要:該應(yīng)用筆記提出了超低抖動時鐘合成器的一種設(shè)計思路,其目標(biāo)是產(chǎn)生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動指標(biāo),設(shè)計難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-05-08 10:19:03 566

566

控制系統(tǒng)的時域分析法--控制系統(tǒng)的時域分析法

2009-07-27 14:20:35 1535

1535 理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點(diǎn)研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 2094

2094

時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 時域頻域分析及MATLAB軟件的應(yīng)用

有需要的朋友下來看看

2015-12-23 10:32:46 4

4 介紹 此應(yīng)用筆記側(cè)重于不同類型的時鐘抖動。時鐘抖動是從它的時鐘邊沿偏差理想的位置。了解時鐘抖動非常重要在應(yīng)用中,因?yàn)樗鹬P(guān)鍵作用,在時間預(yù)算一個系統(tǒng)。 隨著系統(tǒng)數(shù)據(jù)速率的增加,定時抖動成為關(guān)鍵

2017-04-01 16:13:18 6

6 很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現(xiàn)象,其不僅可導(dǎo)致噪聲增加,而且還會降低數(shù)據(jù)轉(zhuǎn)換器的有效位數(shù) (ENOB)。例如,如果系統(tǒng)需要 100MHz 14(最小值)位的 ENOB,我們

2017-04-08 04:51:23 1767

1767

了解高速ADC時鐘抖動的影響將高速信號數(shù)字化到高分辨率要求仔細(xì)選擇一個時鐘,不會妥協(xié)模數(shù)轉(zhuǎn)換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數(shù)轉(zhuǎn)換器的性能

2017-05-15 15:20:59 13

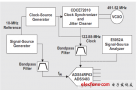

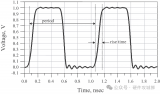

13 級,從而降低成本和功耗。在欠采樣接收機(jī)設(shè)計中必須要特別注意采樣時鐘,因?yàn)樵谝恍└咻斎腩l率下時鐘抖動會成為限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重點(diǎn)介紹如何準(zhǔn)確地估算某個時鐘源的抖動,以及如何將其與AD

2017-05-18 09:47:38 1

1 時鐘抖動時域分析,第 2 部分

2017-10-26 16:10:42 6

6 時鐘抖動時域分析 第 3 部分

2017-10-26 16:13:28 4

4 時間域中分析的時鐘抖動,第 1 部分

2017-10-26 16:16:23 4

4 時鐘產(chǎn)生抖動(jitter)會使發(fā)生抖動的時鐘信號與未發(fā)生抖動的時鐘信號在時域上存在偏差,從而使模數(shù)轉(zhuǎn)換器的采樣頻率發(fā)生紊亂,最終導(dǎo)致模數(shù)轉(zhuǎn)換器采樣的不穩(wěn)定性,使輸出信號存在頻譜毛刺,導(dǎo)致誤碼率上升

2017-11-11 18:22:26 9

9 時鐘接口閾值區(qū)間附近的抖動會破壞ADC的時序。例如,抖動會導(dǎo)致確定性抖動由干擾引起,會通過某些方式使閾值發(fā)生偏移,通常受器件本身特性限制。查看時鐘信號噪聲通常有三種途徑:時域、頻域、相位域。

2018-03-12 13:39:33 24428

24428 仔細(xì)觀察某個采樣點(diǎn),可以看到計時不準(zhǔn)(時鐘抖動或時鐘相位噪聲)是如何形成振幅變化的。由于高 Nyquist 區(qū)域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采樣帶來輸入頻率的增加,固定數(shù)量的時鐘抖動自理想采樣點(diǎn)產(chǎn)生更大數(shù)量的振幅偏差(噪聲)。

2018-05-14 08:51:40 3

3 本文詳細(xì)介紹了TI的6篇應(yīng)用手冊的概述包括:時鐘抖動時域分析,△∑ADC工作原理,用太陽能電池板為升壓拓?fù)浣Y(jié)構(gòu)電池充電器供電,隔離式RS-485收發(fā)器可支持DMX512舞臺照明和特效應(yīng)用,具有數(shù)字隔離器的工業(yè)數(shù)據(jù)采集接口,單電源系統(tǒng)中單端視頻至差分視頻的轉(zhuǎn)換

2018-05-30 10:08:28 20

20 ADI研討會:高性能時鐘: 解密抖動

2019-08-20 06:05:00 2532

2532 時鐘設(shè)計人員通常會提供一個相位噪聲,但不提供抖動規(guī)格。相位噪聲規(guī)格可以轉(zhuǎn)換為抖動,首先確定時鐘噪聲,然后通過小角度計算將噪聲與主時鐘噪聲成分進(jìn)行比較。相位噪聲功率通過計算圖9中的灰色區(qū)域積分得出。

2019-08-20 11:06:53 9314

9314

時鐘抖動性能主題似乎是時鐘,ADC和電源的當(dāng)前焦點(diǎn)供應(yīng)廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內(nèi)的數(shù)字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關(guān)系需要一些努力。

2019-09-14 11:24:00 9399

9399

一、抖動 抖動分析功能主要應(yīng)用于高速串行信號的完整性分析,分析測量方差隨時間的變化情況。 1、為什么要測抖動? 抖動會帶來誤碼,干擾時鐘恢復(fù)、降低系統(tǒng)性能...... 2、測試抖動之前要注意

2020-07-23 15:24:36 2526

2526 本文針對全方位的信號路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術(shù)。研究選用雙級聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實(shí)現(xiàn)了降噪和時鐘抖動濾除的作用。

2020-09-23 10:45:00 2

2 發(fā)射機(jī)必須用適當(dāng)?shù)囊驍?shù)乘以參考時鐘獲得數(shù)據(jù)速率,才能確定邏輯變換定時。例如,對于100 MHz參考時鐘和5 Gb/s輸出信號,發(fā)射機(jī)將用PLL給參考時鐘乘以因數(shù)50。PLL乘法器不僅放大時鐘抖動,還

2020-08-05 08:57:09 7881

7881

MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

7 電子發(fā)燒友網(wǎng)為你提供相位噪聲處理:時鐘抖動或結(jié)束時鐘抖動的最佳方法是什么?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:49:06 26

26 前言 :本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數(shù)對ADC采樣的影響,主要介紹以下內(nèi)容: 時鐘抖動的構(gòu)成 時鐘抖動對ADC SNR的影響 如何計算時鐘抖動 如何優(yōu)化時鐘抖動 1.采樣理論

2021-04-07 16:43:45 10607

10607

超低抖動時鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 ADC時鐘接口中的最小抖動

2021-05-09 12:19:40 6

6 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 PCIe 和網(wǎng)絡(luò)時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數(shù)字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持?jǐn)U頻,而網(wǎng)絡(luò)時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴(kuò)頻的時鐘。

2022-05-05 15:50:44 7109

7109

時鐘采樣系統(tǒng)最大限度減少抖動

2022-11-04 09:52:12 0

0 時鐘抖動使隨機(jī)抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規(guī)范基礎(chǔ)知識

2022-11-07 08:07:30 2

2 對于頻率成分相對較低的輸入信號,例如在1MHz以下,時鐘抖動變得不那么重要,但是當(dāng)輸入信號的頻率為幾百兆赫茲時,時鐘上的抖動將成為誤差的主要來源,并且將成為SNR的限制因素。

2023-01-03 14:35:04 2164

2164

針對啟動抖動會嚴(yán)重影響整車NVH性能的問題,研究了某SUV混動車型啟動工況下的整車抖動問題,確定了啟動抖動產(chǎn)生的根本原因。通過制定一系列的試驗(yàn)方案進(jìn)行對比分析,并結(jié)合LMS測試數(shù)據(jù)進(jìn)行時域分析,明確導(dǎo)致整車啟動抖動的根本原因是啟動電機(jī)拖動發(fā)動機(jī)過程中扭矩波動導(dǎo)致。

2023-01-29 10:35:40 3874

3874 1.1.1.??抖動定義和分類 ITU-T G.701對抖動的定義為:“抖動是指數(shù)字信號在短期內(nèi)相對于理想位置發(fā)生的偏移重大影響的短時變化”。 對于真實(shí)物理世界中的時鐘源,比如晶振、DLL、PLL,它們的時鐘輸出周期都不可能是一個單點(diǎn)的固定值,而是隨時間而變化的

2023-03-10 14:54:32 1847

1847

系統(tǒng)時序設(shè)計中對時鐘信號的要求是非常嚴(yán)格的,因?yàn)槲覀兯械臅r序計算都是以恒定的時鐘信號為基準(zhǔn)。但實(shí)際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 5281

5281 ) 以及其他通常要求時域抖動規(guī)范(如周期)的應(yīng)用生成時鐘- 周期和周期抖動。 然而,對于串行解串器 (SerDes)、千兆以太網(wǎng) (GbE)、10 GbE、同步光網(wǎng)絡(luò)/同步數(shù)字體系 (SONET/SDH) 和光纖通道等高速接口,情況就不同了。有嚴(yán)格的頻域抖動要求。 為了正常運(yùn)行,這些高速接口依賴于低頻

2023-05-26 22:15:02 3574

3574 首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 3288

3288

先來聊一聊什么是時鐘抖動。時鐘抖動實(shí)際上是相比于理想時鐘的時鐘邊沿位置,實(shí)際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實(shí)際上,時鐘源例如PLL是無法產(chǎn)生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 3109

3109

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 3231

3231

時域分析的步驟,以便更好地理解時域分析的過程。時域分析是一種通過分析信號在時間域上的變化規(guī)律來研究系統(tǒng)特性的方法。

2023-09-28 15:43:58 3092

3092

相位噪聲和抖動是對時鐘頻譜純度的兩種表述形式,一個是頻域一個是時域,從原理上來說,它們是等效的。

2023-10-30 16:02:46 4314

4314

詳解時域瞬態(tài)分析技術(shù)

2023-12-07 14:45:01 1577

1577

電子發(fā)燒友網(wǎng)站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費(fèi)下載

2023-11-28 10:24:10 1

1 什么是頻域分析?頻域和時域有什么關(guān)系? 頻域分析是一種用于分析信號的方法,它將信號從時域(時鐘)轉(zhuǎn)換為頻域(頻率)。頻域分析允許我們觀察信號中包含的不同頻率成分,并確定它們的振幅、相位和其它特性

2024-02-03 17:19:00 5852

5852 談到頻域和時域關(guān)系,我們先從信號的基本分析方法講起。傳統(tǒng)上對無線、有線通訊信號的分析方法從三個域上劃分:時域、頻域和調(diào)制域。調(diào)制域是分析信號頻率(或相位)隨時間的變化。

2024-04-28 15:09:47 3251

3251

隨著數(shù)據(jù)傳輸速率的不斷提升,時鐘信號的抖動分析變得越來越重要。在Gb/s范圍,任何一個小的抖動都會對系統(tǒng)性能造成顯著影響。

2024-05-15 16:09:34 2487

2487 時鐘抖動(Clock Jitter)是時鐘信號領(lǐng)域中的一個重要概念,它指的是時鐘信號時間與理想事件時間的偏差。這種偏差不僅影響數(shù)字電路的時序性能,還可能對系統(tǒng)的穩(wěn)定性和可靠性造成不利影響。以下是對時鐘抖動工作原理的詳細(xì)闡述,內(nèi)容將圍繞其定義、類型、產(chǎn)生原因、影響及應(yīng)對措施等方面展開。

2024-08-19 17:58:11 5343

5343 在FPGA(現(xiàn)場可編程門陣列)設(shè)計中,消除時鐘抖動是一個關(guān)鍵任務(wù),因?yàn)?b class="flag-6" style="color: red">時鐘抖動會直接影響系統(tǒng)的時序性能、穩(wěn)定性和可靠性。以下將詳細(xì)闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設(shè)計到軟件優(yōu)化的各個方面。

2024-08-19 17:58:54 3753

3753 時鐘抖動和相位噪聲是數(shù)字系統(tǒng)和通信系統(tǒng)中兩個至關(guān)重要的概念,它們之間存在著緊密而復(fù)雜的關(guān)系。以下是對時鐘抖動和相位噪聲關(guān)系的詳細(xì)探討,旨在全面解析兩者之間的相互作用和影響。

2024-08-19 18:01:57 2380

2380 時鐘抖動(Jitter)和時鐘偏移(Skew)是數(shù)字電路設(shè)計中兩個重要的概念,它們對電路的時序性能和穩(wěn)定性有著顯著的影響。下面將從定義、原因、影響以及應(yīng)對策略等方面詳細(xì)闡述時鐘抖動和時鐘偏移的區(qū)別。

2024-08-19 18:11:30 3230

3230 電子發(fā)燒友網(wǎng)站提供《低噪聲振蕩器的時域抖動測量注意事項(xiàng).pdf》資料免費(fèi)下載

2024-09-23 11:33:05 0

0 引言:時鐘抖動(jitter)是現(xiàn)代通信和數(shù)字系統(tǒng)中至關(guān)重要的性能指標(biāo)之一,對數(shù)據(jù)傳輸速率和系統(tǒng)同步起著關(guān)鍵作用。本文將深入探討時鐘抖動的定義、不同類型,詳細(xì)介紹各種抖動類型的測試方法,并分析時鐘

2024-10-21 16:15:04 2420

2420

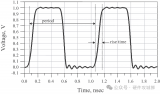

一般來說,我們會從時域和頻域兩個角度,分別對信號進(jìn)行分析。 時域 時域是真實(shí)世界存在的域,按時間順序呈現(xiàn)。例如,在某個時鐘信號的時域圖中,可以觀察到兩個重要的參數(shù),波形的周期和上升沿: 時鐘周期即

2024-11-19 10:18:30 5275

5275

通過上一期我們了解到:數(shù)字電子產(chǎn)品中電源軌噪聲和時鐘抖動是有關(guān)聯(lián)的,以及測量電源軌噪聲的方案,接下來我們基于實(shí)際測量,揭示電源軌噪聲對系統(tǒng)時鐘抖動的影響。

2024-11-22 16:11:22 1176

1176

電子發(fā)燒友App

電子發(fā)燒友App

評論