本文介時鐘頻率概念及其對系統(tǒng)性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2012-03-10 09:55:23 5225

5225

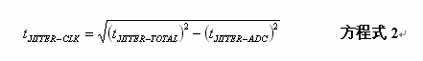

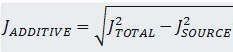

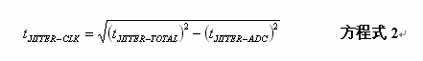

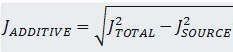

本系列文章共有三部分,第 1 部分重點介紹如何準確地估算某個時鐘源的抖動,以及如何將其與 ADC 的孔徑抖動組合。在第 2 部分中,該組合 抖動 將用于計算 ADC 的 SRN,然后將其與實際

2012-05-07 11:37:30 3382

3382

性能和集成的頻率裕量設定能力。IDT 高性能振蕩器的超低相位抖動和可修改的輸出頻率顯著降低萬兆以太網(wǎng) (10GbE) 交換器、路由器和其他相關網(wǎng)絡設備的誤碼率 (BER)。

2013-03-27 13:40:33 1547

1547 為了正確理解時鐘相關器件的抖動指標規(guī)格,同時選擇抖動性能適合系統(tǒng)應用的時鐘解決方案,本文詳細介紹了如何理解兩種類型時鐘驅(qū)動器的抖動參數(shù),以及從鎖相環(huán)輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 19925

19925

Silicon Labs(亦稱“芯科科技”,NASDAQ:SLAB)日前推出了一系列高性能I2C可編程晶體振蕩器(XO),具有最佳的抖動性能和頻率靈活性。憑借低至95fs的典型抖動性能,Si544

2017-12-13 09:32:48 8919

8919 設計使用 UCC28700-Q1 反激式控制器對輸出進行恒定電壓和恒定電流控制。變頻工作模式可最大限度減少空載時的待機功耗。此設計的特性包括通過準諧振谷底開關實現(xiàn)最高效率和頻率抖動,從而提高 EMI 性能。 特性 初級側(cè)調(diào)節(jié)恒定電壓和恒定電流工作模式空載功耗低于 10mW頻率抖動一路隔離式輸出和一路接地參考式輸出

2022-09-23 07:52:00

采用16 位、250 MSPS 數(shù)模轉(zhuǎn)換器AD9467 和低抖動時 鐘發(fā)生器 AD9523-1。第一部分說明了軟件評估,其中模擬了ADC 性能隨頻率的變化情況并展示了如何在軟件中連接各器件。第二 部分

2019-10-23 08:00:00

John Johnson 德州儀器 在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t

2018-09-19 11:47:50

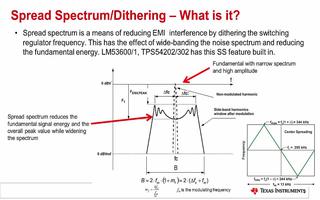

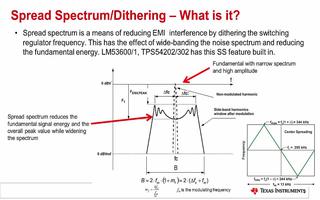

頻率抖動改善EMI原理 開關電源采用脈寬調(diào)制(PWM)控制方式,開關頻率不斷提高,其高頻開關波形含有大量諧波成分,通過傳輸線和空間電磁場向外傳播,造成傳導和輻射干擾。頻率抖動技術(Frequency

2013-02-01 15:30:40

ICE3A2065ELJ離線式SMPS電流模式控制器的典型應用電路,集成650V CoolMOS和啟動單元(鎖存和頻率抖動模式)。 CoolSETF3 ELJ版本是針對系統(tǒng)噪音的增強型LJ版本。它

2019-06-13 13:46:19

`下圖是半橋LLC的半橋中點的波形,發(fā)覺頻率在不停的抖動,是怎么回事?可從哪些方面下手解決?`

2019-02-20 10:29:44

LM331做壓頻轉(zhuǎn)換,輸出頻率9KHZ,輸出頻率抖動,抖動范圍大約在2%.什么原因?

2024-12-06 07:32:38

STM32的ADC項目應用,大家都用什么算法濾波和穩(wěn)定數(shù)據(jù)抖動。

ADC數(shù)據(jù)的抖動有時候應用在項目上讓人很是頭疼,什么度娘十大濾波算法也是要斟酌選用。

單片機項目設計中,外設ADC的使用總是少不了的,這也就涉及了相關的算法來處理數(shù)據(jù),ADC的學習一下各位的經(jīng)驗。

2024-04-17 08:20:15

我用IN199A1進行電流檢測,采樣電阻1歐,IN199A1的電壓直接送進單片機的ADC口進行檢測,但我用示波器觀察送進單片機的電壓有嚴重抖動,抖動頻率大概30-40khz,于是我把R3電阻拆掉,用

2024-08-09 06:02:40

DN1013- 了解時鐘抖動對高速ADC的影響

2019-07-17 06:41:39

信號路徑設計是如何影響輸出信號的抖動性能的?為了解決這一問題,有哪些不同的設計方法?

2021-04-12 06:24:23

時鐘頻率的不斷提高使相位噪聲和抖動在系統(tǒng)時序上占據(jù)日益重要的位置。本文介其概念及其對系統(tǒng)性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2019-06-05 07:13:30

。均方根時鐘抖動可能會限制性能最佳的ADC的信噪比,在更高的輸入頻率下加劇。雖然這不會改變ADC的NSD電位,但會在具有高抖動時鐘的系統(tǒng)中限制其實際SNR性能。由于ADC的模擬輸入頻率使用相同的rms

2018-11-01 11:33:13

基于Labview和Matlab的圖像法抖動測量程序。能夠?qū)崿F(xiàn)對高速相機的圖進行抖動分析。具體程序見附件中。需要labview2012及其以上版本才能打開運行。

2015-05-13 21:31:10

0.3 A 電流。UCC28700 擁有頻率抖動特性,以減少 EMI。主要特色解決方案尺寸很小頻率抖動以提高 EMI1 層電路板高輸入電壓過壓和過流保護

2018-08-27 09:45:53

)。為了實現(xiàn)高性能,需要無抖動時鐘。為什么不應使用像ADuM14x系列這樣的標準隔離器?標準隔離器會增加時鐘抖動,從而限制ADC的性能。

圖7顯示了不同頻率、不同類型時鐘抖動下SNR的理論極限。像

2025-05-29 10:37:33

采樣時鐘抖動對ADC信噪比的性能有什么影響?如何實現(xiàn)低抖動采樣時鐘電路的設計?

2021-04-14 06:49:20

有這些應用,但在模數(shù)轉(zhuǎn)換系統(tǒng)中我們需要噪聲來提高電路性能。這種信號處理技術,稱為抖動,故意將具有適當 PDF(概率密度函數(shù))和 PSD(功率譜密度)的噪聲信號添加到 ADC(模數(shù)轉(zhuǎn)換器)輸入(采樣和量化

2022-12-22 15:17:41

實現(xiàn)頻率抖動的原理是啥?

2015-10-12 08:58:50

頻率,其連續(xù)諧波的能量會越來越低。采用頻率抖動技術(Frequency Jitter)的著眼點在于分散諧波干擾能量,我們使得開關電源的工作頻率并非固定不變,而是周期性地變化,由于EMI發(fā)射分布在較廣

2018-10-12 16:43:58

。這工作正常,直到我決定董事會所做的測量不夠準確(在時間軸上)。因此,我將生成的時鐘使能信號(2MHz)輸出到IO-Pin,并使用示波器測量頻率抖動。抖動似乎具有高斯分布,標準偏差約為28ns。我還測量

2020-08-19 06:09:57

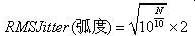

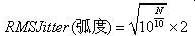

高信噪比=低ADC孔徑抖動嗎?在設計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產(chǎn)生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉(zhuǎn)換為時間抖動呢?

2019-08-13 06:27:54

目前的實時信號處理機要求ADC盡量靠近視頻?中頻甚至射頻,以獲取盡可能多的目標信息?因而,ADC的性能好壞直接影響整個系統(tǒng)指標的高低和性能好壞,從而使得ADC的性能測試變得十分重要?那要怎么測試高速ADC的性能?

2021-04-14 06:02:51

。

ADC基礎知識

抖動和信噪比之間的關系

在查閱現(xiàn)有文獻時,我們看到了有關ADC性能依賴于抖動參數(shù)的大量描述,并且通常此類標題會包含“高速”一詞,這不無道理。為了考察抖動和信噪比(SNR)之間

2025-06-05 11:20:18

對高速信號進行高分辨率的數(shù)字化處理需審慎選擇時鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

因為接收機鎖相環(huán)路 (PLL) 追蹤 f1 以下的抖動(從而排斥它),而發(fā)射 PLL 的頻率上限為 f2。從接收機的角度來看,使鏈路性能降低的隨機抖動降至這些限制之間。 圖2高速通信鏈路—隨機抖動測量

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數(shù)據(jù)進行傳輸?shù)囊恍藴什粩喑霈F(xiàn)。來自各行業(yè)的工程師們組成了各種委員會和標準機構,根據(jù)其開發(fā)標準的目標

2022-11-23 06:59:24

其它時鐘分配方法,其可降低整體抖動性能。您可使用如 LMK03806 等一款器件來克服這個問題,其在同一器件中整合了所有主時鐘發(fā)生器和時鐘分配功能(帶驅(qū)動器),如圖 1 所示。該器件可在 300MHz

2018-09-13 14:18:06

提升PF值、效率、瞬態(tài)響應,并降低THD。頻率抖動、時鐘同步和電壓運放擺率校正等特性進一步提升了芯片性能。PC8070還包含多種保護功能:輸出過電壓檢測,可調(diào)峰值電流限制、欠壓關斷和開環(huán)保護等。產(chǎn)品特點

2025-06-05 10:08:03

碼密度法測試ADC的INL和DNL時輸入正弦波的頻率和采樣頻率,采樣點有什么關系?需要采樣的周期是怎么確定的?看了美信AN2085里面舉了個例子,測MAX1193,8BIT,采樣頻率45M,輸入信號

2021-06-24 07:51:57

SI5347-EVB,評估板用于評估Si5347四路任意頻率抖動衰減時鐘倍頻器。 Si5347在單個IC中包含4個獨立的DSPLL,每個DSPLL具有可編程的抖動衰減帶寬。 Si5347-EVB通過

2019-02-27 11:19:26

值,即使在相對較低的輸入頻率下也不例外。本文我將使用安裝了 LTC2389-18 2.5Msps 18 位 ADC 和 LTC PScope 軟件的 DC1826A-A 演示板,來說明抖動對于

2018-07-19 16:23:22

fpga設計利用普通IO口輸出脈沖寬度為20ns脈沖,頻率為100Khz,但最終輸出頻率在示波器上觀察在50——120之間抖動。使用的時鐘為主板自帶時鐘125MHz

2018-08-30 13:39:01

ADC的動態(tài)性能。為了將這種影響最小化,ADC的時鐘源必須具有很低的定時抖動或相位噪聲。如果在選擇時鐘電路時沒有考慮該因素,則系統(tǒng)的動態(tài)性能在很大程度上將不由前端模擬輸入或ADC的質(zhì)量決定。理想時鐘

2019-05-30 05:00:04

描述適用于 GSPS 數(shù)據(jù)轉(zhuǎn)換器的低成本、高性能時鐘解決方案。此參考設計討論如何使用低噪聲頻率合成器 TRF3765 為 4 GSPS 模數(shù)轉(zhuǎn)換器 (ADC12J4000) 生成采樣時鐘。實驗展示了

2018-08-16 06:56:42

本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 在離線 ac-dc 轉(zhuǎn)換器中抖動脈沖寬度調(diào)制器 (PWM) 頻率經(jīng)證實可以通過將其由窄帶變?yōu)閷拵У姆绞絹斫档?EMI。本文將介紹一種用于抖動一個離線功率因數(shù)校正 (PFC) 預調(diào)節(jié)器 20%開關頻率

2010-09-11 16:48:36 20

20

抖動的概念和抖動的測量方法

在數(shù)字通信系統(tǒng),特別是同步系統(tǒng)中,隨著系統(tǒng)時鐘頻率的不斷提高,時間抖動成為影響通

2008-11-27 08:28:11 5084

5084

頻率響應法--頻率特性

2009-07-27 14:23:55 3725

3725

頻率響應法--對數(shù)坐標圖

2009-07-27 14:24:34 6763

6763 頻率響應法--極坐標圖

2009-07-27 14:26:12 4641

4641 頻率響應法-- 頻域性能指標和時域性能指標的關系

頻域性能指標和時域性能指標的關系

2009-07-27 14:28:56 13582

13582

用模擬時鐘IC替代昂貴的高頻率VCO,改善抖動性能

Analog Devices, Inc.,全球領先的高性能信號處理解決方案供應商,

2009-09-01 17:26:25 1723

1723 MAX3671 具有亞皮秒級抖動性能的頻率合成器,簡化了高速系統(tǒng)的時鐘設計

2009-09-18 08:32:46 1025

1025 Maxim推出具有亞皮秒級抖動性能的頻率合成器MAX367x

Maxim推出用于高速系統(tǒng)的帶有9路相位對齊LVPECL輸出的低抖動頻率合成器MAX3671/MAX3673。這兩款器件采用低噪聲VCO和PLL架

2009-11-09 15:55:48 1195

1195 電信頻率和波段的命名法

2010-02-07 15:55:46 1821

1821

您在使用一個高速模數(shù)轉(zhuǎn)換器 (ADC) 時,總是期望性能能夠達到產(chǎn)品說明書載明的信噪比 (SNR) 值,這是很正常的事情。您在測試 ADC 的 SNR 時,您可能會連接一個低抖動時鐘器

2010-12-25 09:46:42 3373

3373

在固定頻率(時鐘控制)功率轉(zhuǎn)換器中,窄帶發(fā)射通常發(fā)生在開關頻率,其連續(xù)諧波的能量也越來越低。

2011-08-25 14:39:05 5938

5938

為實現(xiàn)高信噪比(SNR),ADC的孔徑抖動必須很低(參見參考文獻1、2和3)。目前可提供孔徑抖動低至60 fs rms的ADC(AD9445 14位125 MSPS和AD9446 16位100 MSPS)。為了避免降低ADC的性能,必須采用抖動極低

2011-11-17 15:10:53 28

28 設計人員可以通過控制器的開關頻率抖動,減少一個脈沖寬度調(diào)制(PWM)控制器的電磁干擾(EMI)分布中頻譜分量的峰值幅度。時鐘抖動擴頻技術并非意在取代傳統(tǒng)的EMI降低技術,但它們與傳統(tǒng)技術的結(jié)合使用,可以減少系統(tǒng)中的EMI分布。它們還可以利用減少通過某些排放標準所需的屏蔽和濾波量來降低成本。

2013-02-19 14:07:10 3441

3441

美高森美公司(Microsemi Corporation,紐約納斯達克交易所代號:MSCC) 宣布推出六款新型多輸出、任意速率時鐘合成器和頻率轉(zhuǎn)換/抖動衰減產(chǎn)品,新產(chǎn)品的主要優(yōu)勢在于輸出時鐘的高頻率和超低抖動,以及內(nèi)部集成了時鐘驅(qū)動器和用戶可配置存儲區(qū)。

2013-06-19 11:55:44 2262

2262 我們知道在固定頻率PWM控制器中,窄帶發(fā)射通常發(fā)生在開關頻率,其連續(xù)諧波的能量會越來越低。采用頻率抖動技術(Frequency Jitter)的著眼點在于分散諧波干擾能量,我們使得開關電源的工作頻率

2016-12-14 10:15:04 17299

17299

了解高速ADC時鐘抖動的影響將高速信號數(shù)字化到高分辨率要求仔細選擇一個時鐘,不會妥協(xié)模數(shù)轉(zhuǎn)換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數(shù)轉(zhuǎn)換器的性能

2017-05-15 15:20:59 13

13 中國,北京-2017年6月29日-Silicon Labs(亦稱“芯科科技”,NASDAQ:SLAB)日前宣布推出全新的高性能晶體振蕩器(XO)系列產(chǎn)品,提供了業(yè)界最低抖動和最高靈活頻率的解決方案

2017-06-29 17:41:02 2807

2807 采用頻率抖動技術減小EMI 為抑制開關電源電磁干擾新思路

2017-09-14 14:08:01 14

14 ,窄帶發(fā)射通常發(fā)生在開關頻率,其連續(xù)諧波的能量會越來越低。采用頻率抖動技術(Frequency Jitter)的著眼點在于分散諧波干擾能量,我們使得開關電源的工作頻率并非固定不變,而是周期性地變化,由于EMI發(fā)射分布在較廣的頻率范圍而不是

2017-09-25 08:45:07 14

14 本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。 ADC 是現(xiàn)代數(shù)字解調(diào)器和軟件無線電接收機中連接模擬信號處理部分和數(shù)字信號處理部分的橋梁,其性能在很大程度上決定了

2017-11-27 14:59:20 18

18 工業(yè)及汽車系統(tǒng)的低EMI電源變換器設計(六)通過頻率抖動有效降低EMI

2019-04-08 06:07:00 2525

2525

ADI研討會:高性能時鐘: 解密抖動

2019-08-20 06:05:00 2532

2532 時鐘抖動性能主題似乎是時鐘,ADC和電源的當前焦點供應廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內(nèi)的數(shù)字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關系需要一些努力。

2019-09-14 11:24:00 9399

9399

對高速信號進行高分辨率的數(shù)字化處理需審慎選擇時鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

2020-08-01 11:26:11 1764

1764

對高速信號進行高分辨率的數(shù)字化處理需審慎選擇時鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

2020-08-20 14:25:16 1408

1408

14 位 125Msps 低功率雙通道 ADC 增強了高效基站收發(fā)器的性能

2021-03-18 23:35:36 4

4 MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

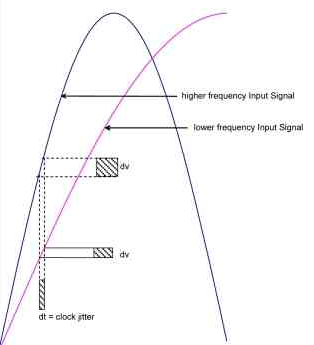

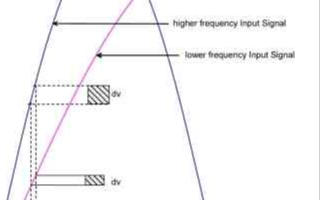

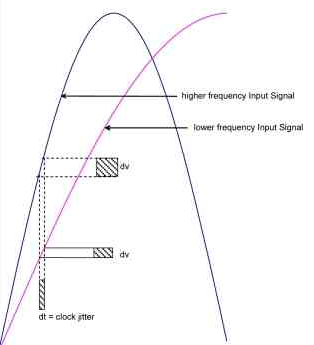

7 高速ADC使用外部輸入時鐘對模擬輸入信號進行采樣,如圖1所示。圖中顯示了輸入采樣時鐘抖動示意圖。 圖1、ADC采樣 輸入模擬信號的頻率越高,由于時鐘抖動導致的采樣信號幅度變化越大,這點在圖2中顯示的非常明顯。輸入信號頻率為F2=100MHz時,采樣幅度變化如圖紅色虛

2021-04-07 16:43:45 10607

10607

ADC時鐘接口中的最小抖動

2021-05-09 12:19:40 6

6 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 LMX2820 是一款高性能寬帶合成器,可生成 45 MHz 至 22.6 GHz 范圍內(nèi)的任何頻率。具有–236 dBcHz 品質(zhì)因數(shù)和高相位檢測器頻率的高性能PLL 可以實現(xiàn)極低的帶內(nèi)噪聲和集成

2021-06-12 09:05:00 3047

3047

頻率抖動技術在開關電源EMC中的應用綜述

2021-06-18 10:18:29 22

22 作者: Richard Zarr

如果您在通信行業(yè)工作,那么您可能很熟悉抖動對系統(tǒng)性能的影響。抖動不僅會降低數(shù)據(jù)轉(zhuǎn)換器的性能,而且還可在高速數(shù)字系統(tǒng)中產(chǎn)生誤碼。憑直覺判斷,給時鐘增加噪聲會增大

2021-11-23 17:45:07 2967

2967

MSP430或STM32,在使用內(nèi)部ADC出現(xiàn)的采樣數(shù)據(jù)異常抖動問題采樣設計:用于檢測供電線路電流及電壓。產(chǎn)品運行在兩種模式下,1、低功耗靜態(tài)模式(倉儲態(tài)),2、全功能全速運行模式(工作態(tài))。在倉儲

2021-12-08 09:06:10 12

12 Silicon Labs 聲稱其新型晶體振蕩器 (XO) 提供業(yè)界最低的抖動以及頻率靈活的性能。Si54x Ultra 系列 XO 在整個工作范圍內(nèi)將整數(shù)和分數(shù)頻率的超低抖動降至 80 飛秒 (fs)。

2022-08-10 15:36:22 1412

1412 本應用筆記介紹了超低抖動時鐘頻率合成器的設計思路。目標性能在2GHz時<100fs的邊沿到邊緣抖動。討論和仿真測試結(jié)果表明,目標抖動比最初預期的更難實現(xiàn)。討論組件變量和權衡,以用于未來的開發(fā)工作。

2023-01-16 11:09:56 2108

2108

DS1086L為3.3V擴頻振蕩器,用于符合電磁兼容性(EMC)標準(如FCC part 15或CISPR 22)的應用。理想情況下,這種架構的峰值功率衰減始終與抖動跨度和輸出頻率與抖動頻率之比成正比。本應用筆記討論了由于功率譜測量方式而產(chǎn)生的這些參數(shù)的實際限制。

2023-03-01 17:11:33 1558

1558

PD/QC快充電源ic U6648具有±5%的隨機頻率抖動功能,開關頻率抖動分散了諧波擾動能量,獲得良好的EMI特性。

2023-05-08 10:53:03 650

650 電子發(fā)燒友網(wǎng)站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

1 晶振中的抖動有哪兩種主要類型? 晶振中的抖動主要分為相位抖動和頻率抖動。 相位抖動是指晶振輸出信號相位的隨機波動。這種波動可能是由于晶體本身的不完美造成的,也可能是由于外部環(huán)境的干擾引起的。相位抖動

2024-01-25 13:51:07 1679

1679 電子發(fā)燒友網(wǎng)站提供《CDC7005高性能時鐘頻率合成器和抖動消除器數(shù)據(jù)表.pdf》資料免費下載

2024-08-21 11:14:32 0

0 電子發(fā)燒友網(wǎng)站提供《PLL抖動對GSPS ADC SNR及性能優(yōu)化的影響.pdf》資料免費下載

2024-09-20 11:11:29 0

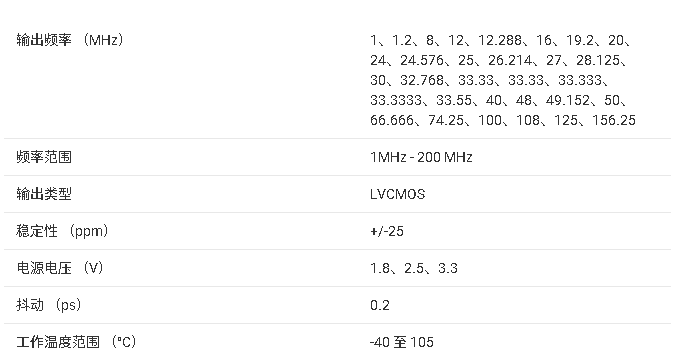

0 LMK6x 器件是一款超低抖動、固定頻率振蕩器,將 BAW 作為諧振器源。該器件在工廠根據(jù)特定工作模式進行編程,包括頻率、電壓、輸出類型和功能引腳。LMK6x 采用高性能小數(shù)分頻器,能夠產(chǎn)生指定范圍內(nèi)的任何頻率,為所有頻率需求提供單一器件系列。

2025-09-11 10:32:46 766

766

LMK6x 器件是一款超低抖動、固定頻率振蕩器,將 BAW 作為諧振器源。該器件在工廠根據(jù)特定工作模式進行編程,包括頻率、電壓、輸出類型和功能引腳。LMK6x 采用高性能小數(shù)分頻器,能夠產(chǎn)生指定范圍內(nèi)的任何頻率,為所有頻率需求提供單一器件系列。

2025-09-11 10:38:12 689

689

電子發(fā)燒友App

電子發(fā)燒友App

評論