晶振在布局時,一般是不能放置在PCB邊緣的,今天以一個實(shí)際案例講解。

2022-09-08 09:36:03 5675

5675 智能穿戴不同的主控芯片對晶振頻率要求不同,常用頻率是16MHz、24MHz、26MHz、32MHz、48MHz;智能穿戴尺寸小,晶振尺寸一般選擇2520、2016、1612;智能穿戴功耗低,無源晶振需選擇低負(fù)載和低阻抗的,有源晶振電壓1.8~3.3V,并要求晶振的抗震防摔性能好。

2024-04-11 09:17:25 1927

1927

如果有人和你說18.432MHZ晶振,您肯定絕對很正常。但當(dāng)采購和你說1.8432MHZ晶振,你是否會質(zhì)疑是不是采購在制作bom表單的時候,小數(shù)點(diǎn)打錯位置了,實(shí)則上是你錯了。上圖是CTS 5070

2015-07-15 16:37:02

最近在學(xué)單片機(jī)定時器初值的計算方法,下面大概列出來12MHz晶振與11.0592MHz兩種不同晶振的區(qū)別,用10ms和50ms的計算方法,希望能幫助到大家,有問題可以評論區(qū)提問一、10MS定時器初值

2021-11-22 07:49:33

系列。 一般來說MCU需要接入一個主頻和一個時鐘頻率,STM32F1系列也不例外。其中主頻4~16MHZ居多,一般搭配常用的8MHZ晶振。本文主要講解STM32系列MCU匹配主頻晶振的推薦選型及注意事項(xiàng)等

2018-07-02 00:12:34

有對晶振很了解的,一直有個疑問,layout的時候晶振下面到底要不要挖空,有的說挖空,有的不挖空。公司的很多項(xiàng)目我看也都沒有挖空,挖空與否有多大影響

2025-03-10 06:32:21

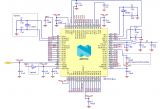

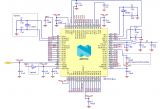

理清功能方框圖

網(wǎng)表導(dǎo)入PCB Layout工具后進(jìn)行初步處理的技巧射頻PCB布局與數(shù)模混合類PCB布局

無線終端PCB常用HDI工藝介紹信號完整性(SI)的基礎(chǔ)概念

射頻PCB與數(shù)模混合類PCB

2023-09-27 07:54:33

晶振選擇和電路板設(shè)計 晶振的選擇和PCB板布局會對VCXO CLK發(fā)生器的性能參數(shù)產(chǎn)生一定的影響。選擇晶體時,除了頻率、封裝、精度和工作溫度范圍,在VCXO應(yīng)用中還應(yīng)注意等效串聯(lián)電阻和負(fù)載電容

2018-09-13 16:09:28

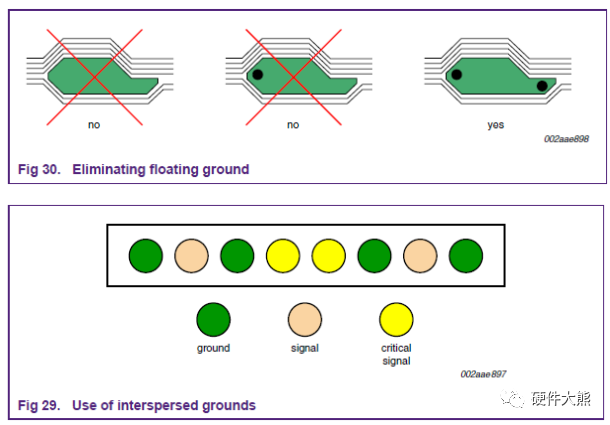

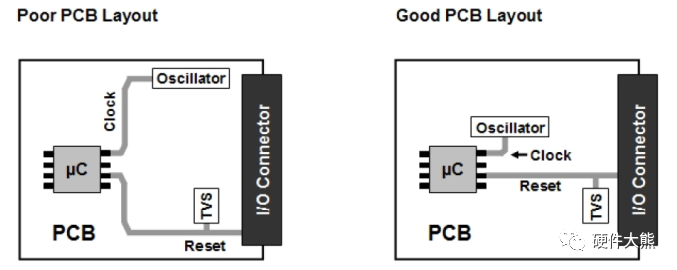

好于晶體晶振器件;3、時鐘信號走線長度盡可能短,線寬盡可能大,與其它印制線間距盡可能大,緊靠器件布局布線,必要時可以走內(nèi)層,以及用地線包圍;4、通過背板從外部引入時鐘信號時有特殊的設(shè)計要求,需要詳細(xì)

2010-01-20 21:46:05

好于晶體晶振器件;3、時鐘信號走線長度盡可能短,線寬盡可能大,與其它印制線間距盡可能大,緊靠器件布局布線,必要時可以走內(nèi)層,以及用地線包圍;4、通過背板從外部引入時鐘信號時有特殊的設(shè)計要求,需要詳細(xì)

2010-01-20 21:48:08

與CO為2pf,CPCB=4pF可以得出CL1為6.8pf.左右注意:CPCB,CS 在不同的芯片,不同的PCB布局當(dāng)中是不同的,因此在計算當(dāng)中我做了修改,在實(shí)際的運(yùn)用當(dāng)中,我們貼片式晶振中電容一般選

2021-08-12 08:27:58

流向排布,且靠近晶體擺放整齊緊湊; (4)晶體靠近芯片處擺放,兩者間的走線盡量短而直。 可以參考如下圖布局方式: 經(jīng)整改后,樣機(jī)測試結(jié)果如下: 四、結(jié)論 現(xiàn)今很多系統(tǒng)晶振現(xiàn)今很多系統(tǒng)晶振時鐘

2018-09-19 16:31:11

`大家好,想聽聽大家如何看待如何避免晶振的諧波輻射問題(晶振布局位置、芯片供電電壓、電纜長度)?`

2015-08-22 23:41:00

急急急!哪位高手賜教一下,PIC18F242是否可以用40MHz的晶振?查了數(shù)據(jù)手冊上面說可以工作在40MHz的晶振和時鐘頻率下,但是我用了40MHz的晶振,單片機(jī)的指令周期問什么是0.3ns而不是0.1ns?SIM仿真的時候是正確的,而連接硬件仿真時卻出現(xiàn)上述的問題?為什么?

2012-11-26 15:25:36

設(shè)計時,AD2S1210的時鐘輸入采用8.192MHZ的有源晶振,選擇晶振時對有源晶振的功率有什么要求???一個有源晶振能不能給兩個AD2S1210芯片提供時鐘輸入???感謝!

2023-12-07 07:07:43

AD9650 40MHz采樣和80MHz采樣采集數(shù)據(jù)不同, 70MHz中頻輸入通過FPGA ila抓取 大量數(shù)據(jù)130k個點(diǎn),40Mhz采樣的數(shù)據(jù)比80MHz采樣數(shù)據(jù)偏小。這是為什么?

2018-08-10 08:48:38

AD9650 40MHz采樣和80MHz采樣采集數(shù)據(jù)不同, 70MHz中頻輸入通過FPGA ila抓取 大量數(shù)據(jù)130k個點(diǎn),40Mhz采樣的數(shù)據(jù)比80MHz采樣數(shù)據(jù)偏小。這是為什么?

2023-12-12 07:39:29

ADAU1701如何輸出40K正弦波,晶振為12.288Mhz

2019-09-23 19:03:45

ADS1256對晶振要求嚴(yán)格嗎?我看規(guī)格書里面介紹ELECTRICAL CHARACTERISTICS 采用無源晶振是從2MHz到10MHz之間,是否可以采用7.6MHz或者8MHz晶振?

2024-12-02 06:07:03

為什么ds1302不起振 手按下晶振時間會走不按就不走

2014-06-20 19:37:44

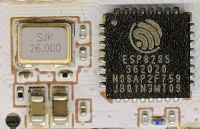

ESP32-D2DW 40MHZ晶振不能起振,請問可能是什么原因?

晶振的第三腳電壓1.5V左右,晶振本身在其它ESP32模組上驗(yàn)證能正常工作。

請問正常情況下XTAL_N在芯片啟動后會輸出什么樣的信號?是固定的直流電壓嗎?還是會某種波形?

2024-07-01 07:07:10

最近在選擇芯片,想請教大家?guī)讉€問題:

1、ESP32-S3-WROOM-1(N8R8)是否需要連接外圍40MHz晶振?

2、ESP32-S3-WROOM-1(N8R8)是否可以用任意IO口作為SPI和I2C接口?

3、SPI口的使用需不需要考慮到內(nèi)部的flash接口?

2024-07-01 06:21:15

最近在選擇芯片,想請教大家?guī)讉€問題:1、ESP32-S3-WROOM-1(N8R8)是否需要連接外圍40MHz晶振?2、ESP32-S3-WROOM-1(N8R8)是否可以用任意IO口作為SPI和I2C接口?3、SPI口的使用需不需要考慮到內(nèi)部的flash接口?

2023-03-13 10:03:59

`MSP430晶振布局要領(lǐng)`

2013-05-17 21:36:03

嗨,喂25MHz到OSC1,然后內(nèi)部縮放到41MH,我能從OSC2 41MHz得到一個輸出來驅(qū)動其他芯片,或者我必須增加另一個40MHz時鐘來驅(qū)動其他芯片?謝謝 以上來自于百度翻譯 以下為原文

2019-01-14 08:29:44

STM的MCU選擇外接晶振,是選擇高頻還是選擇低頻,說明是什么?比如stm32L486,datasheet給出的最大主頻為80MHz,所以通過外接晶振倍頻可以達(dá)到4Mhz、8Mhz、16Mhz

2022-12-22 07:13:44

請問這顆DAC能實(shí)現(xiàn)輸出40MHZ的速度嗎,兩個電壓軌,占空比50%就行,有其它的推薦嗎,設(shè)計簡單,性價比高一點(diǎn)的。

2024-11-26 07:11:19

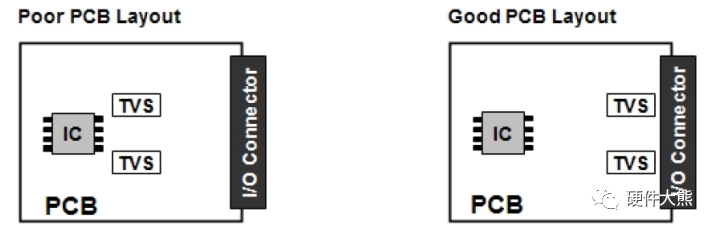

用的PLL電路需要的周邊配置主要是電容、電阻、電感,其穩(wěn)定度和價格方面遠(yuǎn)遠(yuǎn)好于晶體晶振器件;3、時鐘信號走線長度盡可能短,線寬盡可能大,與其它印制線間距盡可能大,緊靠器件布局布線,必要時可以走內(nèi)層,以及用地線包圍;4、通過背板從外部引入時鐘信號時有特殊的設(shè)計要求,需要詳細(xì)參考相關(guān)的資料1

2010-01-20 21:45:40

例如stm32l486xx,主頻如果設(shè)置成80Mhz,外部晶振有4Mhz,8Mhz,16Mhz,40Mhz,或者直接80Mhz的,哪個晶振是最優(yōu)選擇?

2024-04-15 07:59:39

`主板上晶振主要分為時鐘晶振:與時鐘芯相連 頻率為14.318MHz 工作電壓為1.1--1.6V實(shí)時晶振:與南橋相連 頻率為32.768MHz 工作電壓為0.4V左右聲卡晶振:與志卡芯片相連

2013-03-21 14:59:58

,20PPM; 12MHz/16MHz/24MHz/25MHz,27MHz/20pF,20ppm b,STM32 RTC【6pF】晶振,2*6,3*8;5PPM,10PPM,20PPM c,無線收發(fā)芯片用的晶振

2011-06-05 21:53:08

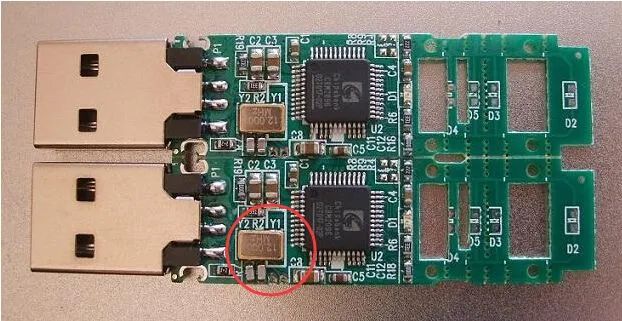

最近在調(diào)ESP32的芯片,使用的外部晶振頻率為40MHZ,負(fù)載電容選用兩個22PF電容,最近軟件在做功能驗(yàn)證,在抓取芯片內(nèi)部WIFI部分的smartconfig過程中,發(fā)現(xiàn)有時會成功,但幾率很小

2019-11-22 17:42:32

請問無刷電機(jī)如何去進(jìn)行pcb布局?無刷電機(jī)的pcb走線規(guī)劃是怎樣的?

2021-06-26 07:29:35

分享無線收發(fā)器使用到的石英晶振a,工業(yè)級-40~85度,頻率點(diǎn):32.768KHz 、12.5pF,20PPM; 12MHz/16MHz/24MHz/25MHz,27MHz/20pF,20ppm b

2011-05-30 21:26:29

單片機(jī)的晶振頻率怎么選擇,同樣是51系列,走的是11.0592mhz,有的用mhz

2023-10-25 06:40:38

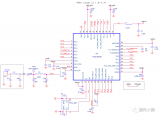

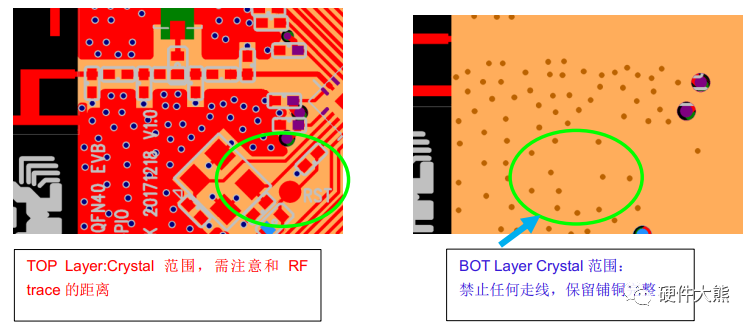

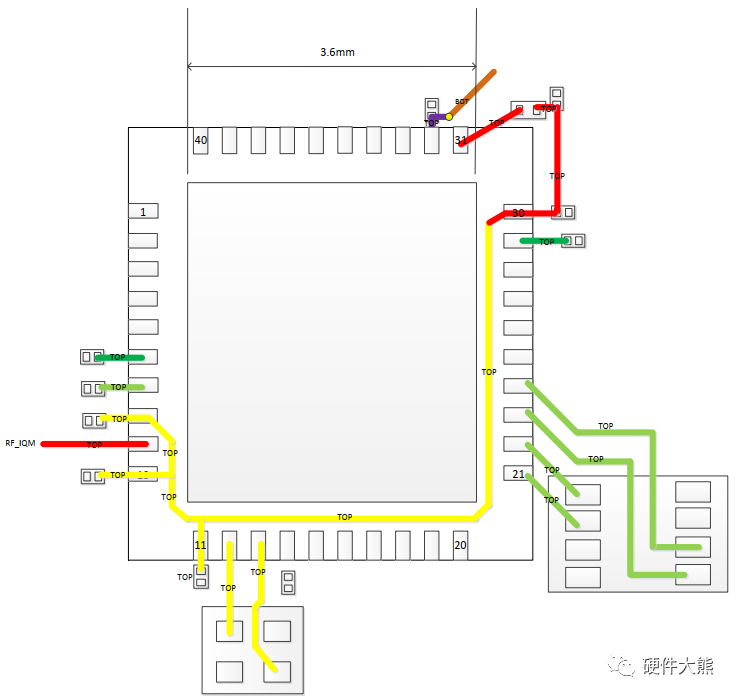

,不要布局在板邊,離板邊至少要有10mm以上的距離,晶體和晶振靠近芯片放置,同層放置,不要打孔,預(yù)留包地的空間,如下圖所示;

⑤ 相同結(jié)構(gòu)電路,采用 “對稱式”標(biāo)準(zhǔn)布局 (直接相同模塊復(fù)用),滿足信號

2023-09-08 13:53:56

開關(guān)電源的PCB設(shè)計(布局、排版、走線)規(guī)范

2015-05-21 11:49:28

電容值不正確。

3. PCB Layout 分析

**·**檢查布局:使用電路設(shè)計軟件或手動檢查PCB Layout,確保晶振電路與單片機(jī)或芯片引腳的布局盡可能靠近,以減少信號傳輸?shù)母蓴_和損耗

2024-03-06 17:22:17

我用atf1508as,100mhz晶振,想產(chǎn)生一個高精度的pwm,,程序功能仿真能通過,下到片子上不行,,,同樣的程序用40mhz的晶振就可以,換100mhz的就不行,,什么原因了?求幫助

2013-04-04 07:45:37

。。26mhz晶振電源是從PMU輸出,也需包地保護(hù),線寬12mil。其他AVDD,DVDD,VCCRF等,都可走12mil。除PA供電電源,其他電源線換層時小孔至少2個。所有的電源線都是干擾源,故不能靠近

2013-04-25 17:08:34

布局布線,必要時可以走內(nèi)層,以及用地線包圍;4、通過背板從外部引入時鐘信號時有特殊的設(shè)計要求,需要詳細(xì)參考相關(guān)的資料。此外還要做一些說明:總體來說晶振的穩(wěn)定度等方面好于晶體,尤其是精密測量等領(lǐng)域

2015-01-21 09:34:05

我有一個關(guān)于內(nèi)部時鐘生成的問題。

外部 24MHz 時鐘連接到 MHzECO 端子。

是否可以內(nèi)部生成 40MHz 時鐘并將 PLL 時鐘設(shè)置為 40MHz?

如果可能的話請告訴我如何做。

2025-07-30 07:26:47

` 本帖最后由 youyou920 于 2019-9-3 17:25 編輯

本人8年LAYOUT經(jīng)驗(yàn),熟悉PCB板的布局布線,精通的產(chǎn)品有電腦臺式機(jī),一體機(jī),筆記本,工控,基帶板,背板,射頻等

2017-03-03 09:47:32

以及晶片厚薄與晶振的頻率密切相關(guān),一般來講,石英晶振的頻率越高,需要的石英晶片越薄。舉個例子40MHZ的石英晶體所需的晶片厚度是41.75毫米,這樣的厚度還算可以做到,但100MHZ的石英晶體,所需

2016-06-07 10:57:30

仿真出來的和實(shí)際PCB布局,但是到40MHZ有點(diǎn)不像方波了,有什么解決辦法嗎

2024-09-05 08:02:20

基頻?比如基頻為20MHZ的晶體,五次泛音之后就可以得到100MHZ的晶體。一般以經(jīng)驗(yàn)來講,40MHZ以下基本都是基頻晶振,而40MHZ以上,則是泛音晶振了。晶振頻率的高低與晶片有什么樣的聯(lián)系?一般來講

2016-07-20 10:59:51

我有一個20~40MHz左右的掃頻信號輸出,想把它轉(zhuǎn)換成恒流源輸出,請問應(yīng)該怎么做?我試過了直接使用集成芯片OPA861和OPA860,但是頻率到達(dá)1MHz以上后衰減很嚴(yán)重,而且也失去了恒流特性

2024-09-03 07:43:52

在畫PCB的時候,8M晶振底下是不是不能走線? 晶振到STM32輸入的兩個引腳不能經(jīng)過過孔對嗎?

2019-03-18 06:35:52

我們單位準(zhǔn)備用AD9361做一塊LTE的FMC子板,我看了一些商用的參考子板,發(fā)現(xiàn)板載晶振基本都是10MHz,20MHz或40MHz,LTE的采樣率不是30.72MHz嗎?為什么不用30.72MHz

2018-07-31 07:51:05

ad芯片自帶一個晶振40mhz,fpga外部有一個50mhz 的晶振,兩者是不是算作異步通信呢?時鐘設(shè)計應(yīng)該注意什么問題呢?

2019-05-08 04:50:03

誰有高速PCB布局布線規(guī)范,謝謝

2020-04-16 21:10:10

描述這種“射頻布局參考設(shè)計”顯示出卓越的適用于在 868 MHz 和 915 MHz 頻帶中低功耗射頻設(shè)備的去耦和布局技術(shù)。特性 推薦的可實(shí)現(xiàn)最佳性能的 PCB 布局PCB 層疊射頻去耦組件類型和值組件制造商

2022-09-20 06:21:37

ESP32-WROVER-IBIOT常用12MHZ/16MHZ/24MHZ/26MHZ/32MHZ/32.768K等無源晶振 有需要的老板可聯(lián)系QQ:***號:15013461744 大量現(xiàn)貨,原裝正品。

2020-04-01 15:09:03

ESP32-WROVER-IBIOT常用12MHZ/16MHZ/24MHZ/26MHZ/32MHZ/32.768K等無源晶振 有需要的老板可聯(lián)系QQ:***號:15013461744 大量現(xiàn)貨,原裝正品。

2020-03-27 11:18:16

高頻正弦波(40MHz以上)變換成方波的芯片有哪些可以用?高頻的電壓比較器芯片能行嗎?

2015-08-04 16:54:16

The HA-2541 is the first unity gain stable monolithicoperational amplifier to achieve 40MHz unity

2009-01-07 13:03:35 6

6 The ADS5421 is a high-dynamic range 14-bit, 40MHz, pipelined Analog-to-Digital Converter (ADC

2010-06-04 14:40:08 10

10

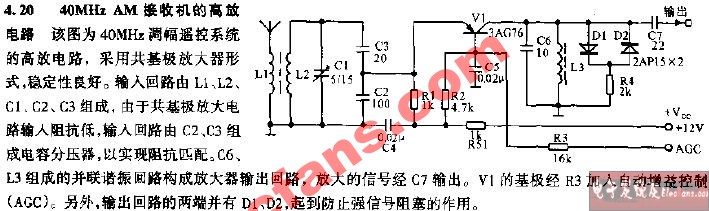

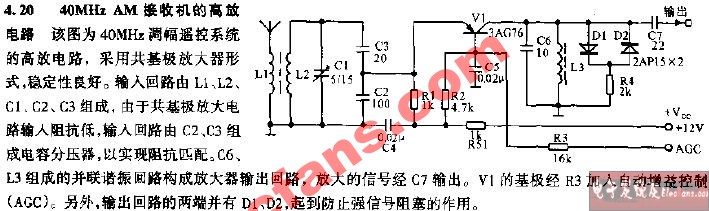

40MHz AM接收機(jī)的高放電路

2009-03-13 20:30:37 2450

2450

介紹了PCB Layout零件布局走線的一般原則,數(shù)字信號走線盡量放置在數(shù)字信號布線區(qū)域內(nèi)等知識

2012-06-25 11:25:17 6047

6047 開關(guān)電源的PCB設(shè)計(布局、排版、走線)規(guī)范,感興趣的小伙伴們可以看看。

2016-07-26 14:09:33 0

0 開關(guān)電源的PCB設(shè)計(布局、排版、走線)規(guī)范

2016-09-06 16:03:47 0

0 PCB layout中的走線策略16頁,臺灣原廠規(guī)范

2016-12-16 21:58:19 0

0 MSP430晶振布局要領(lǐng)。

2018-04-28 11:04:45 0

0 的layout顯得尤其的重要,有如下幾點(diǎn)需要注意。

? 兩個匹配電容盡量靠近晶振擺放。

? 晶振由石英晶體構(gòu)成,容易受外力撞擊或跌落的影響,所以在布局時,最好不要放在PCB邊緣,盡量靠近芯片擺放。

?...

2022-02-10 14:39:38 4465

4465

本篇文章會著重介紹一下晶振的常見問題原因分析,還有就是比較重要的PCB布局講解。

2021-03-14 16:50:41 11028

11028 LT5538 - 40MHz 至 3.8GHz 對數(shù)射頻功率檢波器具 75dB 動態(tài)范圍

2021-03-21 11:21:25 0

0 發(fā)生問題。比如,16MHz晶振給一個2.4G藍(lán)牙芯片提供參考時鐘,如果16MHz出現(xiàn)頻偏,比如偏-48ppm(頻率為15.999223MHz),由于射頻是參考時鐘倍頻上去的,也會出現(xiàn)-48ppm的頻偏(藍(lán)牙頻點(diǎn)

2022-06-06 17:12:23 8543

8543 儀器頻標(biāo),時間標(biāo)準(zhǔn),頻率校準(zhǔn)通訊,網(wǎng)絡(luò),單片機(jī),其他常用頻率元器件有源貼片晶振 OSC3225 40MHZ 技術(shù)數(shù)據(jù)手冊免費(fèi)下載。

2022-07-23 10:05:41 0

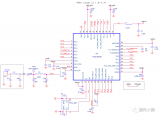

0 《一款射頻芯片的layout設(shè)計指導(dǎo)案例-篇章1》中,我們闡述了RTL8762元件布局順序、DC/DC電路元件布局走線、電源Bypass布局規(guī)范、外部flash布局走線、RF布局走線,

2023-06-06 14:08:03 1976

1976

,如果時鐘出錯了,整個電路或者通信就會發(fā)生問題。比如,16MHz晶振給一個2.4G藍(lán)牙芯片提供參考時鐘,如果16MHz的晶振出現(xiàn)頻偏,比如偏-48ppm(頻率為15.999223MHz),由于射頻是參考時

2025-11-21 15:37:54 4534

4534

電子發(fā)燒友網(wǎng)站提供《有源貼片晶振OSC3225 40MHZ 規(guī)格書.pdf》資料免費(fèi)下載

2022-07-07 16:08:40 0

0 無源貼片晶振SMD322540MHZ4腳-40~85℃

2022-08-19 14:13:59 0

0 無源晶振SMD322533.000000MHz7pF-10ppm+10ppm-40~+85℃封裝:SMD3225

2022-08-19 16:00:50 1

1 有源貼片晶振OSC503240MHZ4P±10PPM~30PPM-40~+85℃;-20到+70℃

2022-08-24 14:13:38 0

0 有源貼片晶振OSC705040MHZ4P±10PPM~30PPM-40~+85℃;-20到+70℃

2022-08-24 14:13:54 0

0 有源直插晶振PXO40MH4腳±10PPM~30PPM-40~+85℃;-20到+70℃DIP14/DIP08

2022-08-24 14:14:09 0

0 電子發(fā)燒友網(wǎng)站提供《40MHz帶通濾波器設(shè)計實(shí)例應(yīng)用.doc》資料免費(fèi)下載

2023-11-20 09:58:34 11

11 如何優(yōu)化晶振布局與連接 晶振是電子設(shè)備中常見的元件之一,用于提供時鐘信號和穩(wěn)定的頻率參考。在進(jìn)行晶振布局和連接時,需要考慮一系列的因素以確保其工作穩(wěn)定可靠。本文將詳細(xì)介紹如何優(yōu)化晶振布局和連接,從而

2023-12-18 14:09:22 1888

1888 為什么晶振下方不能走信號線? 晶振作為數(shù)字電路中常見的一個元件,用于產(chǎn)生穩(wěn)定的時鐘信號,是整個電路的重要組成部分。在設(shè)計電路布局時,有一個重要的原則是盡量避免信號線靠近晶振,尤其是在晶振下方布線

2024-01-23 16:43:11 2754

2754 振蕩器,它需要外部電源來提供能量以維持振蕩。通常包括晶振芯片和外部電路,通過反饋機(jī)制產(chǎn)生穩(wěn)定的振蕩信號。二、晶振擺放規(guī)則近距離放置:將晶振封裝與相關(guān)的晶體管、放大

2024-05-09 08:10:23 2427

2427

射頻(RF)PCB走線規(guī)則是確保無線通信設(shè)備性能的關(guān)鍵因素之一。在高頻信號設(shè)計中,PCB走線不僅承載著電流,還對信號的完整性和質(zhì)量有著顯著影響。

2024-05-16 18:18:22 6169

6169 個2.5G模塊主板上常用到一款40MHz無源晶振,這款2.5G模塊晶振具有超小型封裝和高精度特性,對于無線藍(lán)牙模塊來說,都是十分合適,選擇一款合適2.5G模塊晶振其對頻

2024-08-12 15:09:29 811

811

電子發(fā)燒友網(wǎng)站提供《LMV112 40MHz雙通道時鐘緩沖器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-08-22 11:41:45 0

0 可能靠近使用它的IC,以減少走線長度和信號衰減。 避免將晶振放置在高溫區(qū)域或靠近可能產(chǎn)生熱量的組件。 電源和地線布局 : 為晶振提供穩(wěn)定的電源和地線連接,避免電源噪聲影響晶振的穩(wěn)定性。 使用寬的地線和電源線,以減少阻抗和噪聲。 走線設(shè)計 : 保持晶振

2024-09-19 10:55:27 2684

2684

電子發(fā)燒友App

電子發(fā)燒友App

評論