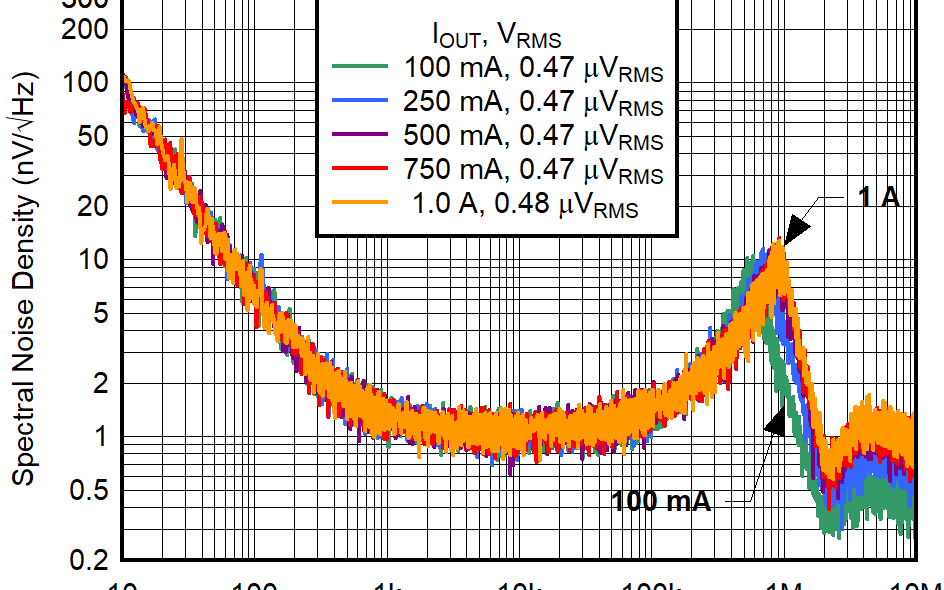

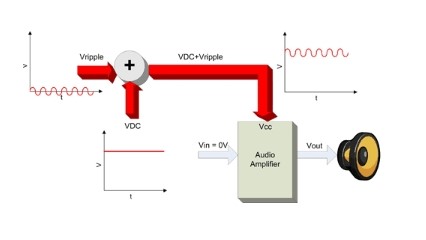

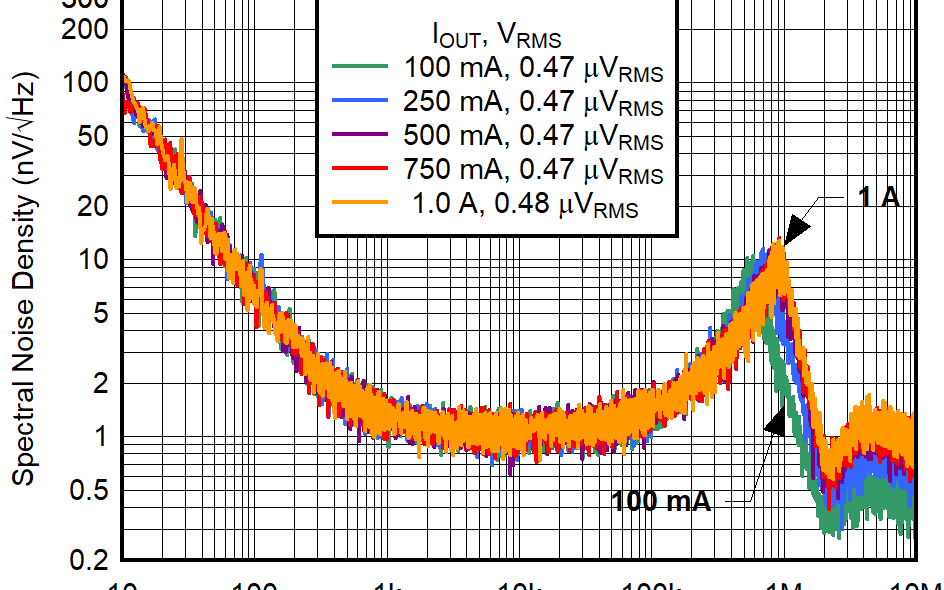

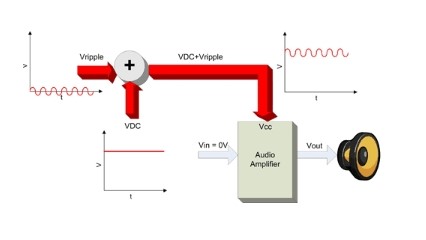

是電子器件,因此它們會自行產生一定量的噪聲。選擇低噪聲LDO并采取措施來降低內部噪聲對于生成不會影響系統性能的清潔電源軌而言不可或缺。 識別噪聲 理想的 LDO 會生成沒有交流元件的電壓軌。遺憾的是,LDO 會像其他電子器件一樣自行產生噪聲。圖1顯示了這種噪聲在時域

2022-04-18 18:05:29 6842

6842

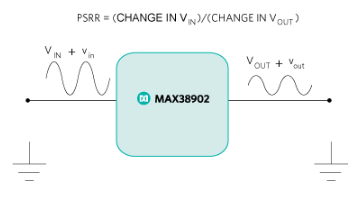

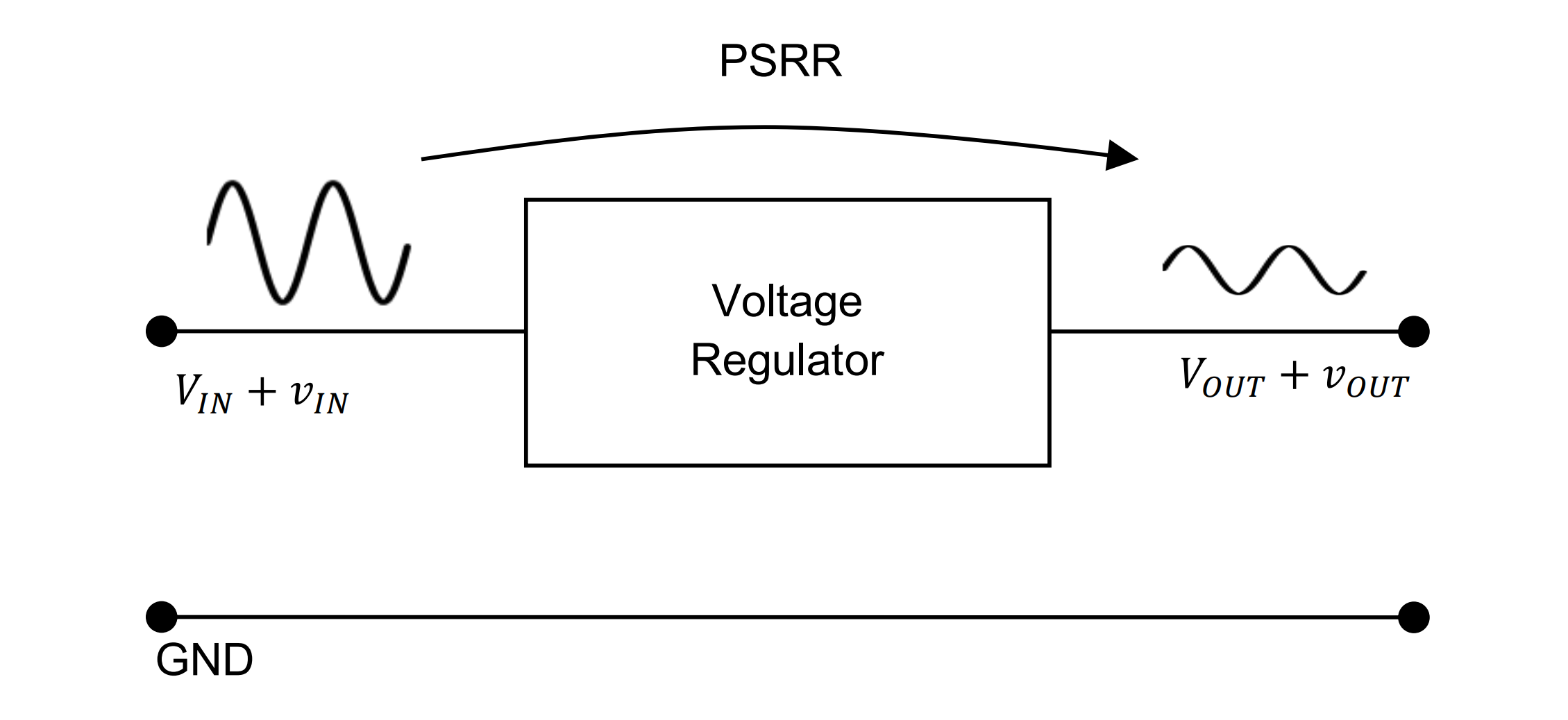

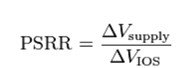

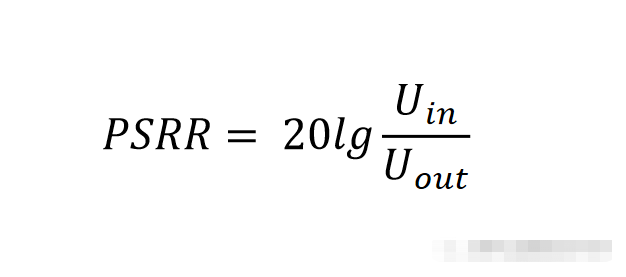

電源抑制比的代號是PSRR,這個詞不是運算放大器的專屬,如果你研究過LDO,或DCDC芯片,你會發現,PSRR也是LDO以及DCDC的關鍵指標參數。通俗點來說,PSRR是表征電路對電源電壓波動抑制

2024-11-07 09:07:37 3529

3529

LDO是一種微功耗的低壓差線性穩壓器,它通常具有極低的自有噪聲和較高的電源抑制比PSRR(PowerSupplyRejectionRatio)。

2011-09-29 10:46:00 6199

6199

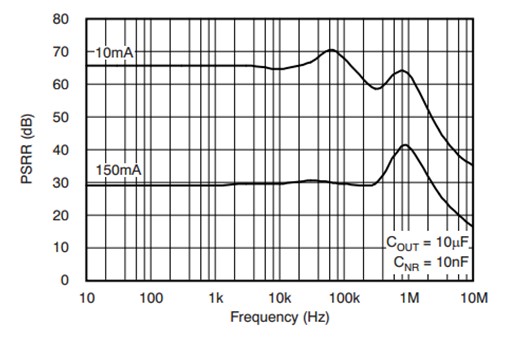

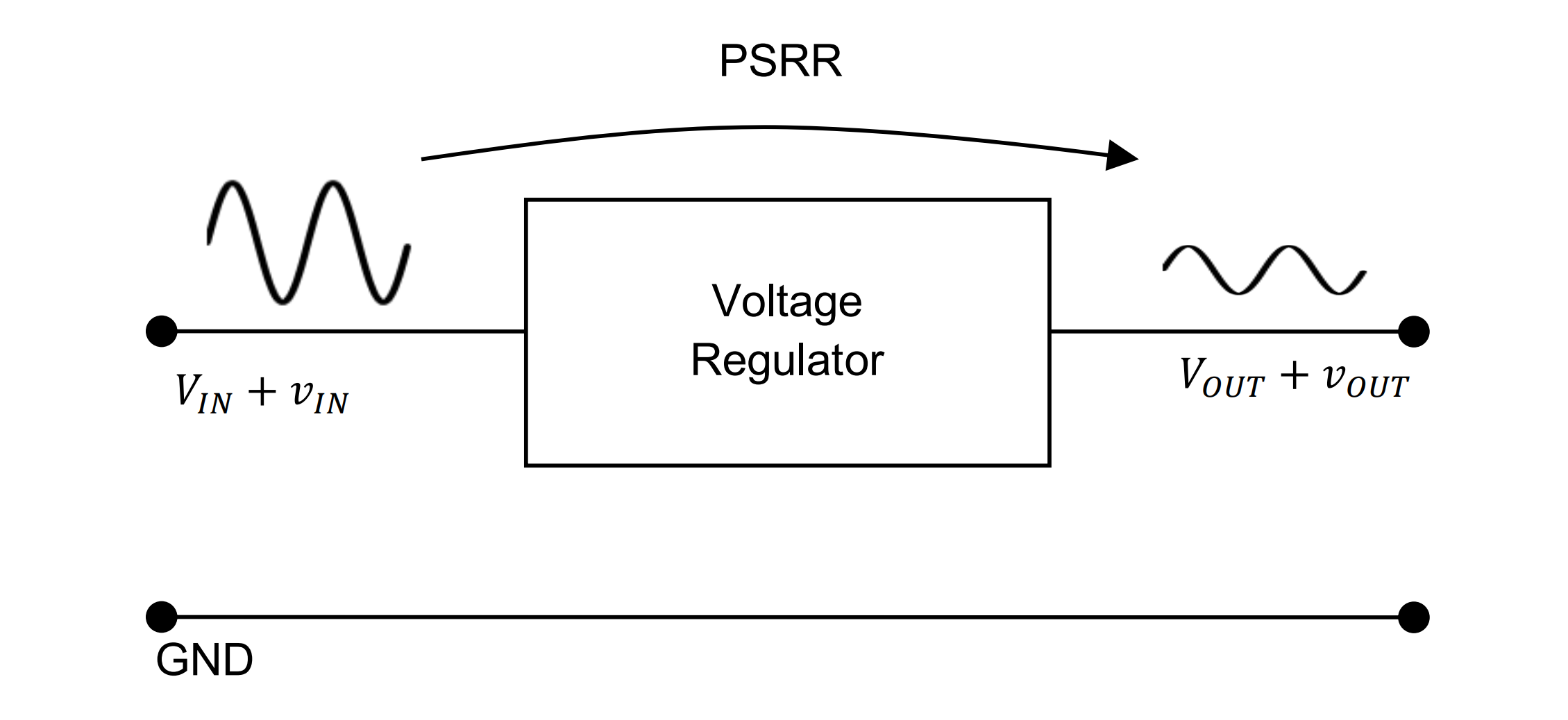

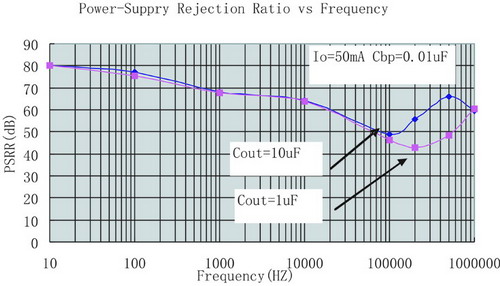

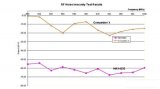

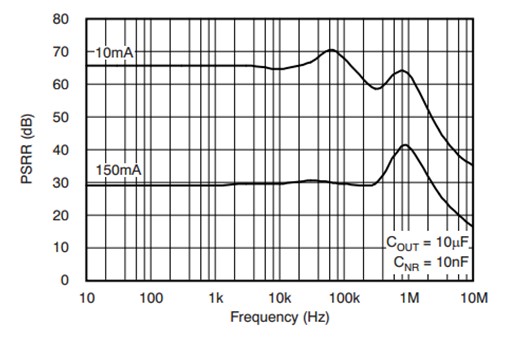

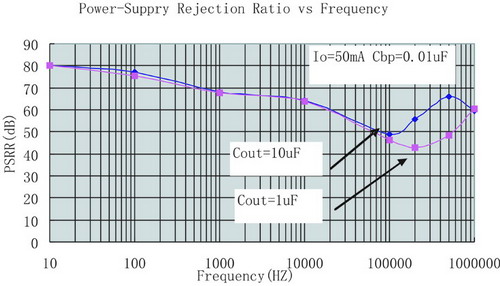

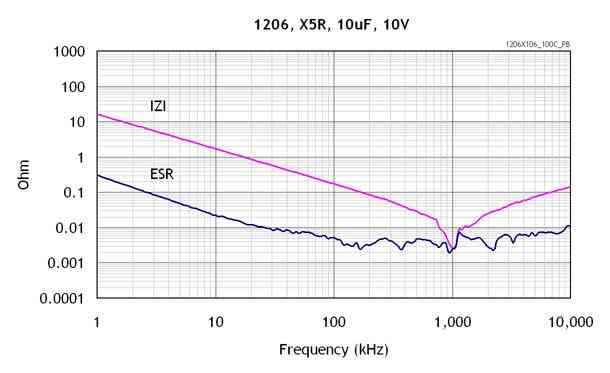

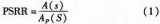

Ramus在博客中介紹了噪音對信號調節設備的不利影響:減少高速信號鏈電源問題。然而,電源抑制比(PSRR)仍然通常被誤認為單一的靜態值。在這篇文章中,我將嘗試說明什么是PSRR以及影響它的變量有哪些。 什么是 PSRR ? PSRR是許多LDO數據手冊中的公

2018-06-28 10:16:00 25787

25787

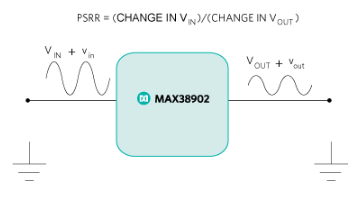

電源抑制比 (PSRR) 用于衡量 LDO 清除或抑制由上游其他元件傳入噪聲的能力。對于高端 ADC,為了更大限度地減少位錯誤,輸入電源噪聲要求不斷提高。

2022-03-09 09:24:03 1450

1450

低壓差線性穩壓器(LDO)相比 DC-DC 的優點之一,是輸出電壓紋波小。但是高速電路下,LDO 的電源抑制比(PSRR)也是不可忽略的因素,通常被誤認為是單一的靜態值,本篇文章將詳細講解電源抑制比(PSRR)及如何測量它。

2022-08-30 17:09:25 26513

26513

電源抑制比 ,英文名Power Supply Rejection Ratio,簡稱PSRR,它描述了電路抑制任何電源變化傳遞到其輸出信號的能力,通常以dB為單位進行測量,用來描述輸出信號受電源

2022-09-09 15:37:05 40955

40955

在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩壓器中的影響。讓我們簡要討論一下什么是 LDO。

2023-09-26 14:29:43 6753

6753

在本文中,我們將介紹低壓差 (LDO) 穩壓器中噪聲和電源抑制比 (PSRR) 的影響。讓我們簡單討論一下什么是 LDO。

2024-03-15 17:12:08 6801

6801

噪聲、接地干擾或其他外部干擾。共模抑制比是通過測量輸入共模信號與輸出共模信號之間的差異來確定設備抑制干擾信號的能力。共模抑制比不僅會對運放電路的精度產生影響,而且對

2024-06-04 08:10:46 6435

6435

LDO(LowDropoutRegulator)是嵌入式系統中廣泛使用的器件,也是最基本的模擬類電源,由于其輸出噪聲小,電路簡單,所以在各種應用中都是不可或缺的器件,其中有一些重要的參數對電路的性能

2025-02-05 17:03:15 10156

10156

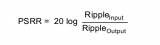

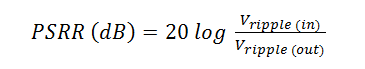

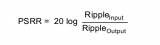

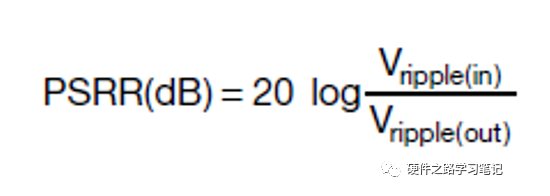

作者:Hao Wang深圳模擬工程師PSRR是什么PSRR(Power supply rejection ratio)又稱電源抑制比,是衡量電路對于輸入電源中紋波抑制大小的重要參數,表示為輸出紋波

2019-03-20 06:45:01

如圖,請問下LDO的紋波抑制比是否可以這樣測試,測試的LDO為3.3V輸出,規格書紋波抑制比40dB但實際上計算數差很多

2021-11-20 09:50:15

、LDO14005靜態電流低,僅8uA;14002靜態電流低,在2uA以下。電流驅動能力在150MA,全功率在0.6~0.8W,有過溫保護。

3、電源抑制比 70dB

4、同等條件下,瞬態響應比許多

2024-09-29 15:38:46

引言便攜產品電源設計需要系統級思維,在開發由電池供電的設備時,諸如手機、MP3、PDA、PMP、DSC等低功耗產品,如果電源系統設計不合理,將影響到整個系統的架構、產品的特性組合、元件的選擇、軟件

2019-07-05 06:22:55

1kHz的頻率下電源抑制比(PSRR)高達73dB,它能夠為諸如射頻(RF)接收器和發送器、壓控振蕩器(VCO)和音頻放大器等對噪聲敏感的模擬電路的供電提供低噪聲、電源紋波抑制比(PSRR)和快速瞬態響應

2019-07-25 06:15:03

高質量的D/A轉換器,要求開關電路及運算放大器所用的電源電壓發生變化時,對輸出的電壓影響極小.通常把滿量程電壓變化的百分烽與電源電壓變化的百分數之比稱為電源抑制比.電源抑制比可分為交流電源抑制比

2025-04-08 13:30:34

現在正做一個折疊式共源共柵放大器的設計,性能指標增益和電源抑制比不能同時達到要求,各位大神幫忙告訴我怎么提高電源抑制比?另外,抑制電路到底是什么啊?最好有圖呈現,謝謝了!

2016-05-27 13:52:28

1. 高的噪音和紋波抑制;2. 占用PCB板面積小,如手機等手持電子產品;3. 電路電源不允許使用電感器,如手機;4. 電源需要具有瞬時校準和輸出狀態自檢功能;5. 要求穩壓器低壓降,自身功耗低;6. 要求線路成本低和方案簡單;此時,選用LDO是最恰當的選擇,同時滿足產品設計的各種要求。二、再

2021-11-17 07:07:52

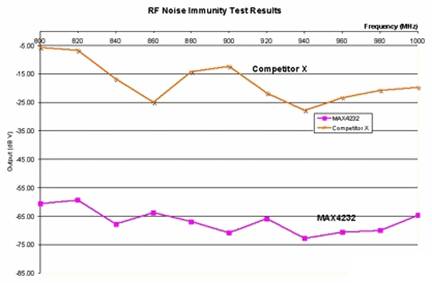

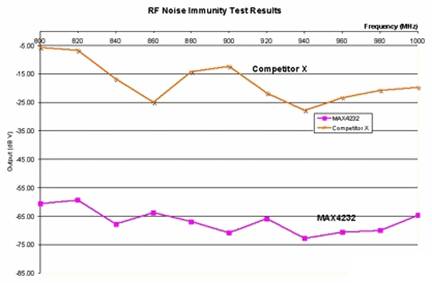

本文描述了一種通用的集成電路RF噪聲抑制能力測量技術。RF抑制能力測試將電路板置于可控制的RF信號電平下,該RF電平代表電路工作時可能受到的干擾強度。這樣就產生了一個標準化、結構化的測試方法

2019-07-04 06:21:39

用LDO給運放或者ADC供電,運放和ADC都有PSRR,而且在低頻端PSRR都高達80dB,LDO的內部噪聲剛好也是低頻的,按理說,運放和ADC的PSRR可以把LDO輸出的內部噪聲抑制的干干凈凈

2025-01-08 07:49:53

用LDO給運放或者ADC供電,運放和ADC都有PSRR,而且在低頻端PSRR都高達80dB,LDO的內部噪聲剛好也是低頻的,按理說,運放和ADC的PSRR可以把LDO輸出的內部噪聲抑制的干干凈凈

2024-09-03 07:32:36

什么是集成電路RF噪聲抑制能力測量技術?

2019-08-02 08:07:40

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2021-12-27 07:24:51

讀論文analysis of switched-capacitor commom-mode feedback circuit1.與單端輸出相比,全差分電路有更好的共模抑制比和電源抑制比。2.共模環路

2021-10-29 07:10:25

近期,項目遇到的問題,不得不考慮ldo的紋波抑制比問題,在選型時,確實沒有仔細研究,咨詢所選電源芯片的廠家后,才得知,自己選的這個芯片,紋波抑制不是很好。具體什么是紋波抑制比,腦子里倒是有,還是準確

2021-07-30 06:38:39

耐輻射低壓降穩壓器 (LDO) 是許多航天級子系統(包括現場可編程門陣列 (FPGA)、數據轉換器和模擬電路)的重要電源元件。LDO 有助于確保為性能取決于干凈輸入的元件提供穩定的低噪聲和低紋波電源

2022-11-03 08:23:55

1 kHz 的頻率下電源抑制比(PSRR)高達73dB,它能夠為諸如射頻(RF)接收器和發送器、壓控振蕩器(VCO)和音頻放大器等對噪聲敏感的模擬電路的供電提供低噪聲、電源紋波抑制比(PSRR)和快速

2019-06-19 06:43:54

。此紋波電壓一般沒有固定的頻率。閉環調節控制引起的紋波噪聲閉環調節控制引起的紋波噪聲的抑制 在開關直流電源中,往往因調節器參數選擇不適當會引起輸出紋波的增大,這部分紋波可通過以下方法進行抑制。a、在

2022-05-01 16:31:12

如何抑制電子電路中噪聲的產生低噪聲前置放大器電路的設計方法元件選擇原則PDA麥克風前置放大器電路

2021-02-25 07:06:39

電源波紋抑止比 (PSRR)、噪聲與封裝大小通常是為便攜式應用決定最佳 LDO 選擇的要素。

2021-03-25 07:20:44

接地電流或靜態電流 (IGND 或 IQ)、電源波紋抑止比 (PSRR)、噪聲與封裝大小通常是為便攜式應用決定最佳LDO選擇的要素。在選擇低壓降線性調節器(LDO) 時,需要考慮的基本問題包括

2021-01-28 17:09:01

能力的LDO的電源抑制比在100KHz以上都不太好開關電源如果選用類似LM2596這樣的芯片,看到紋波輸出大概在150KHz以上,求大神指點迷津,開關電源的紋波和噪聲可以抑制到什么程度呢?可不可以不用開關電源,直接用LDO來抑制適配器的噪聲呢?開關電源芯片有沒有開關頻率比較低的呢?

2014-04-22 22:30:52

影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

2024-09-09 07:32:22

什么是紋波抑制比PSRR?如何確定應用的紋波抑制比PSRR呢?怎樣去測量LDO芯片的紋波抑制比PSRR呢?

2021-11-03 06:48:15

選擇好的前端濾波器以加強帶外抑制。關于如何解決RF的電源干擾以及如何選用RF的LDO,首先必須確定RF電源已經被很好地濾波,其次有必要的話最好是不同的RF線路使用獨立的電源。在選用RF的LDO時要注意考慮它的驅動電流、輸出噪聲及紋波抑制等特性。

2019-07-08 08:26:47

(頻帶外的不必要輻射)為目的,介紹使用了片狀鐵氧體磁珠和片狀電感器的移動終端的PA電源線的噪聲對策方法。 通過有線連接的RF信號質量的評估項目中,有ACLR*1(臨道泄露功率比)和SEM*2(頻譜發射

2018-10-10 16:50:20

具有良好電源抑制比(PSRR)的ADC。當然,使您的系統性能免受其電源影響的最佳方法是選擇具有足夠PSRR的ADC來開始工作。如果您所選擇的ADC不能完全滿足您的PSRR需求,那么您可在自己原來

2022-11-18 07:31:30

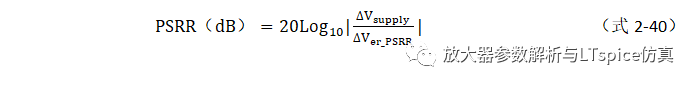

為 400KHz 的噪聲,折算到輸出端是幅值為 4mV 頻率為 400KHz 噪聲。圖 2.62 ADA4077 電源抑制比評估電路所以在開關電源供電精密電路中,依靠放大器自身提高電源抑制比的方式十分

2020-11-24 09:20:54

GSM手機的隨處可見正導致不需要的RF信號的持續增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導致電路產生的結果失真。為了確保電子電路可靠工作,對于電子電路RF抑制能力的測量已經成為

2019-07-31 06:26:15

削弱了穩壓器的噪聲抑制能力,不適合為敏感電路模塊供電。 為了保持良好的調節和噪聲抑制能力,LDO必須使用比它們輸入輸出電壓差規范中規定的更高的輸入電壓供電,這降低了轉換效率。為滿足輸入輸出電壓差

2018-09-26 14:33:58

LDO穩壓器的PSRR和輸出噪聲在RF電路中的選擇:LDO是一種微功耗的低壓差線性穩壓器,它具有極低的自有噪聲和較高的電源抑制比(PSRR)。SGM2007高性能低壓差線性穩壓器在10Hz至100kHz頻率

2009-09-25 08:19:27 19

19

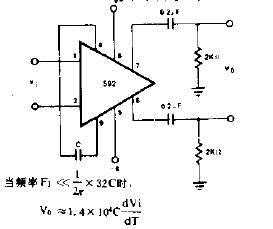

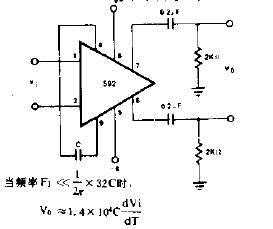

具有高共模噪聲抑制比的微分器電路圖

2009-04-03 08:40:07 703

703

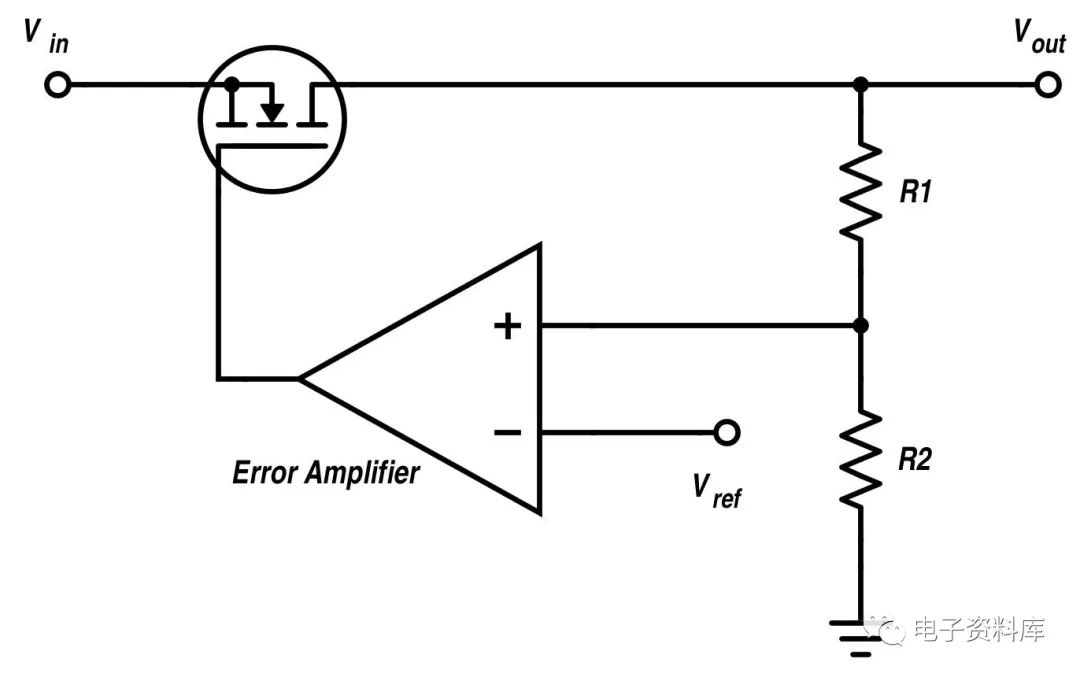

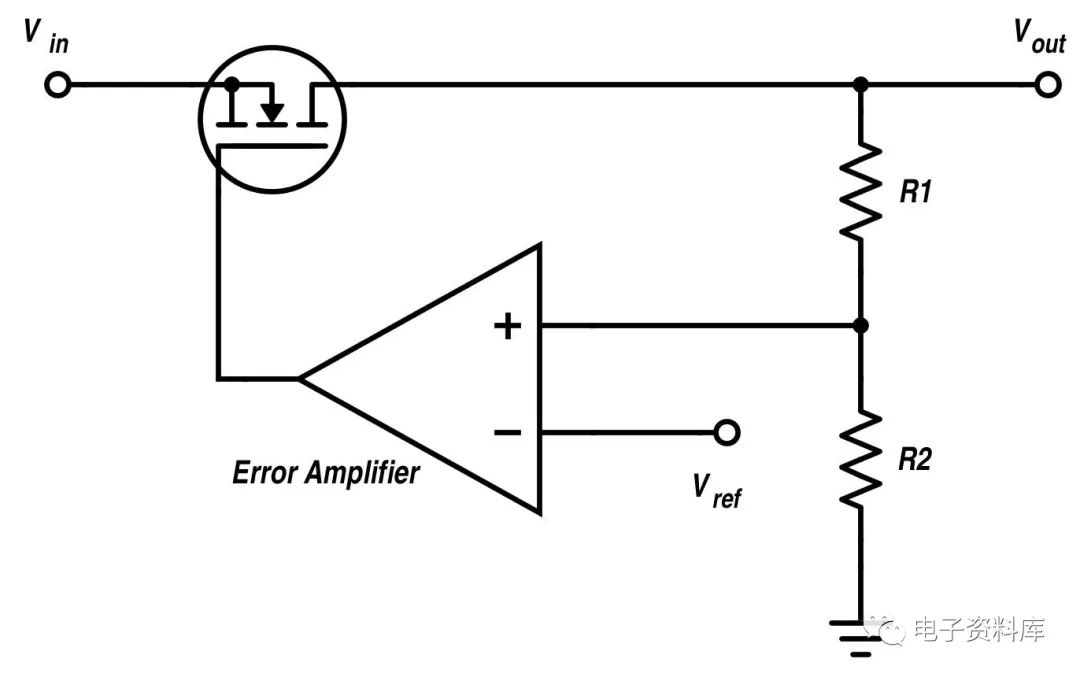

具有高電源抑制比性能的線性穩壓器

低壓降穩壓器(LDO)主要用于產生供音頻和射頻電路使用的低紋波、低噪聲電源,也可以作為頻率合成器和VCO的局部純凈電源。一般

2010-01-14 16:54:00 921

921

電源抑制比(PSRR),電源抑制比(PSRR)是什么意思

電源抑制比

電源抑制比(Power Supply Rejection Ratio):把電源的輸入與輸出看作獨

2010-03-09 16:41:06 16320

16320 RF電路中LDO電源抑制比和噪聲原理及選擇

本文討論LDO的特點以及RF電路對LDO的電源抑制比和噪聲的選擇。引言便攜產品電源設計需

2010-03-09 16:51:32 2972

2972

利用電波暗室測試電路的RF噪聲抑制

GSM手機的隨處可見正導致不需要的RF信號的持續增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導致電路產生的結果失真。為

2010-04-13 10:17:19 1245

1245

LDO是一種微功耗的低壓差線性穩壓器,它具有極低的自有噪聲和較高的電源抑制比(

2010-11-11 17:35:42 2449

2449

在實際應用電路時,噪聲及波動經常不知不覺會引入到供電電壓中,從而影響輸出端電壓。為使電路穩定,需消除或抑制所產生的噪聲。文中討論了3種改善放大器電路電源抑制比(PSRR)的

2011-08-29 11:05:48 14307

14307

由ISO124與MC78L05、MC79L05和DCP011515構成的外部調整器提高電源抑制比(PSR)的電路。利用MC78L05和MC79L05作為輔助穩壓調整,使得在不減小±10V輸入范圍條件下可以降低電源抑制比誤差。

2011-08-31 15:35:57 2232

2232

本文描述了一種通用的集成電路RF噪聲抑制能力測量技術。RF抑制能力測試將電路板置于可控制的RF信號電平下,該RF電平代表電路工作時可能受到的干擾強度。

2012-01-16 09:37:54 2001

2001

GSM手機的隨處可見正導致不需要的RF信號的持續增加,如果電子電路沒有足夠的RF抑制能力,這些RF信號會導致電路產生的結果失真。為了確保電子電路可靠工作,對于電子電路RF抑制能力的測量已經成為

2017-12-05 15:11:01 904

904

模塊對外部電源進行處理,得到模塊所需性能標準的電壓。 設計了一種可用于射頻前端芯片供電的高電源抑制比(PSR)無片外電容CMOS低壓差線性穩壓器(LDO)。基于對全頻段電源抑制比的詳細分析,提出了一種PSR增強電路模塊,使100

2018-02-23 11:41:48 0

0 供電,這意味著它不受外界影響,因此在輸入端沒有外部噪聲(雖然LDO在輸出端確實有內部噪聲)。外部噪聲是由外界影響(輸入處的紋波——實際源)產生的各種噪聲。輸入波紋與電源抑制比(PSRR)有關。此外,還有如熱和閃爍等噪聲的不同

2020-09-08 10:47:00 3

3 通常電源都會產生噪聲,那么怎么抑制電源噪音吶?電磁干擾濾波器也稱為EMI 濾波器,它對串模、共模干擾都起到抑制作用,能有效地抑制電網噪聲,提高電子設備的抗干擾能力及系統的可靠性,可廣泛用于電子測量儀器、計算機機房設備、開關電源、測控系統等領域。

2020-10-06 18:08:00 7424

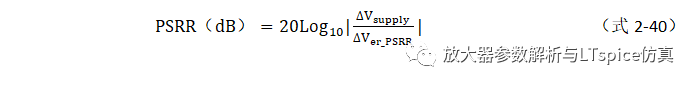

7424 放大器電源抑制比參數對電路的影響與共模抑制比參數的影響近似,因為來自電源線路的噪聲對于放大器而言可視為共模噪聲。本篇介紹放大器電源抑制比參數的評估方法,并通過LTspice仿真參數測量電路。 電源

2020-12-06 10:22:00 4963

4963 電源調制比與眾所周知的電源抑制比(PSRR)相似,但有一個關鍵不同點。PSRR衡量電源缺陷直接耦合到器件輸出的程度。PSMR衡量電源缺陷(紋波和噪聲)如何被調制到RF載波上。

2021-02-21 10:07:44 4783

4783

LT3094演示電路-超低噪聲、超高電源抑制比負LDO穩壓器(-20V至-3.3V@500 mA)

2021-03-23 14:27:09 28

28 ADM7155:600 mA,超低噪聲,高電源抑制比,RF線性穩壓器數據表

2021-04-19 19:48:03 3

3 ADM7154:600 mA,超低噪聲,高電源抑制比,RF線性穩壓器數據表

2021-04-19 20:05:36 0

0 和 PSRR 低壓差線性穩壓器 (LDO) 為調節由較高電壓輸入產生的輸出電壓提供了一種簡單方法。雖然操作簡單,但其自生噪聲在很多時候易與電源抑制比 (PSRR) 混淆。這兩者在很多情況下統稱為“噪聲”,這是不恰當的。噪聲是由LDO 內部電路中的晶體管和電阻器以及外部元件產生

2021-05-13 15:35:18 5082

5082

ADM7172:6.5 V,2 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-14 17:01:48 6

6 ADP7156:1.2 A,超低噪聲,高電源抑制比,RF線性穩壓器數據表

2021-05-17 16:32:35 3

3 ADP7157:1.2 A,超低噪聲,高電源抑制比,RF線性穩壓器數據表

2021-05-17 16:58:49 0

0 ADP7158:2 A,超低噪聲,高電源抑制比,RF線性穩壓器數據表

2021-05-17 18:01:40 1

1 ADM7170:6.5 V,500 mA,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-21 19:19:34 7

7 ADM7171:6.5 V,1 A,超低噪聲,高電源抑制比,快速瞬態響應CMOS LDO數據表

2021-05-21 19:33:05 12

12 LT3045演示電路-低噪聲、高電源抑制比RF線性穩壓器(3.8-20V至3.3V@500 mA)

2021-06-02 16:16:21 41

41 LT3042演示電路-低噪聲、高電源抑制比RF線性穩壓器(3.8-20V至3.3V@200 mA)

2021-06-03 10:50:23 3

3 共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejection-ratio)是運放性能的重要指標,關于他們的具體仿真

2022-01-05 14:22:58 6

6 LDO基礎知識:電源抑制比

2022-11-01 08:26:41 2

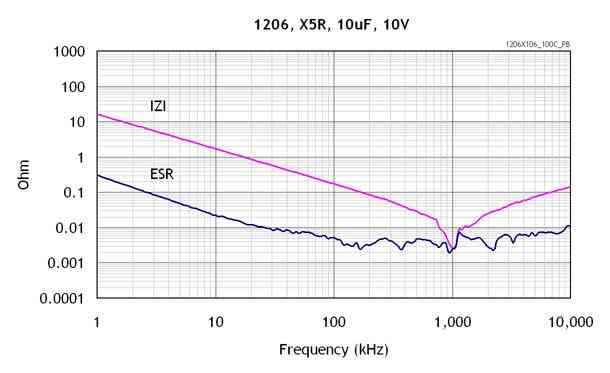

2 電源上的噪聲通常會傳播到輸出端,并且通常是不需要的,特別是在精密測量和RF通信等敏感應用中。線性穩壓器 (LDO) 根據其電源抑制比 (PSRR) 抑制交流噪聲。PSRR是噪聲頻率和輸入至輸出電壓差

2022-12-23 10:12:28 2443

2443

放大器電源抑制比參數對電路的影響與共模抑制比參數的影響近似,因為來自電源線路的噪聲對于放大器而言可視為共模噪聲。本篇介紹放大器電源抑制比參數的評估方法,并通過LTspice仿真參數測量電路。

2023-02-22 14:20:44 3679

3679

在便攜式通信中,低壓差線性穩壓器(LDO)為RF電路產生電源電壓;為頻率合成器和壓控振蕩器(VCO)供電時,這些電壓必須特別干凈。為穩壓器供電的電源通常包括疊加在直流上的寬帶交流紋波。預計LDO會抑制這些偽影。本文介紹了三種提高LDO電源抑制比(PSRR)的方法。

2023-03-13 09:32:37 2242

2242

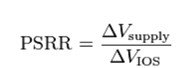

電源抑制比的概念,接觸過運放的讀者應該知道,指的是運放對電源噪聲或者紋波的抑制能力,噪聲和紋波是交流的,所以運放的電源抑制比一般指的是AC PSRR。但是什么又是運放的直流電源抑制比(DC_PSRR)呢?是指運放供電電壓的變化,引起運放輸入失調電壓的變化,這兩個變化之比就是運放的直流電源抑制比。

2023-03-17 15:52:46 3347

3347

低壓差線性穩壓器(LDO)最大的優點之一是它們能夠衰減開關模式電源產生的電壓紋波。這對鎖相環(PLL)和時鐘等信號調節器件在內的數據轉換器尤為重要,因為噪聲電源電壓會影響性能。電源抑制比(PSRR)仍然通常被誤認為單一的靜態值。在這篇文章中,我將嘗試說明什么是PSRR以及影響它的變量有哪些。

2023-04-04 10:25:33 2418

2418

電源抑制比又叫做電源紋波抑制比(power supply rejection ratio)簡稱PSRR。不少電源芯片手冊中有此參數,比如LDO芯片,很多人在閱讀LDO手冊的時候忽略了此參數,其實這個

2023-04-24 12:57:43 10572

10572

在便攜式通信中,低壓差線性穩壓器(LDO)為RF電路產生電源電壓;為頻率合成器和壓控振蕩器(VCO)供電時,這些電壓必須特別干凈。為穩壓器供電的電源通常包括疊加在直流上的寬帶交流紋波。預計LDO會抑制這些偽影。本文介紹了三種提高LDO電源抑制比(PSRR)的方法。

2023-06-10 11:38:35 2954

2954

LDO的電源抑制比基本概念與應用

2023-07-24 16:15:14 3021

3021

電源抑制比是什么意思?電源抑制比怎么提高? 一、電源抑制比的概念 電源抑制比(PSRR)又稱電源噪聲抑制比,是指在電路中,當電源發生噪聲時,電路輸出端對電源噪聲的抑制程度,一般使用分貝(dB)單位

2023-09-02 17:50:32 9857

9857 什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和電源抑制比(power supply rejection

2023-10-29 11:45:48 10810

10810 電源抑制比怎么提高? 電源抑制比是衡量電源噪聲抑制效果的重要指標。提高電源抑制比可以有效降低電源噪聲對電子設備的影響,提升設備的穩定性和性能。本文將從信號處理、濾波器設計、抑制電路、電源線布局等多個

2023-12-12 14:33:28 1552

1552 電子發燒友網站提供《超低噪聲、高電源抑制比 (PSRR)、快速、射頻 (RF)、1A 低壓差線性穩壓器數據表.pdf》資料免費下載

2024-02-28 15:14:45 0

0 在電子設備和系統的設計中,電源抑制比(Power Supply Rejection Ratio,簡稱PSRR)是一個至關重要的參數。它描述了電子設備或系統對來自電源的噪聲和干擾的抑制能力。本文將詳細探討電源抑制比的概念、計算方法、作用及其在電子設備設計中的應用,以期為讀者提供全面的理解和深入的見解。

2024-05-24 14:31:29 8067

8067 LDO電源抑制比(PSRR,Power Supply Rejection Ratio)是衡量線性穩壓器(LDO)在電源電壓變化時對輸出電壓穩定性的影響的一個重要指標。 一、LDO電源抑制比的概念

2024-07-14 10:14:09 2436

2436 電源抑制(Power Supply Rejection)能力是SoC系統中電源模塊很重要的指標,在當今數字和模擬電路高度集成的趨勢下,一個能提供穩定輸出電壓的系統模塊顯得尤為重要,而這個模塊又很容易受到供電電源的噪聲和紋波影響,電源抑制能力描述的就是對這一類影響的抑制能力。

2024-11-09 17:30:39 2178

2178 的應用及其常見故障和解決方法的概述。 應用場景 電源轉換 :LDO可以將電池電壓或其他電源電壓轉換為嵌入式系統所需的穩定電壓。 噪聲抑制 :LDO能有效降低電源線上的噪聲,為敏感的模擬電路提供干凈的電源。 功耗管理 :在低功耗應用中,LDO可以提供穩定的電源,同時減少功耗

2024-12-13 09:08:51 3244

3244 :負載調整率是指當負載電流變化時輸出電壓的變化量,需要根據應用選擇合適的負載調整率。 電源抑制比(PSRR) :PSRR是衡量LDO抑制輸入電源噪聲能力的重要參數,對于需要高PSRR的應用,如模擬信號處理,尤為重要。 靜態電流(Iq) :靜態電流是LDO在

2024-12-13 09:10:16 1560

1560 高精度、低輸出電壓 :立锜工業用 LDO 系列支持 1.1V 至 6.5V 輸入范圍,單一輸入,無需額外電源,可簡化設計。部分產品的輸出電壓低至 0.5V,并具備 1% 高精度。 2. 優異的噪聲抑制能力 :具有高 PSRR(電源紋波抑制比),在 500kHz 頻率下可達 40dB,并具備

2025-05-08 17:03:34 765

765

在電子技術日新月異的今天,電源抑制比(PowerSupplyRejectionRatio,簡稱PSRR)宛如一把精準的標尺,衡量著電子電路對電源噪聲和電壓波動的抑制能力。PSRR以分貝(dB)為

2025-06-06 17:22:02 514

514

電子發燒友App

電子發燒友App

評論