引言

當今社會是數字化的社會,隨著微電子技術的發展,設計與制造集成電路的任務已不完全由半導體廠商來獨立承擔,設計師們更希望在教研室里就能驗證所設計的電路功能。FPGA的出現,使得芯片設計和應用跨入了一個新的領域。

研究背景

隨著硬件方面的急速發展,與之相配套的軟件也不斷更新,更快﹑更智能的原理圖編輯﹑設計實現和驗證工具都被集成到EDA開發工具中。這些發展大大縮短了FPGA的開發周期,增強了FPGA設計的靈活性和可移植性,也避免了專用集成電路設計的高風險。但由于片內存儲器受器件規模和生產成本的制約,其容量通常不能滿足用戶實際需求,這就需要使用半導體存儲器件來擴展存儲空間。針對這種情況,本文專門研究了FPGA與兩種典型的存儲器接口實現問題。在設計實現中采用了Xilinx公司Virtex-E系列的FPGA (XCV300E)﹑ISSI公司的高速靜態存儲器IS63LV1024和HYNIX公司的HY57V281620HC(L/S)T動態存儲器。

XCV300E性能介紹

FPGA(現場可編程門陣列)是可編程邏輯器件的一種,它不僅可以提高系統的可靠性,使得系統結構更加緊湊,節省了電路板的面積,而且實現成本低﹑開發周期短,是進行原始設計的理想載體。Virtex-E系列產品對所有Virtex特性都進行了加強,采用領先的0.18 m六層金屬互連半導體工藝制造,大大提高了器件性能和密度,同時還提供了可進一步滿足下一代數據通信和DSP應用帶寬要求的高性能系統特性組合。Xilinx公司的VirtexE XCV300E,采用BGA432封裝,片內Block RAM為131,072 比特,Distributed RAM為98,304比特,System Gates為411,955門,Logic Gates為82,944門。特性如下:

1.工作在1.8V電壓下的快速﹑高密度FPGA器件 ;

2.采用高度靈活的I/O選擇技術,支持20種高性能接口標準;

3.采用高性能的鏈路選擇技術;

4.精密復雜的存儲器選擇機制;

5.高性能的時鐘管理電路;

6.具有能平衡速度與密度的靈活性體系結構;

7.基于SRAM方式的系統配置。

SRAM性能介紹

為了能更好﹑更有效的設計FPGA與IS63LV1024的接口實現,必須先了解IS63LV1024的性能特點。充分利用這些特點會使設計的實現變得事半功倍。IS63LV1024是128K 8的高速靜態存儲器,性能特點包括:

1.工作在3.3V電壓下,高速接入時間一般分為8、10、12和15ns;

2.高性能﹑低功耗器件(使用ICSI高性能COMS技術制作過程和使用新的電路設計技術);

3.通過選擇CE和OE的狀態可以比較簡單的實現存儲;

4. CE可以使器件進入power-down工作模式,即 沒有被選擇時,器件進入一種掛起狀態,使得功率消耗小于250 W;

5.不需要時鐘和更新,是全靜態工作過程;

6.所有的輸入和輸出都是與TTL相兼容的。

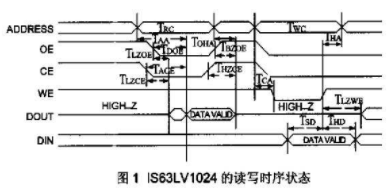

除此之外,為了保證所傳輸的數據的正確性還必須要了解IS63LV1024的讀寫狀態的時序和使能的要求。其讀寫時序狀態如圖1所示:

DRAM性能簡介

DRAM與SRAM不同,它只能將數據保持很短的時間。為了保持數據,DRAM 必須隔一段時間刷新一次,如果存儲單元沒有刷新,數據就會丟失。SRAM雖不需刷新,但斷電后會丟失數據。SRAM的數據傳輸速率從10 ns到30 ns不等,DRAM要比它慢30 ns左右。因此,SRAM通常用于高速緩沖存儲器,而DRAM通常用來存儲較大的數據。HY57V281620HC(L/S)T是4Banks 2M 16bit的同步動態存儲器,性能特點包括:

1.工作在3.3 0.3V電壓下;

2.所有器件管腳都與LVTTL接口兼容;

3.所有的輸入和輸出操作都是在時鐘CLK上升沿的作用下進行;

4.通過UDQM或者LDQM來實現數據延時功能;

5.內部有四個bank可以進行操作;

6.自刷新功能,刷新周期為4096;

7.可編程的猝發類型、猝發長度;

8.可編程的的CAS延遲為2或3個時鐘周期。

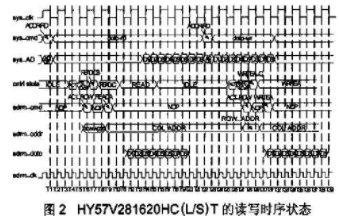

由上面的特性可知,DARM的讀寫操作與SRAM有較大的不同。根據HY57V281620HC(L/S)T的讀寫狀態的時序要求,其讀寫時序狀態如圖2所示:

設計實現

當設計FPGA與SRAM的接口時,由于它的傳輸速度較快,所以只需著重考慮如何保證存儲數據的正確性,而不需要考慮用其它方式來提高SRAM的存儲速度。本設計的做法是一次性寫滿128k數據后,再一次性讀出128k數據。為了保證數據的正確性,要求在寫數據時不能讀數據,而在讀數據時不能寫數據。

當設計FPGA與DRAM的接口時,為了能滿足各種系統的使用要求,本設計創建了時鐘頻率、猝發長度、延時節拍等可編程參數。在具體操作DRAM時,首先,必須進行初始化配置,即寫模式寄存器,以便確定DRAM列選延遲節拍數、猝發類型、猝發長度等工作模式。然后通過ACT命令激活對應地址的組,同時輸入行地址。最后,通過RD或WR命令輸入列地址,將相應數據讀出或寫入到對應的地址。操作完成后,用相關命令中止讀或寫操作。在沒有操作的時候,每64ms必須對所有存儲單元刷新一遍,防止數據丟失。

下面本文將指出在設計實現中需要特別注意的幾個問題,并給出了相應的解決方法 。

首先,是如何控制SRAM的讀寫功能。這就需要與IS63LV1024讀寫時序要求和真值表的描述相配合。本設計為了避免連讀或連寫數據時出錯,考慮了一種通過讀寫數據請求的方法來盡量避免讀或寫數據出錯的可能。即每寫完或讀完一個數據后都要先進行請求,然后才能繼續讀或寫數據。ASRAM的狀態轉移圖如圖3所示:

下面給出了圖3中各個狀態所表示的意思:

DOREAD表示讀數據的請求;

DOWRITE表示寫數據的請求;

STIDLE表示存儲器處于空閑狀態;

STWRITE1表示存儲器處于寫準備狀態,準備寫數據;

STWRITE2表示存儲器處于寫狀態,開始寫數據;

STREAD1表示存儲器處于讀準備狀態,準備讀數據;

STREAD2表示存儲器處于讀狀態,開始讀數據。

只有當系統時鐘的上升沿到來時,才會觸發這個狀態機改變一次當前狀態。

剛開始時,存儲器的初始狀態為空閑狀態,當有請求來時才判斷是讀或寫請求,如果沒有請求就一直保持空閑狀態。虛線表示自動按順序進入下一個狀態。

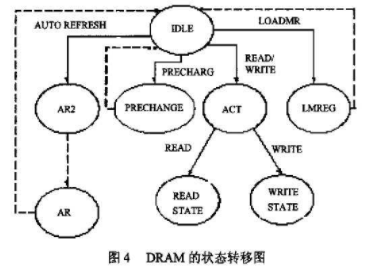

其次,是如何控制DRAM的各種狀態。當設計FPGA與DRAM的接口時,由于它除了讀寫狀態外還有較多的其它狀態,所以需要著重設計好讀寫狀態與其它狀態之間的轉換控制。為了解決這個問題,本設計采用了狀態機來控制這些狀態之間的關系,DRAM的狀態轉移圖如圖4所示:

下面給出了圖中各個狀態所表示的意思:

IDLE 表示存儲器處于空閑狀態;

LMREG 表示加載寄存器狀態;

ACT 表示活動狀態;

AR2 表示自動刷新有效狀態;

AR 表示自動刷新無效狀態;

WRITE STATE 表示讀狀態;

READ STATE 表示寫狀態;

只有當系統時鐘的上升延到來時,才會觸發這個狀態機改變一次當前狀態。

剛開始時,存儲器的初始狀態為空閑狀態,當有請求來時才會進入下一個狀態,如果沒有請求就一直保持空閑狀態。虛線表示自動按順序進入下一個狀態。

最后,是FPGA的設計要求。一個優秀的FPGA設計不僅要達到系統的基本要求,同時必須滿足可讀性、可重復性和可測性。

可讀性好的FPGA設計原理圖和硬件描述語言設計應該包含足夠詳細的注釋。每張原理圖之間的關系及硬件描述模塊間的互聯關系的說明固然重要,但是每個模塊本身的說明也是不能忽視的,例如狀態機的文檔應當包括狀態圖或功能描述。好的文檔也許花不了很多的時間,但是卻可以在調試﹑測試和維護設計上節省大量的時間。

可重復性指FPGA設計應該保證如果不同的人從不同的部位開始,并重新進行布局布線等,應該得到同樣的結果。沒有這個保證,驗證以及其他形式的設計測試就毫無意義。設計者顯然不希望在設計里出現這樣的情況,具有相同的輸入輸出管腳和功能的器件,由于布局布線的差異,導致最后時序不一致。如果在實現的過程中,系統設計軟件的參數或選項不一致,就會發生這種情況。因此FPGA的文檔就應該包括必要的信息,即軟件開發系統的版本號﹑軟件的各個選項及參數設計。

可測性是FPGA設計的最后一個特征。系統級的測試要求設計者對整個設計流程及系統架構都要很清楚。隨著設計層次的提高,使得設計者面對的電路規模越來越大,功能越來越復雜,相應電路的測試也變得越來越困難。在設計過程中綜合考慮測試的設計問題并統一實施,將有效地縮短整個產品的開發時間、減少返工。

結束語

在開發過程中由于采用高級硬件編程語言-編程器件的設計實現過程,大大縮短了開發周期,增加了硬件設計的靈活性和可移植性,也避免了專用集成電路設計的高風險。采用邏輯仿真與后時序仿真相結合的驗證方法,可以保證設計的可靠性。基于上述優點,這種開發方式在中小型集成電路開發中已得到廣泛應用。 隨著工藝技術的發展與市場的需要,超大規模﹑高速﹑低功耗的新型FPGA將會不斷推陳出新。現在新一代的FPGA甚至集成了中央處理器(CPU)或數字處理器(DSP)內核,在一片FPGA上進行軟硬件協同設計,為實現片上可編程系統(SOPC,System On Programmable Chip)提供了強大的硬件支持。

責任編輯:gt

電子發燒友App

電子發燒友App

評論