作者:Jacob Beningo 很多嵌入式設(shè)計使用基于微處理器和微控制器的單板計算機 (SBC) 和模塊化系統(tǒng) (SoM)(例如,請參閱“使用 Raspberry Pi 3構(gòu)建低成本工業(yè)控制器

2023-10-03 14:20:00 1838

1838

8051的微處理器由哪幾部分構(gòu)成?8051微處理器具有哪些引腳功能?

2022-01-18 07:26:58

FPGA上對OC8051IP核的修改與測試FPGA上對OC8051IP核的修改與測試單片機與嵌入式系統(tǒng) 解放軍信息工程大學(xué) 楊先文 李崢引 言20世紀80年代初,Intel公司推出了MCS-51

2012-08-11 11:41:47

FPGA嵌入8051單片機 IP核編程,編寫的c語言矩陣鍵盤程序可以在stc89c54單片機上正常工作,但是下載到FPGA中8051單片機ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

可編程邏輯業(yè)對微處理器核的報道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標準還是行業(yè)標準?這些核如何用來全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來選擇微處理器?如何根據(jù)應(yīng)用來選擇核?

2019-08-08 06:43:03

設(shè)計RISC微處理器需要遵循哪些原則?基于FPGA技術(shù)用VHDL語言實現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

大家在移植UIP協(xié)議棧的時候 有沒有遇到UIP協(xié)議棧源代碼的[C] 純文本查看 復(fù)制代碼uip_arp.h文件中 extern struct uip_eth_addr uip

2020-04-02 01:40:13

UIP和lwip有什么區(qū)別,uIP是專門為8位和16位控制器設(shè)計的一個非常小的TCP/IP棧。完全用C編寫,因此可移植到各種不同的結(jié)構(gòu)和操作系統(tǒng)上,一個編譯過的棧可以在幾KB ROM或幾百字節(jié)RAM

2021-08-09 09:09:45

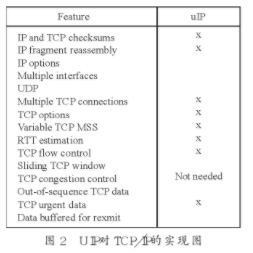

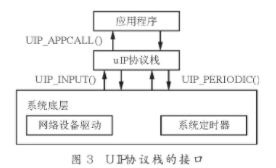

是將JavaScript程序內(nèi)嵌在網(wǎng)頁中,不需要在瀏覽器上另外安裝插件,降低了系統(tǒng)成本和Web服務(wù)器實現(xiàn)的難度。1 uIP協(xié)議棧分析uIP是專為8/16位嵌入式微處理器設(shè)計的輕量級TCP/IP協(xié)議棧

2019-05-28 05:00:04

基于FPGA的嵌入式系統(tǒng)的開發(fā)工具包。本文介紹基于SoPC的波形發(fā)生器在EDK工具包下的設(shè)計與實現(xiàn)。本設(shè)計采用嵌入式軟處理器核 MicroBlaze以及自主編寫的包括實現(xiàn)DDS在內(nèi)的多種IP Core

2009-06-25 08:12:37

嵌入式產(chǎn)品的生產(chǎn)商總是期待能使自己的產(chǎn)品成本更低、更快地走向市場的微處理器解決方案。高性價比、高集成度、高度靈活的微處理器能幫助終端產(chǎn)品在性能、價格競爭日益激烈的市場環(huán)境中脫穎而出。

2019-09-27 06:51:10

微處理器必須具備足夠的能力來保障產(chǎn)品的性能,并能支持產(chǎn)品的生存周期。嵌入式微處理器的品種非常多,針對不同的應(yīng)用領(lǐng)域有不同的芯片類型。而且很多芯片是SoC芯片,芯片上除集成微處理器核外,還集成有LCD控制器

2020-05-20 11:11:35

隨著嵌入式系統(tǒng)在消費電子和工業(yè)設(shè)備中的廣泛應(yīng)用,功耗已經(jīng)開始像時鐘速度和系統(tǒng)性能一樣成為微處理器的一個核心特性。為了確定各種微處理器的功耗效率,嵌入式微處理器基準協(xié)會開發(fā)了一個有力的工具

2019-08-22 07:30:54

ARM開發(fā)教程之基于ARM微處理器TCPIP協(xié)議棧LwlP實現(xiàn)

2012-08-24 22:42:21

,國際上只有I-Shou大學(xué)的Yu-Jung Huang等人設(shè)計了可驅(qū)動不同規(guī)模LCD的驅(qū)動電路IP核,通過在系統(tǒng)中植入嵌入式微處理器來實現(xiàn)這一功能。但是,這種嵌入式微處理器使系統(tǒng)更復(fù)雜,而且成本更高

2012-08-12 12:28:42

TCP服務(wù)器端通信為例,分析三種方法以及之間的關(guān)系,著重介紹基于raw API的應(yīng)用程序設(shè)計。最后在ST公司STM32F107微處理器平臺上驗證,并給出了測試結(jié)果。關(guān)鍵詞 LwIP協(xié)議棧...

2021-08-06 07:33:33

的老版本的源碼中串口部分有問題,最新的1.6版本則已經(jīng)修正了這個問題,因此強烈建議使用我們提供的源碼。 本移植結(jié)果已經(jīng)在芯航線FPGA學(xué)習(xí)套件的核心板上完全驗證通過。如有任何疑問,歡迎加入芯航線FPGA學(xué)習(xí)支持群(472607506)進行討論。mc8051_test.rar (7.48 MB )

2019-05-24 04:35:33

)作為一種特殊的嵌入式微處理器系統(tǒng),已逐漸成為一個新興的技術(shù)方向。SOPC融合了SoC和FPGA各自的優(yōu)點,并具備軟硬件在系統(tǒng)可編程、可裁減、可擴充、可升級的功能。其核心是在FPGA上實現(xiàn)的嵌入式微處理器

2020-03-16 06:37:20

實現(xiàn),于是2001年Altera第一次提出了可編程片上系統(tǒng)(SOPC)概念,并且推出了第一款嵌入式處理器軟核Nios以及之后的第二代Nios II以及相應(yīng)的開發(fā)環(huán)境,此后Xilinx也推出

2020-03-09 06:50:07

項目名稱:FPGA上的處理器核原型設(shè)計試用計劃:申請理由及項目計劃:本人西安某高校學(xué)生,對數(shù)字IC感興趣,學(xué)習(xí)過FPGA與處理器相關(guān)知識,用過quartus和vivado,ISE,看過水頭一壽

2017-07-25 18:02:36

報文協(xié)議和TCP傳輸控制協(xié)議。為了在8位16位處理器上應(yīng)用,uIP協(xié)議棧在各層協(xié)議實現(xiàn)時采用有針對性的方法,保持代碼大小和存儲器使用量最小。 1 實現(xiàn)ARP地址解析協(xié)議時為了節(jié)省存儲器,ARP應(yīng)答包

2011-08-08 09:27:36

可編程邏輯業(yè)對微處理器核的報道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標準還是行業(yè)標準?這些核如何用來全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來選擇微處理器?如何根據(jù)應(yīng)用來選擇核?

2019-08-13 07:52:46

基于FPGA的IP核8051上實現(xiàn)TCPIP的設(shè)計

2012-08-06 12:18:28

的RISC CPU設(shè)計是一個從抽象到具體的過程,本文根據(jù)FPGA的結(jié)構(gòu)特點,圍繞在FPGA上設(shè)計實現(xiàn)八位微處理器軟核設(shè)計方法進行探討,研究了片上系統(tǒng)的設(shè)計方法和設(shè)計復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出

2021-07-11 08:00:01

兩個方面的內(nèi)容:IP核生成和IP核復(fù)用。文中采用IP核復(fù)用方法和SOC技術(shù)基于AVR 8位微處理器AT90S1200IP Core設(shè)計專用PLC微處理器FSPLCSOC模塊。

2019-07-26 06:19:34

/ IP協(xié)議棧的嵌入式以太網(wǎng)終端的設(shè)計方案。該方案給出了ARM內(nèi)核的微處理器S3C44B0X和以太網(wǎng)控制器芯片RTL8019AS的接口電路以及嵌入式TCP / IP棧和μC/OS - Ⅱ?qū)崟r操作系統(tǒng)

2008-06-27 09:33:13

基于μC/OS—II的μC/IP協(xié)議棧在ARM系統(tǒng)中的實現(xiàn)深入分析了UC/IP協(xié)議棧,闡述了其移植原理和實現(xiàn)方案,并給出了在具體軟硬件平臺上的移植實例。首先,通過分析UC/IP協(xié)議棧,結(jié)合實時內(nèi)核

2009-03-28 14:04:52

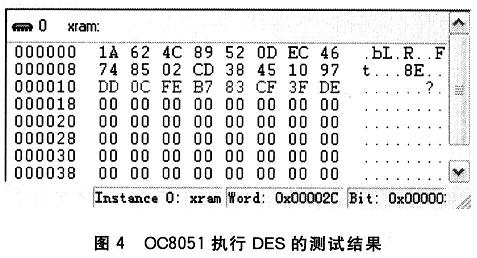

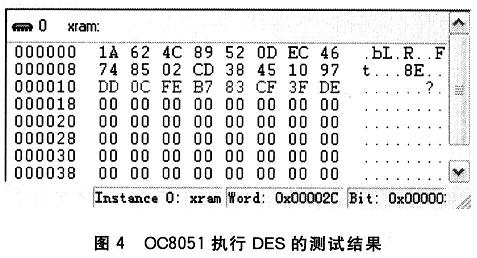

本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

本文闡述在一種異構(gòu)網(wǎng)絡(luò)互聯(lián)——CAN總線與以太網(wǎng)互聯(lián)系統(tǒng)設(shè)計方案中嵌入式TCP/IP協(xié)議棧的設(shè)計與實現(xiàn)。從而實現(xiàn)了將基于TCP/IP協(xié)議的計算機網(wǎng)絡(luò)設(shè)備與基于CAN總線協(xié)議的底層現(xiàn)場網(wǎng)絡(luò)連通。

2021-06-07 06:28:25

本文采用了在嵌入式實時操作系統(tǒng)uC/OS-II中移植一種小型TCP/IP協(xié)議棧uIP的方法,使基于8051嵌入式系統(tǒng)的GPRS終端能夠在網(wǎng)絡(luò)中進行數(shù)據(jù)傳輸;同時改善了系統(tǒng)的性能,提高了系統(tǒng)的可靠性,增強了系統(tǒng)的可擴展性和產(chǎn)品開發(fā)的可延續(xù)性。

2021-05-26 06:41:59

怎么才能在嵌入FPGA的IP核8051上實現(xiàn)TCP/IP的設(shè)計?

2021-04-29 06:51:27

的其它設(shè)計部分盡量不相關(guān)。為了滿足上述的要求, 在FPGA中嵌入一個比較理想的選擇, 而這個即通用又控制簡單的IP核最好選擇8051微處理器。

2019-08-26 06:27:15

一個以上的嵌入式處理器IP(Intellectual Property,知識產(chǎn)權(quán))核,具有小容量片內(nèi)高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA

2020-03-13 07:03:54

本文根據(jù)FPGA的結(jié)構(gòu)特點,圍繞在FPGA上設(shè)計實現(xiàn)八位微處理器軟核設(shè)計方法進行探討,研究了片上系統(tǒng)的設(shè)計方法和設(shè)計復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出了一種基于FPGA的微處理器的IP的設(shè)計方法。

2021-04-29 06:38:37

與GPRSmodem的連接,即數(shù)據(jù)端的串行數(shù)據(jù)經(jīng)ARM CPU的串口發(fā)送到GPRSmodem上;二是在ARM CPU中嵌入實時操作系統(tǒng)uC/OS-II,然后在uC/OS-II中移植uIP,實現(xiàn)TCP/IP協(xié)議棧。圖

2008-08-07 06:48:35

想請教各位大神們。嵌入式系統(tǒng)實現(xiàn)以太網(wǎng)(比如stm32),TCP/IP協(xié)議棧是不是都是移植的。比如都移植LWIP。UIP等。而不是自己寫啊…………感謝……

2020-03-13 02:22:48

片上Nios Ⅱ嵌入式軟核多處理器系統(tǒng)具有哪些優(yōu)勢?如何實現(xiàn)片上嵌入式Nios Ⅱ軟核六處理器系統(tǒng)的設(shè)計?

2021-04-19 08:17:09

包含一個以上的嵌入式處理器IP(Intellectual Property,知識產(chǎn)權(quán))核,具有小容量片內(nèi)高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA編程接口共用或并存,可能包含部分可編程模擬電路,單芯片、低功耗[1]。

2019-08-23 08:18:51

在介紹IEEE802.11MAC 協(xié)議結(jié)構(gòu)的基礎(chǔ)上,給出協(xié)議開發(fā)的方法和步驟,提出IEEE802.11MAC 協(xié)議在32 位ARM7TDMI 微處理器S3C4510B 上的一種移植方案,開發(fā)出了嵌入式IEEE802.11MAC 協(xié)議的IP核。同時

2009-05-16 14:23:46 10

10 實現(xiàn)一個運行在16 位數(shù)字信號處理器TMS320VC5402 上的小型嵌入式TCP/IP 協(xié)議棧。對TCP/IP 協(xié)議中的IP 協(xié)議、ARP 協(xié)議、UDP 協(xié)議進行分析, 完成基于TCP/IP 協(xié)議的嵌入式網(wǎng)絡(luò)系統(tǒng)。

2009-05-16 14:55:25 28

28 uIP 協(xié)議棧是一種免費的可實現(xiàn)的極小的TCP/IP協(xié)議棧,可以使用于由8位或16位微處理器構(gòu)建的嵌入式系統(tǒng)。本文分析了uIP協(xié)議棧的結(jié)構(gòu)和應(yīng)用接口,并討論了如何將其應(yīng)用到51系列單

2009-08-19 08:48:01 53

53 基于FPGA 的嵌入式ASIP 軟核設(shè)計與實現(xiàn)作者:李慶誠 任健 劉嘉欣 黃寶貞 來源:微計算機信息摘要:采用ASIP+FPGA 模式設(shè)計了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和

2010-02-06 10:44:40 30

30 采用ASIP+FPGA模式設(shè)計了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和指令集設(shè)計兩方面對ASIP+FPGA模式微處理器軟核的設(shè)計進行了分析和驗證,最后通過與傳統(tǒng)微處理器對比

2010-07-28 17:41:46 17

17 提出了一種采用基于NiosII處理器的通用AD IP核來實現(xiàn)嵌入式數(shù)據(jù)采集系統(tǒng)的新方案。它能將市面上任意一款A(yù)D芯片制作成IP核并集成到NiosII系統(tǒng)中使用,且整個IP核的控制與運算邏輯由

2010-07-30 11:39:16 50

50 摘要:介紹了基于GPRS網(wǎng)的數(shù)據(jù)傳輸、嵌入式實時操作系統(tǒng)u/OS-II以及小型TCP/IP協(xié)議棧uIP;深入論述了基于8051嵌入式系統(tǒng)的GPRS終端的實現(xiàn)。提供了一種羅為

2006-03-11 13:34:00 842

842

BIST在SoC片上嵌入式微處理器核上的應(yīng)用

引 言

隨著科技的不斷發(fā)展,集成電路的制造工藝和設(shè)計水平得到了飛速提高,設(shè)計者能夠?qū)⒎浅?fù)雜的功能集成到

2009-11-07 11:18:03 1950

1950

基于ARM微處理器TCP IP協(xié)議棧LwlP實現(xiàn)

0 引 言 隨著嵌入式系統(tǒng)與網(wǎng)絡(luò)的日益結(jié)合,越來越多的嵌入式設(shè)備需要實現(xiàn)Internet網(wǎng)絡(luò)化,支持嵌入式設(shè)備接入網(wǎng)

2009-12-19 10:01:19 1550

1550 在FPGA上對OC8051IP核的修改與測試

引 言

20世紀80年代初,Intel公司推出了MCS-51單片機,隨后Intel以專利轉(zhuǎn)讓的形式把8051內(nèi)核發(fā)布給許多半導(dǎo)體廠家,從而出

2010-01-07 11:23:57 1892

1892

FPGA中的處理器IP概述

可編程邏輯業(yè)對微處理器核的報道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒什么改變,諸如采用硬

2010-03-10 10:38:14 1160

1160

基于IP復(fù)用設(shè)計的微處理器FSPLCSOC模塊

1 引言

文中采用IP核復(fù)用方法和SOC技術(shù)基于AVR 8位微處理器AT90S1200IP Core設(shè)計專用PLC微處理器FSPLCSOC模塊。

隨

2010-05-17 08:41:09 2002

2002

摘要:介紹了TMS320C5402芯片與RTL8019AS互聯(lián)網(wǎng)控制器的硬件接口電路的設(shè)計,實現(xiàn)了一個運行在TMS320C5402上的 小型嵌入式TCP/IP協(xié)議棧。對TCP/IP協(xié)議中的IP協(xié)議

2011-02-25 17:26:47 189

189 MiC roBlaze 是Xilinx公司針對嵌入式處理器開發(fā)應(yīng)用推出的一種32位通用微處理器IP核,利用它可以進行基于FPGA的嵌入式系統(tǒng)設(shè)計。本文結(jié)合圖像采集系統(tǒng)中對數(shù)據(jù)處理速度要求高,而系統(tǒng)

2011-05-14 17:00:51 26

26 目前利用FPGA設(shè)計高性能的嵌入式處理器已經(jīng)成為SOC設(shè)計的重要部分,對一種基于FPGA芯片的嵌入式PLC處理器進行了研究和設(shè)計,并采用了基于VHDL語言的自頂向下的模塊化設(shè)計方法,頂層

2011-09-28 18:19:50 2186

2186

TURBO51的工程背景是TURBO51嵌入式微處理器結(jié)構(gòu)設(shè)計上采取經(jīng)時間考驗過的32位機主流系統(tǒng)結(jié)構(gòu), 在嚴格保證對8051 指令集兼容的前提下, 通過重新定義其處理器核的系統(tǒng)結(jié)構(gòu)來挖掘處理器

2011-12-15 10:23:12 1530

1530

SX微處理器是美國Scenix公司推出的新一代微處理器本文主要介紹SX微處理器的通信機制和虛擬外設(shè)原理并詳細描述基于TCP/IP協(xié)議的Internet技術(shù)和Java虛擬機技術(shù)在SX微處理器控制下的具體實

2011-12-15 16:18:24 27

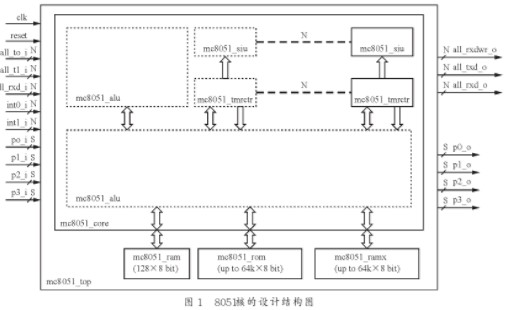

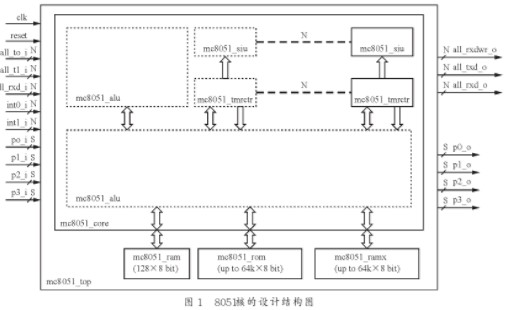

27 MC8051是與MCS一5l系列微處理器指令集完全兼容的8位嵌入式微處理器,通過芯核重用技術(shù),可廣泛應(yīng)用在一些面積要求比較苛刻,而對速度要求不是很高的片上系統(tǒng)中。 1 MC8051功能特點

2012-05-22 11:16:23 7805

7805

uIP 協(xié)議棧去掉了完整的 TCP/IP 中不常用的功能,簡化了通訊流程,但保留了網(wǎng)絡(luò)通信必須使用的協(xié)議,設(shè)計重點放在了 IP/TCP/ICMP/UDP/ARP 這些網(wǎng)絡(luò)層和傳輸層協(xié)議上,保證了其代碼的通用性和結(jié)構(gòu)的穩(wěn)定性。

2016-01-06 11:17:20 21

21 uip TCP/IP棧中文描述,uip TCP/IP棧是使用于低至8位或16位微處理器的嵌入式系統(tǒng)的一個可以實現(xiàn)的極小的TCP/IP協(xié)議棧

2016-03-01 17:51:39 9

9 uIP 協(xié)議棧是一種免費的可實現(xiàn)的極小的TCP/IP協(xié)議棧,可以使用于由8位或16位微處理器構(gòu)建的嵌入式系統(tǒng)。本文分析了uIP協(xié)議棧的結(jié)構(gòu)和應(yīng)用接口,并討論了如何將其應(yīng)用到51系列單片機上。

2016-07-15 15:27:00 0

0 MicroCore實驗室將四個兼容8051微處理器核的MCL51處理器集成到售價$99的Avnet/Digilent Xilinx Arty 開發(fā)板上,該開發(fā)板基于Xilinx Artix-7

2017-02-08 11:09:37 661

661 頻率4.77MHz)。 同樣的性能時鐘速率為什么可以提升20倍的差別?這是基于微處理器時序序列實現(xiàn)IP核的原因。微處理器中每個4.77MHz的時鐘在IP核中都被

2017-02-08 17:21:30 1017

1017 uIP協(xié)議棧在CC2430芯片上的移植研究_李偉勤

2017-03-19 11:28:02 0

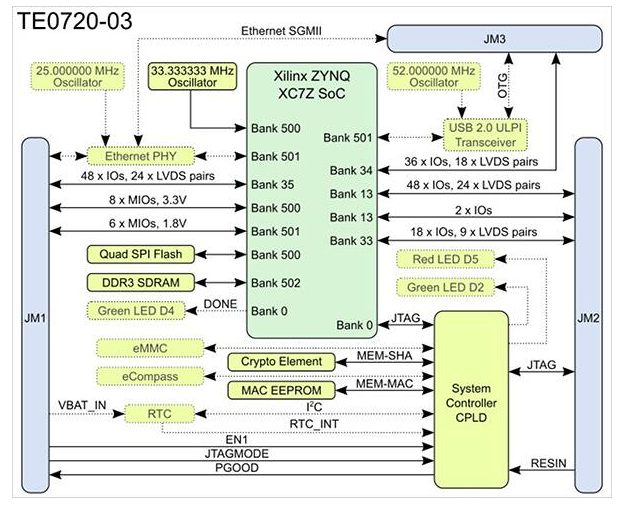

0 研究了TCP/IP通信協(xié)議棧在Xilinx 公司現(xiàn)場可編程門陣列FPGA上的實現(xiàn),介紹了其軟硬件的系統(tǒng)組成

和原理,提出一種不需操作系統(tǒng)的TCP/IP協(xié)議棧的高效工作模式,并在

2017-09-04 09:24:59 9

9 成本。微處理器根據(jù)不同的程序應(yīng)用,采用不同的配置數(shù)據(jù)對FPGA進行配置,使FPGA實現(xiàn)與該應(yīng)用有關(guān)的特定功能。詳細介紹了微處理器系統(tǒng)中連接簡單的被動串行配置方法和被動并行異步配置方法。 關(guān)鍵詞: 在應(yīng)用配置 FPGA配置 被動串行 被動并行異步 可編程邏輯器

2017-11-06 11:10:48 1

1 研究了嵌入式TCP/IP通信協(xié)議棧在Xilinx FPGA上的實現(xiàn),介紹了其軟硬件的系統(tǒng)組成和原理,提出一種實時操作系統(tǒng)上TCP/IP協(xié)議棧的高效工作模式,并在Virtex5 FPGA上移植成功。通過建立測試平臺進行數(shù)據(jù)傳輸測試,證明其具有穩(wěn)定、高效的通信性能,為嵌入式設(shè)備開發(fā)提供了新的思路。

2017-11-17 17:05:01 9560

9560

在FPGA中植入8051后, 還可在上面實現(xiàn)簡單的TCP/IP協(xié)議, 以支持遠程訪問或進行遠程調(diào)試, 這只是在嵌入FPGA的8051上的一個應(yīng)用。為了保證用戶能夠?qū)?b class="flag-6" style="color: red">8051實現(xiàn)不同的控制操作,設(shè)計時

2019-08-01 08:01:00 1945

1945

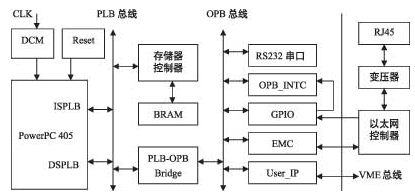

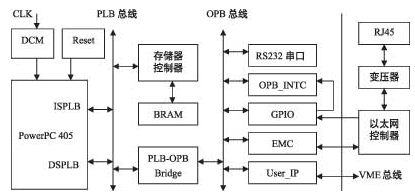

擴充、可升級的功能,已逐漸成為一個新興的技術(shù)方向。SoPC的核心是在FPGA上實現(xiàn)的嵌入式微處理器核,目前主要有Xilinx公司的32位軟核MicroBlaze、32位PowerPC系列處理器硬核PowerPC 405,以及Altera公司的Nios系列微處理器軟核等。

2021-06-17 11:40:52 3580

3580

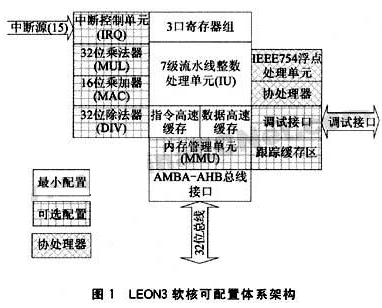

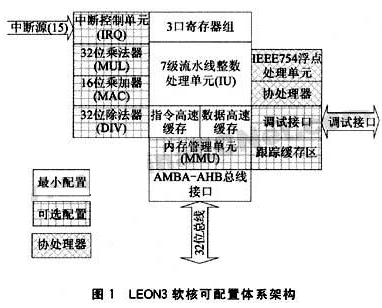

SoC芯片的核心是實現(xiàn)運算和控制功能的微處理器。LEON是一款基于SPARC V8架構(gòu)的開源微處理器IP軟核,在VHDL源代碼基礎(chǔ)上,結(jié)合具體需求加入定制的運算單元和外設(shè)接口建立SoC系統(tǒng)。在配置靈活的LEON核上運行Embedded Linux,提供SoC調(diào)試和測試的基本平臺。

2021-06-17 14:32:42 3523

3523

基于ARM微處理器的嵌入式TCP-IP協(xié)議的實現(xiàn)與應(yīng)用(嵌入式開發(fā)平臺搭建)-文檔為基于ARM微處理器的嵌入式TCP-IP協(xié)議的實現(xiàn)與應(yīng)用總結(jié)文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,

2021-08-04 14:38:35 22

22 STM32+ENC28J60+UIP協(xié)議棧實現(xiàn)WEB服務(wù)器示例

2021-12-06 09:21:14 34

34 在前文中,我們了解到兩種 FPGA 嵌入式處理器核方案:軟核與硬核。本文將展開討論軟核在一個基于 FPGA 通信系統(tǒng)中的應(yīng)用。軟核,由 FPGA...

2022-02-07 10:07:43 4

4 摘要: 現(xiàn)代 信號 處理系統(tǒng)通常需要在不同處理器之間實現(xiàn)高速數(shù)據(jù) 通信 ,SRIO協(xié)議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現(xiàn)SRIO協(xié)議的方法,并

2023-03-20 15:00:01 3755

3755 嵌入式微處理器是專為嵌入式系統(tǒng)設(shè)計的微處理器,它們是嵌入式系統(tǒng)的核心組件,負責(zé)執(zhí)行程序指令、處理數(shù)據(jù)和控制其他硬件設(shè)備。與通用微處理器相比,嵌入式微處理器通常具有針對特定應(yīng)用領(lǐng)域的優(yōu)化特性,如低功耗、小尺寸、高可靠性和實時操作能力。下面分別就嵌入式微處理器的原理和應(yīng)用進行簡要介紹。

2024-03-28 15:51:13 1841

1841 嵌入式微處理器是指嵌入到特定應(yīng)用系統(tǒng)中的微處理器,它是整個嵌入式系統(tǒng)的核心,由通用處理器演變而來,具有體積小、重量輕、成本低、可靠性高等優(yōu)點。與通用處理器相比,嵌入式微處理器在功能上進行了裁剪,去除

2024-03-29 11:39:54 1956

1956 嵌入式微處理器(Embedded Microprocessor)和數(shù)字信號處理器(Digital Signal Processor,簡稱DSP)是兩種常見的微處理器架構(gòu)。它們在應(yīng)用領(lǐng)域、設(shè)計理念

2024-04-21 09:50:14 3081

3081 要求的硬件和軟件技術(shù)。 在嵌入式微處理器的基礎(chǔ)上,我們可以考慮以下幾個方面進行詳細討論: 處理器架構(gòu)和指令集:嵌入式微處理器通常在特定的指令集架構(gòu)上運行,比如ARM架構(gòu)、MIPS架構(gòu)或者x86架構(gòu)。不同的架構(gòu)有不同的特點

2024-04-21 14:34:07 1712

1712 設(shè)計。本文將詳細介紹嵌入式微處理器的功能、原理與應(yīng)用,以期給讀者一個全面的了解。 一、功能 CPU處理能力:嵌入式微處理器內(nèi)置的CPU核心可以處理各種算法和指令,實現(xiàn)各種計算任務(wù)。CPU處理能力與芯片的主頻、指令集類型等因

2024-05-04 14:50:00 2320

2320 嵌入式微處理器是一種專門設(shè)計用于控制和執(zhí)行嵌入式系統(tǒng)任務(wù)的微處理器。與通用微處理器相比,嵌入式微處理器通常具有低功耗、小體積、低成本和高度可靠性等特點。在嵌入式系統(tǒng)中,嵌入式微處理器被廣泛應(yīng)用于各種

2024-04-21 14:52:24 1966

1966 等。在本文中,我們將詳細介紹嵌入式微處理器的幾類以及包含的重要參數(shù)。 一、嵌入式微處理器的幾類 通用微處理器 通用微處理器是指那些不專為嵌入式系統(tǒng)設(shè)計的處理器,如Intel的x86系列、ARM的Cortex-A系列等。這類處理器的優(yōu)點

2024-05-04 14:58:00 1776

1776 嵌入式微處理器是一種專門設(shè)計和應(yīng)用于嵌入式系統(tǒng)的微處理器。相比于常規(guī)計算機系統(tǒng),嵌入式系統(tǒng)通常具有更高的實時性、更低的功耗、較小的尺寸和成本以及更強的可靠性和穩(wěn)定性要求。嵌入式微處理器技術(shù)因此

2024-05-04 15:10:00 4239

4239 嵌入式微處理器的定義與發(fā)展 嵌入式微處理器指的是以處理器為核心的專用集成電路芯片,用于實現(xiàn)特定任務(wù)的計算或控制功能。它通常被嵌入在各種電子設(shè)備中,例如智能手機、電視機、冰箱、洗衣機等。相比于通用

2024-05-04 15:43:00 3282

3282 的任務(wù)或控制其他硬件設(shè)備。 嵌入式微處理器的出現(xiàn)可以追溯到20世紀70年代末以及80年代初。嵌入式微處理器通過集成了處理器核心、內(nèi)存、輸入輸出控制器以及其他必要的外圍接口等功能,實現(xiàn)了在一個微處理器芯片中集成多種復(fù)雜電路的目標。這種全集成的設(shè)計

2024-04-21 15:44:46 2625

2625 嵌入式微處理器是指集成在嵌入式系統(tǒng)中的微處理器,它是一種專門針對特定應(yīng)用的定制處理器。嵌入式微處理器的主要組成包括核心處理單元、內(nèi)存、外設(shè)、總線和輸入/輸出(I/O)接口等。 核心處理單元: 核心

2024-05-04 15:48:00 3519

3519 嵌入式微處理器是指內(nèi)部集成了CPU、存儲器、外設(shè)接口等功能的微型芯片,被廣泛應(yīng)用于各種嵌入式系統(tǒng)中。嵌入式系統(tǒng)是指嵌入在某種設(shè)備或系統(tǒng)中的微處理器系統(tǒng),主要用于控制和處理該設(shè)備的功能。 嵌入式微處理器

2024-05-04 16:31:00 3555

3555

電子發(fā)燒友App

電子發(fā)燒友App

評論