在同步電路設計中,邊沿檢測是必不可少的!

2012-03-01 09:59:04 5376

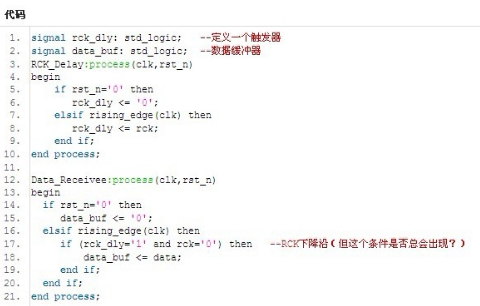

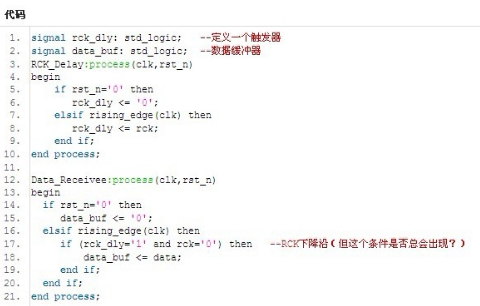

5376 在同步電路設計中,邊沿檢測是必不可少的!后一種方法所耗的資源要比前一種方法多(一個觸發器),但是就可以大大提高可靠性,這絕對是物有所值!!

2012-02-01 10:53:05 1066

1066

在同步電路設計中,邊沿檢測是必不可少的!

2017-08-16 15:19:32 2166

2166

如何檢測過流信號,并在電路中實現邏輯控制。

2019-05-24 07:29:00 6212

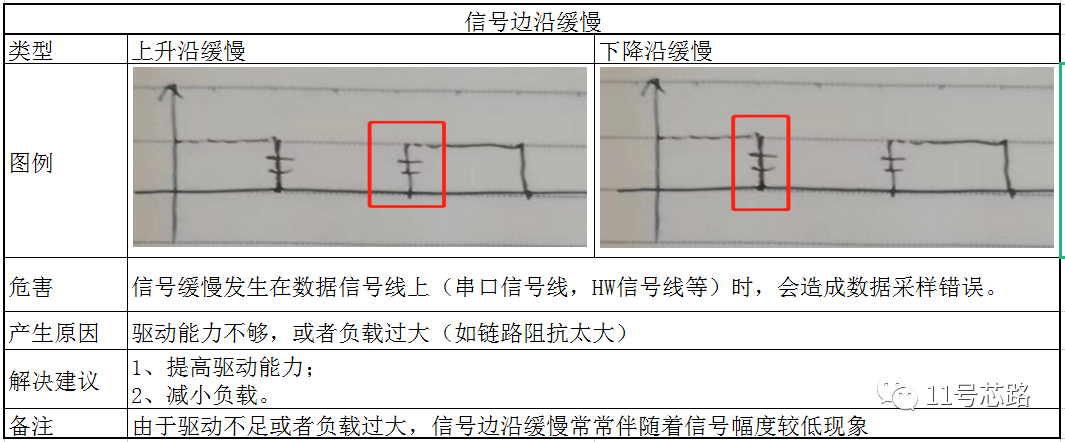

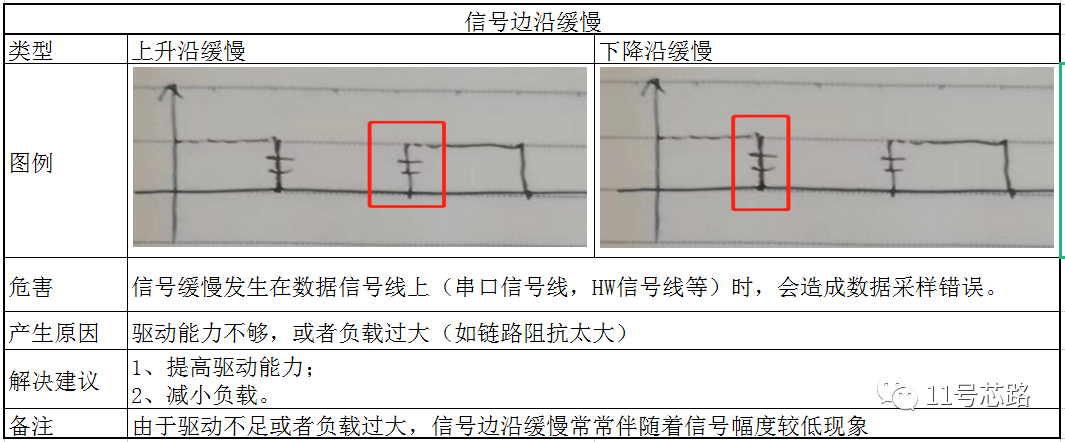

6212 隨著市場更高的需求,現在的設計者不得不考慮提高時鐘頻率,縮短信號的上升邊沿。

2023-10-02 16:35:00 1781

1781

異步電路原理是什么?有哪些優劣勢?通過英特爾的Loihi芯片實現異步電路?

2021-06-21 07:17:56

邊沿檢測設計報告

2017-09-26 15:38:19

FPGA_100天之旅_邊沿檢測

2017-09-28 13:37:44

Labview的TCP控件為同步超時模式實現的,在一對多場景明顯不夠用,效率低,看了官方例程也沒有異步TCP的說明,該如何實現異步TCP呢?

2022-04-25 17:08:00

常見的串行通信接口有哪些呢?STM32串口異步通信的過程該怎樣去完成呢?

2021-12-08 06:36:24

STM32定時器怎樣通過ETR模式進行邊沿檢測并計數呢?如何去實現?

2021-11-24 06:51:27

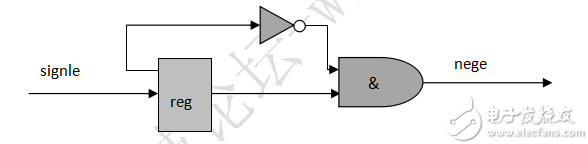

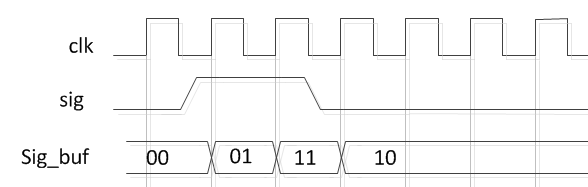

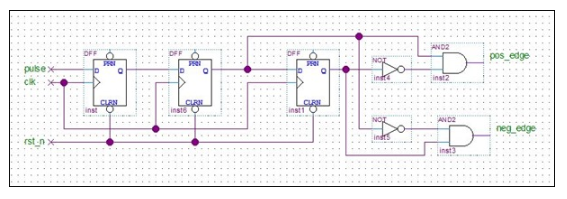

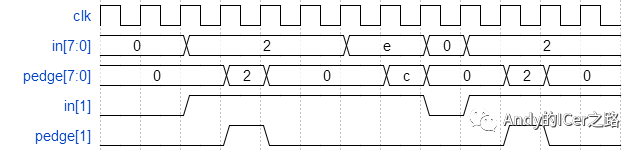

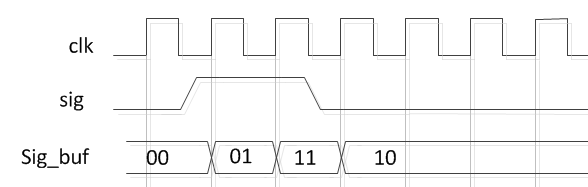

`fpga應用篇(二):邊沿檢測上一篇介紹了阻塞賦值與非阻塞賦值,這次我們利用非阻塞賦值產生一個簡單的應用即邊沿檢測,邊沿檢測一般用來產生使能信號。程序如下:綜合后電路:clk為主時鐘分頻之后得到

2017-04-06 21:28:08

verilog怎么將一個邊沿觸發信號的上升沿作為控制變量呢?

2023-05-10 10:38:09

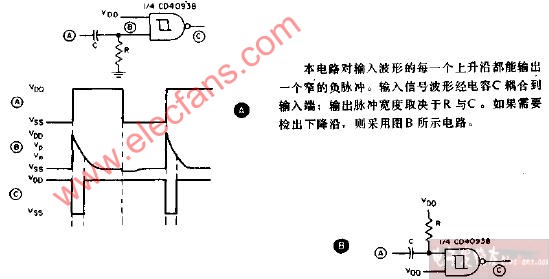

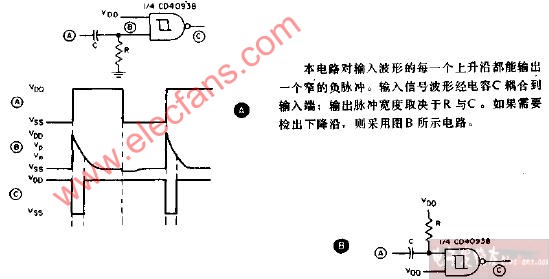

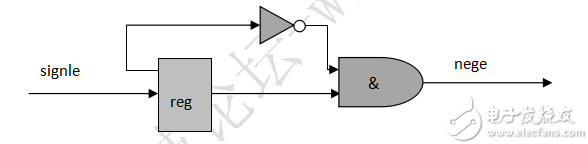

低到高的跳變。本節,夢翼師兄和大家一起學習一個經典的邊沿檢測電路,通過該電路,我們可以在信號出現跳變沿的時候產生尖峰脈沖,從而驅動其他電路模塊進行相應的動作。電路原理分析我們來分析一下這個電路結構

2019-12-04 10:24:31

什么是同步邏輯和異步邏輯,同步電路和異步電路的區別是什么?

2021-06-18 08:52:44

入圖,有沒有大神分析一下,是怎實現邊沿檢測的,它各個時期的電平狀態是什么

2016-04-13 14:36:25

程序邊沿檢測下降沿并統計數量(數量到達2后重新計數,并發送動作信號),但是最終發現檢測結果不準確,有時候能檢測到,有時候檢測不到。萬分感謝您的解答和建議!下面是verilog代碼[code]//邊沿檢測initial numinitial led

2021-08-21 12:58:00

設計一個脈搏檢測前置放大電路,主要是信號調理電路這一塊,目前用了AD620作為一級放大電路,還有一個運放LM324的有源低通濾波電路環節,二級放大電路該怎么設計呢,或者說我目前這個電路還存在什么問題

2016-05-16 19:24:58

的差別,而不會有什么波形上的不同。但是檢測結果卻顯示的很不正常,如下圖所示,上面是原始信號,下面是檢測到的信號,電阻是線性元件,不可能有濾波的功能啊,但是波形卻為什么變成了這樣呢?反復檢查了電路,并無異常。另,檢測電路接地要接mcu上的GND還是接電源上的地呢?二者有什么區別嗎?跪求解釋。

2019-01-16 08:24:53

在FPGA上實現時鐘信號的多路同步輸出該怎么做呢?好像要用到FPGA內部的PLL,將時鐘信號分成多路輸送到其他板塊,求高手解答該怎么做輸入時鐘由一個50M的晶振提供

2023-03-21 14:51:29

的寄存器的輸出端都是由同一個時鐘端驅動出來的,所有的寄存器在同一個步調上進行更新。同步電路中的信號,我們稱之為同步信號。如果在設計中,寄存器的時鐘端連接在不同的時鐘上,那么稱之為異步電路設計。 在異步電路中

2023-02-28 16:38:14

我看到網上關于邊沿檢測的講解,有個地方不理解,t0時刻和t1時刻分別是怎樣的時刻,trigger在時鐘上升沿經過觸發器輸出的信號和經過非門的信號是什么樣的關系?我的理解是trigger分別輸出后是兩個電平相反的信號,為什么相與之后就可以檢測是否為上升沿或者下降沿?謝謝。

2023-05-10 14:52:22

如何準確測量CAN節點的信號邊沿參數?

2021-05-08 06:27:36

驅動實現GPIO的脈沖信號檢測原理是什么?如何利用驅動去實現GPIO的脈沖信號檢測呢?

2022-03-04 08:48:48

新手求問:最近在做一個測試系統,我用了DAQ助手采集電壓信號來測量壓力又用了邊沿計數功能來測量轉角(通過轉角能求得體積參數),這里出現了一個問題:邊沿計數功能測試只能采樣(按要求),得不到采樣率,該

2015-06-02 21:18:23

請教大神:同時能檢測有源信號(如24V脈沖信號)和無源脈沖信號,接收端為5V單片機IO,我知道有源信號用光耦隔離后再接收,無源信號可以直接接收,但是怎樣能用一個電路實現兩種信號都可以接收呢?就是不管有源無源都可以接收。

2022-05-11 16:18:27

示波器輸入負載而言還是對于該信號源輸出阻抗而言?2.怎么實現高低阻抗不匹配的檢測呢,我看部分信號源可以設置輸出50歐和高阻態,那么如果后級示波器輸入阻抗不匹配怎么檢測呢?需要設計什么硬件電路檢測電流

2024-05-23 11:45:07

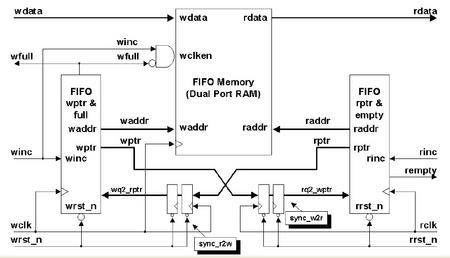

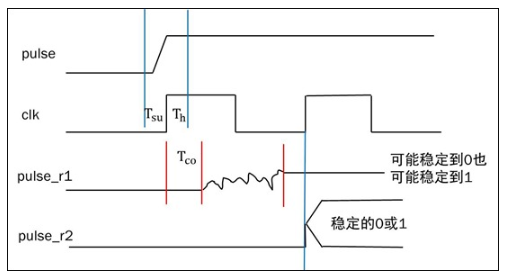

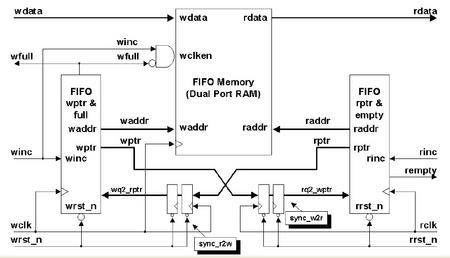

本文討論了在ASIC設計中數據在不同時鐘之間傳遞數據所產生的亞穩態問題,并提出了一種新的異步FIFO的設計方法,并用VHDL語言進行描述,利用Altera公司的Cyclone系列的EP1C6進行硬件實現,該電路軟件仿真和硬件實現已經通過驗證,并應用到各種電路中。

2021-04-29 06:54:00

打開開關的時候,功耗就上來了,無法進入低功耗模式,如何讓我們的藍牙模塊監測到高低電平之后,進入低功耗模式?群里問了下,說需要讓該io口支持雙邊沿觸發,即,上升沿和下降沿同時觸發檢測,請問,方向是否是正確的?其二,如果正確,如果設置雙邊沿觸發?

2019-11-07 15:55:30

的數據進行計數;停止位不參與,起始位加上數據位共9bit。該計數器的計數周期為9。本工程使用了檢測信號下降沿的方法,信號下降沿的檢測方法:檢查uart_rx的下降沿,就要用到FPGA里的邊沿檢測技術

2019-11-29 10:08:59

本人想做黑白塊的邊沿檢測,但是為了達到檢測的高精度,普通光電對管與光電傳感器的區別在哪里?因為原理相同,也不知道到底性能差別在哪里?有沒有大神可以一起討論一下?

2015-05-31 09:47:10

本文提出了一種簡易通用異步串行信號檢測裝置的設計方法。介紹了AVR 系列單片機Atmega128 和USB2.0 接口芯片的功能特性,并實現異步串行信號檢測裝置。闡述了通過USB2.0 接口控制單

2009-09-12 16:26:22 23

23 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 摘要:提出了1種基于CPLD、EPLD或FPGA等可編程邏輯器件的異步串行通信接口電路的設計方法。該方法簡單快捷。易于實現。而且可以作為異步串行通信接口的標準模塊插入到用戶的各

2010-04-30 09:58:41 46

46

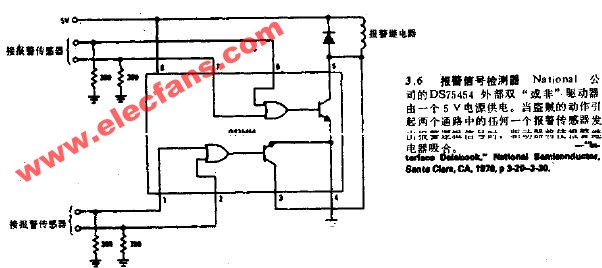

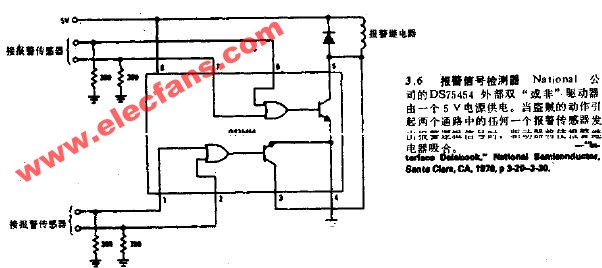

報警信號檢測器電路

2009-01-11 22:36:18 822

822

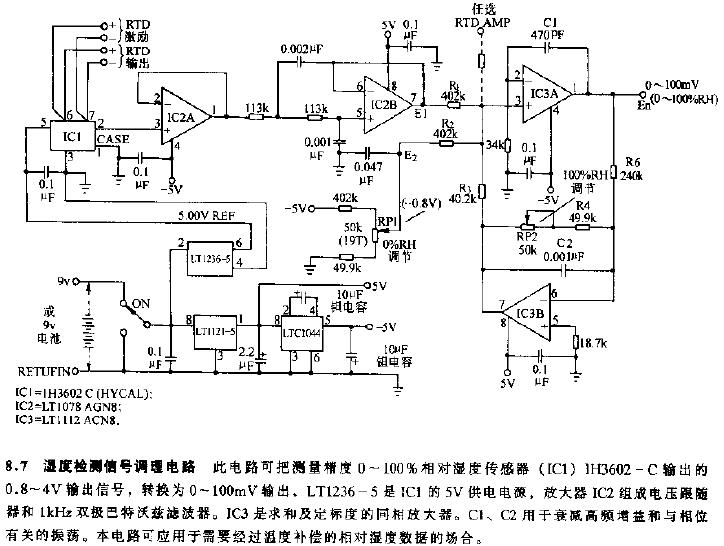

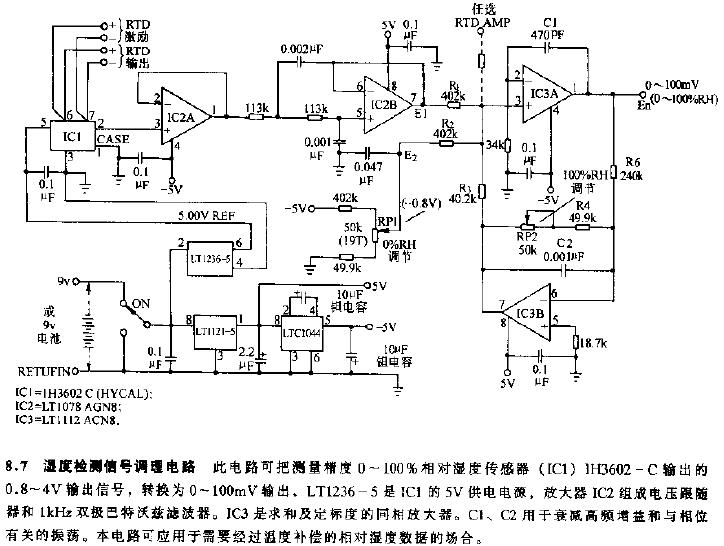

溫度檢測信號調理電路

2009-02-15 13:35:03 1576

1576

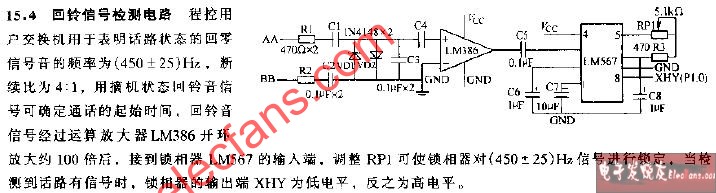

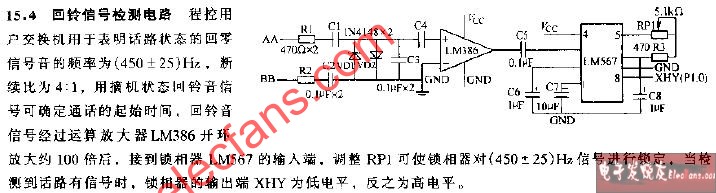

回鈴信號檢測電路

2009-02-28 11:45:54 839

839

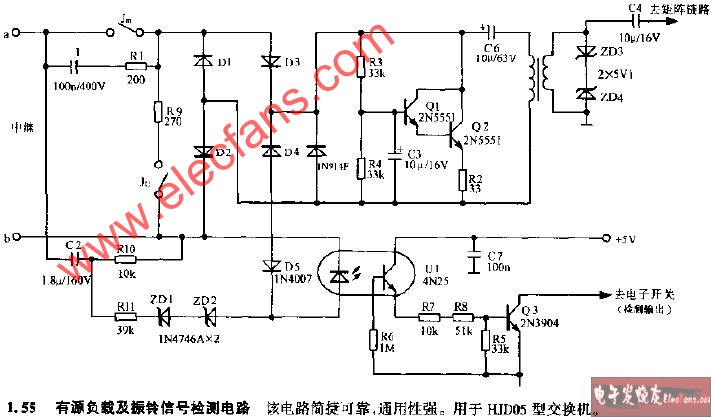

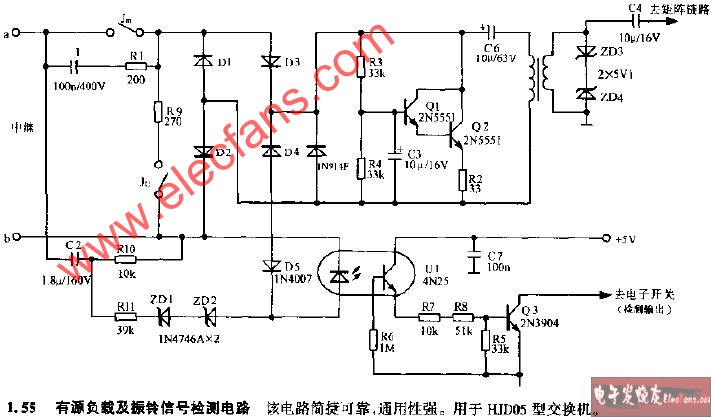

有源負載及振鈴信號檢測電路

2009-03-04 21:25:02 1360

1360

脈沖邊沿檢出器電路圖

2009-03-28 09:20:16 767

767

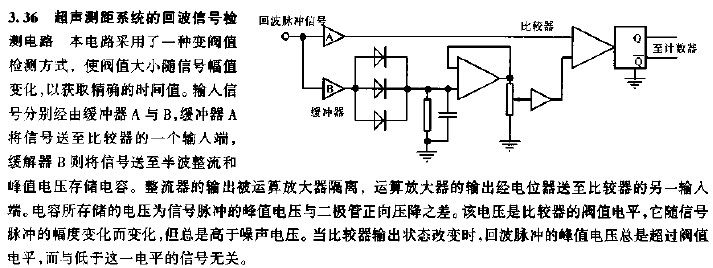

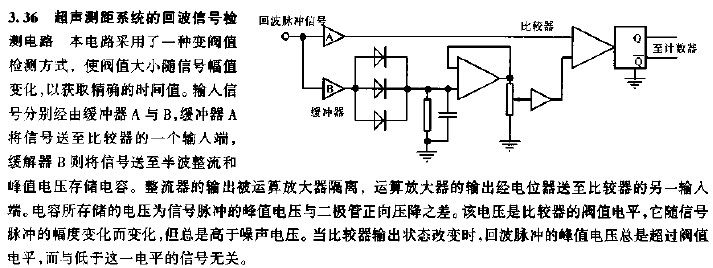

超聲測距系統的回波信號檢測電路

2009-04-22 19:33:13 1031

1031

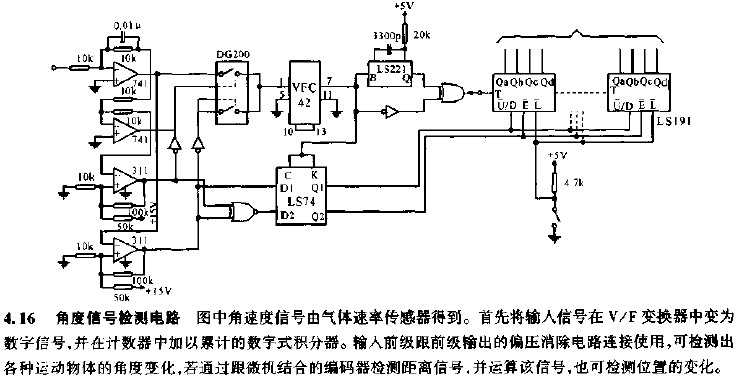

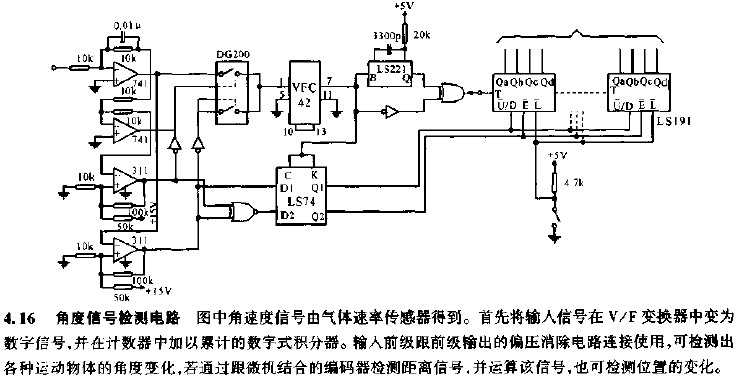

角度信號檢測電路

2009-04-24 21:50:05 837

837

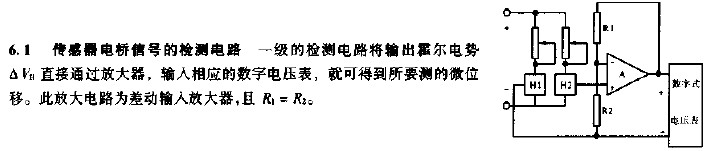

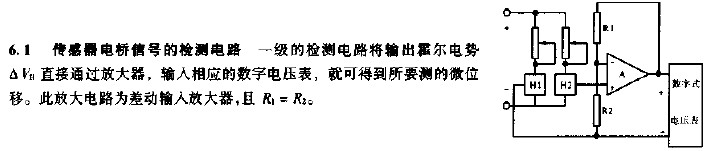

傳感器電橋信號的檢測電路

2009-04-26 15:58:38 996

996

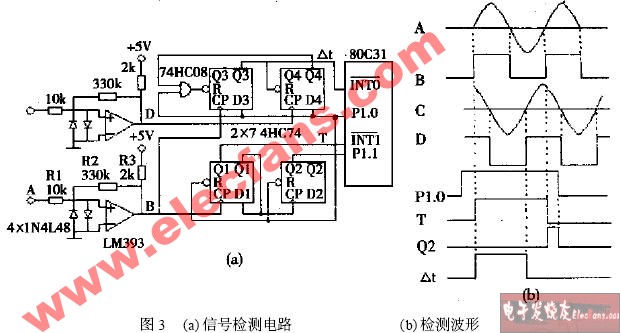

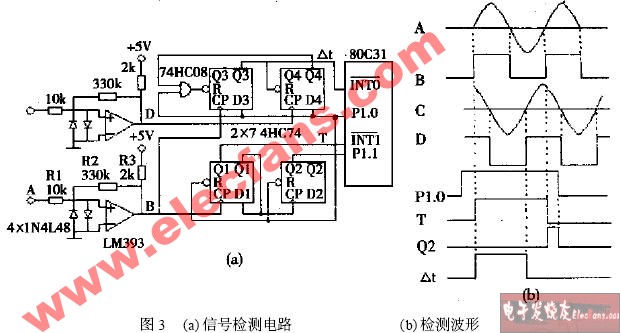

信號檢測電路如圖3 (a) ,波形如圖3 (b) 所示:

2009-06-06 17:58:26 2182

2182

邊沿檢測與提取程序

2018-01-29 14:56:31 0

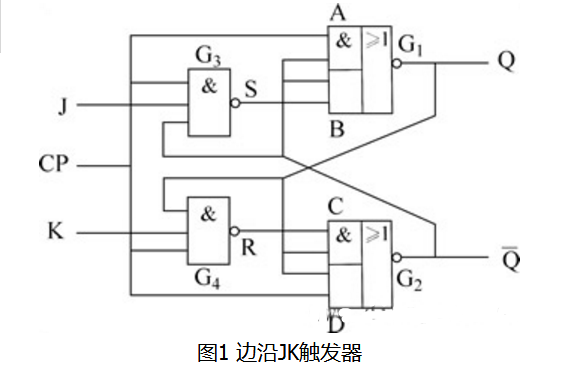

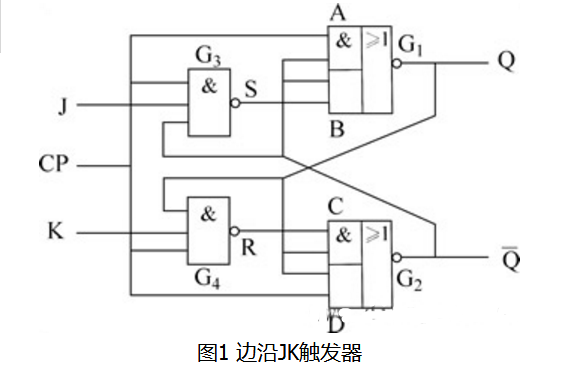

0 邊沿觸發器只在時鐘脈沖CP上升沿或下降沿時刻接收輸入信號,電路狀態才發生翻轉,從而提高了觸發器工作的可靠性和抗干擾能力,它沒有空翻現象。邊沿觸發器主要有維持阻塞D觸發器、邊沿JK觸發器、CMOS邊沿觸發器等。

2018-01-31 09:17:11 33188

33188

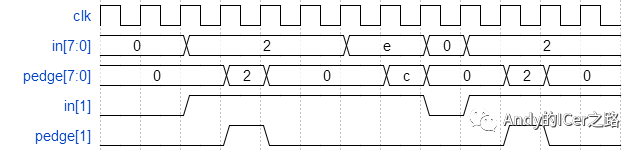

本文記錄一下關于用移位寄存器實現邊沿檢測的技巧。要學會硬件思維式的“模塊式”讀寫代碼,那么請多看別人的代碼,并用ISE或者VIVADO綜合出來看看。 邊沿檢測 邊沿檢測,顧名思義,就是檢查信號的邊沿

2018-04-15 10:26:01 3667

3667 方便我們學習,邊沿檢測。 這個電路的意思就是,輸入一個信號后我們經過一個寄存器,然 后把這個寄存器的輸出,和下次輸出的值取反后相與,那么我們就可 以這么想,如果一個高平的值經過這個寄存器后延遲一個上升沿后輸 出也為高

2018-06-13 11:20:07 6134

6134

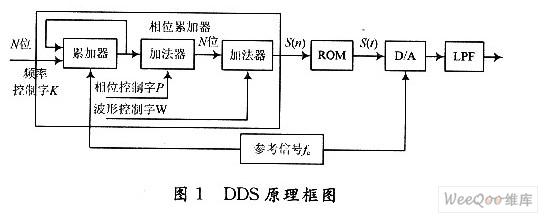

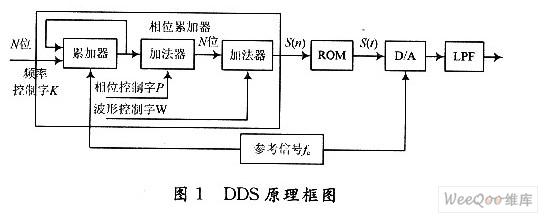

某型導彈測試設備電路板檢測儀主要完成該測試設備的電路板的故障檢測。該檢測系統要求激勵信號產生電路體積小,配置靈活,且精度高、轉換速度快。基于FPGA的DDS信號發生器較傳統信號發生器能夠更好地滿足檢測儀要求。

2019-01-10 09:15:00 5327

5327

一般而言,處理跨時鐘域的方法有這么幾種(大家在網上也都能找到資料,這些資料大都來自幾篇經典的論文,中文方面的資料大都是翻譯過著理解這幾篇論文而來):少量的數據用邊沿檢測電路,或者脈沖檢測電路,或者電平檢測電路,或者兩級觸發器;比較多的數據時用異步FIFO。

2018-09-10 10:06:00 13063

13063

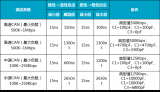

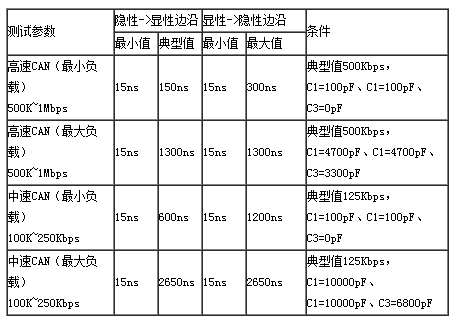

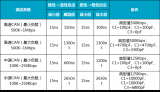

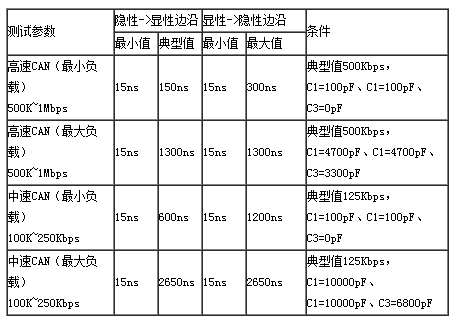

邊沿時間分為上升沿時間、下降沿時間。下降沿時間是按照電壓(20%~80%電壓區間,有些按照10%~90%電壓區間測量邊沿時間,文中以20%~80%電壓區間測量邊沿時間)。表中給出時間范圍,如果超出

2018-09-22 08:51:00 21393

21393

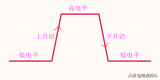

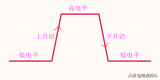

首先,我們看一下時鐘信號中最常見到的波形 - 矩形波(尤其是方波更常用)。在較低時鐘頻率的系統中我們看到的基本上都是以矩形波為主的時鐘信號,因為電路基本上都是靠時鐘的邊沿(上升沿或下降沿)進行

2018-12-06 11:53:10 64392

64392

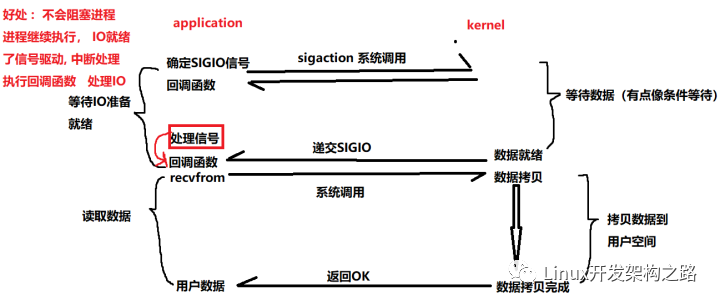

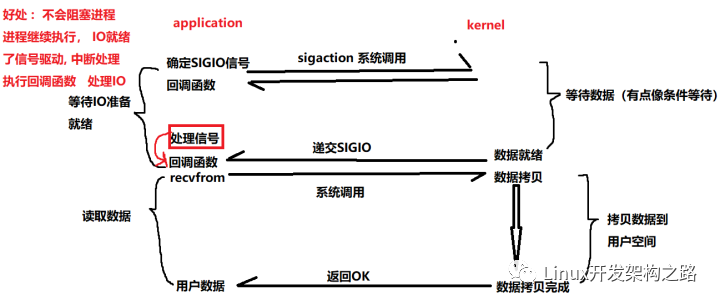

程序的二進制代碼在內存中都有著確定的執行流程,為什么收到異步信號以后,程序會被“中斷”,然后跳轉到這個handle函數里面去運行呢?內核怎么有能力讓程序做這樣的跳轉呢,總不可能臨時修改程序的可執行代碼吧?

2019-04-15 14:58:11 1337

1337 CAN總線設計規范對于CAN節點的信號邊沿各項參數都有著嚴格的規定,如果不符合規范,則在現場組網后容易出現不正常的工作狀態,各節點間出現通信故障。具體要求如表 1所示,為測試標準“GMW3122信號邊沿標準”。

2019-05-17 15:18:10 1616

1616

邊沿檢測電路(edge detection circuit)是個常用的基本電路。所謂邊沿檢測就是對前一個clock狀態和目前clock狀態的比較,如果是由0變為1,能夠檢測到上升沿,則稱為上升沿檢測

2019-11-19 07:09:00 11728

11728 異步電路 1. 電路的核心邏輯是組合電路,比如異步的FIFO/RAM讀寫信號、地址譯碼信號等電路; 2. 電路的輸出不依賴于某一個時鐘,也就說不是由時鐘信號驅動觸發器產生的; 3. 異步電路非常容易

2020-12-05 11:53:41 12647

12647 )都可以分解成4個狀態:①高電平 ②低電平 ③上升沿 ④下降沿。 圖1:開關信號 在PLC編程里,上升沿指令和下降沿指令可以直接調用;那么對于單片機的C語言編程,又如何實現邊沿信號的判斷呢?因為早期做過PLC編程的緣故,受PLC編程思路的影響

2021-05-03 10:14:00 5180

5180

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括Verilog仿真時常用的系統任務、雙向端口的使用(inout)、邊沿檢測”

2022-03-15 13:34:56 3146

3146 面這個電路我覺得肯定是第一時間想到的,直接對輸入信號分壓,單片機檢測高低電平就好了,另外防止過沖或者地漂移加上鉗位設計;

2022-08-02 17:42:09 9175

9175

所謂邊沿檢測,就是檢測輸入信號即上升沿或者下降沿的檢測。 邊沿檢測的電路很好實現:上一時刻為低電平,而當前時刻為高電平,此時就為上升沿;上一時刻為高電平,而當前時刻為低電平,此時就為上升沿。 通過

2022-11-26 10:20:09 2681

2681 , 那么究竟速率多高才能稱為高速電路呢,平時我們應該如何區分高速和低速呢? 大家可能會認為信號周期頻率 FCLOCK 高的才屬于高速設計 其實我們在設計時考慮的最高頻率往往取決于信號的有效頻率( 亦稱轉折頻率 ) Fknee 如上圖信

2023-03-26 02:30:05 1973

1973 邊沿檢測指令有掃描操作數的信號下降沿指令和掃描操作數的信號上升沿指令。

2023-04-10 09:38:27 2587

2587 邊沿檢測指令有掃描操作數的信號下降沿指令和掃描操作數的信號上升沿指令。

2023-04-12 09:23:26 10916

10916 本文將從Verilog和邊沿檢測的基本概念入手,介紹Verilog邊沿檢測的原理和應用代碼示例。

2023-05-12 17:05:56 5473

5473

對于8位向量中的每個位,檢測輸入信號何時從一個時鐘周期的0變為下一個時鐘周期的1(類似于上升沿檢測)。應在從0到1的跳變發生后的周期內設置輸出位。

2023-06-05 16:24:02 1395

1395

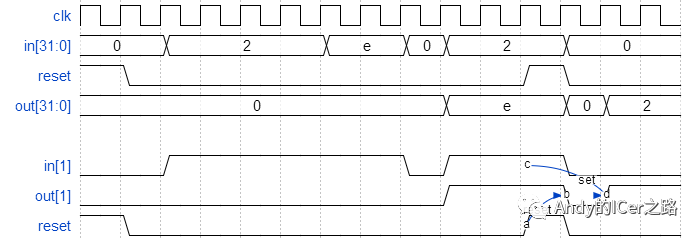

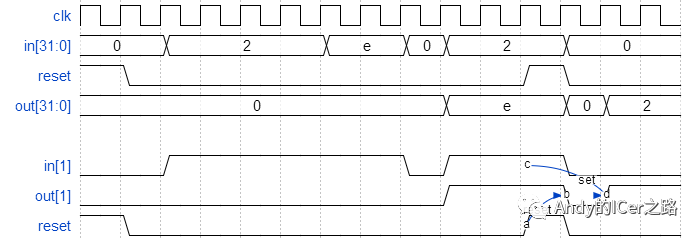

在設計雙邊沿采樣電路(Dual-edge triggered flip-flop)之前,先從單邊沿采樣電路設計(Edge capture register)開始。

2023-06-05 16:27:30 2355

2355

1、什么是邊沿檢測 邊沿檢測用于檢測信號的上升沿或下降沿,通常用于使能信號的捕捉等場景。 2、采用1級觸發器的邊沿檢測電路設計(以下降沿為例) 2.1、設計方法 設計波形圖如下所示: 各信號說明如下

2023-06-17 14:26:40 3847

3847

簡單的說觸發器實現邊沿出發是通過兩級鎖存器實現的,比如上升沿觸發其實是,前一級是低電平鎖存,后一級是高電平鎖存。

2023-06-28 11:18:32 3213

3213

邊沿檢測大致分為:上升沿檢測,下降沿檢測和,雙沿檢測。原理都是通過比輸入信號快很多的時鐘去采集信號,當出現兩個連續的采集值不等的時候就是邊沿產生處。

2023-06-28 15:19:12 4359

4359

。如果該指令檢測到 RLO 從“0”變為“1”,則說明出現了一個信號上升沿。 每次執行指令時,都會查詢信號上升沿。檢測到信號上升沿時,該指令輸出 Q 將立即返回程序代碼長度的信號狀態“1”。在其它任何情況下,該輸出返回的信號狀態均為“0”。 說明 修改邊沿

2023-06-28 16:20:11 1491

1491

同步電路與異步電路有何區別 同步電路和異步電路是數字電路中兩種類型的電路,兩種電路在功能、結構、時序要求等方面都存在差異。同步電路和異步電路分別適用于不同類型的應用場景,因此在設計數字電路時要根據

2023-08-27 16:57:02 12401

12401 對于多位的異步信號如何進行同步呢? 異步信號(Asynchronous Signals)是指系統中發生的事件或者信號,它們的發生時間不可預測、不可控制,與其他的進程、線程以及系統中的各種資源之間

2023-09-12 11:18:09 2192

2192 高頻信號為什么容易衰減?為什么高頻信號不能直接通過電阻的分壓來實現信號的衰減呢? 隨著科技的不斷發展,生活中越來越少有人不了解“高頻信號”的概念。高頻信號是指頻率比較高、波長比較短的電磁波信號,往往

2023-10-20 15:02:24 4220

4220 反電勢過零檢測電路如何選擇電阻呢? 反電勢過零檢測電路主要是用于控制電器開關的電路,實現準確的開關控制。在該電路中,電阻的選擇是非常重要的,直接關系到檢測電路的可靠性和穩定性。下面就來詳細闡述反電勢

2023-10-26 18:19:08 1511

1511 一. 談信號驅動IO (對比異步IO來看) 信號驅動IO 對比 異步 IO進行理解 信號驅動IO: 內核將數據準備好的時候, 使用SIGIO信號通知應用程序進行IO操作 通知應用程序處理IO

2023-11-08 15:32:41 1915

1915

什么是同步邏輯和異步邏輯?同步電路與異步電路有何區別? 同步邏輯和異步邏輯是計算機科學中的兩種不同的邏輯設計方法。它們分別用于描述數字電路中信號的傳輸和處理方式。同步邏輯是指電路中的各個組件在一個

2023-11-17 14:16:03 3516

3516 部分是獨立運行的,沒有明確定義的時鐘信號來同步它們的操作。相反,每個部分在滿足特定的條件下單獨啟動和運行,通過相互之間的通信來完成所需的協作。異步電路通常采用握手協議來確保數據的正確傳輸,即在發送方發送數據

2023-12-07 10:53:42 5316

5316 不良影響。本文將詳細介紹異步信號與同步電路交互問題的背景、常見的問題及其解決方法。 一、背景 在現代電子系統中,通信和交互已經成為不可或缺的一部分。為了實現設備之間的信息傳遞和控制,我們常常會使用各種不同的信號

2023-12-07 10:53:45 1525

1525 同步復位和異步復位到底孰優孰劣呢? 同步復位和異步復位是兩種不同的復位方式,它們各自有優勢和劣勢,下面將詳細介紹這兩種復位方式。 同步復位是指在時鐘的邊沿(上升沿或下降沿)發生時對系統進行復位。這種

2024-01-16 16:25:52 2718

2718 什么是時鐘信號?數字電路的時鐘信號是怎么產生呢? 時鐘信號,也稱為時鐘脈沖,是用于同步數字電路中所有操作的基本信號。它提供了一個參考頻率,使得所有電路元件都能按照同樣的節奏進行工作。時鐘信號是一個

2024-01-25 15:40:52 15221

15221 脈沖觸發器和邊沿觸發器是數字電路中常用的存儲器元件。它們都是根據輸入信號的變化狀態進行觸發,并且可以實現特定的功能。然而,它們在觸發方式、觸發條件和觸發時機等方面存在一些差異。本文將詳細介紹脈沖

2024-02-06 13:45:50 6967

6967 FPGA(現場可編程門陣列)在處理異步信號時,需要特別關注信號的同步化、穩定性以及潛在的亞穩態問題。由于異步信號可能來自不同的時鐘域或外部設備,其到達時間和頻率可能不受FPGA內部時鐘控制,因此處理起來相對復雜。以下是對FPGA異步信號處理方法的詳細探討。

2024-07-17 11:10:40 2415

2415 統一的時鐘信號進行工作,各個部分的輸出與輸入之間存在固定的時序關系。同步電路通常用于數據傳輸、存儲器、處理器等高速電子系統中。 異步電路(Asynchronous Circuit)是指電路中的各個部分不依賴于統一的時鐘信號,而是根據輸入信號的變化來控制輸出信號

2024-07-22 17:37:00 1227

1227 邊沿觸發器在數字信號處理器(DSP)中的應用是廣泛而重要的。作為數字電路中的關鍵元件,邊沿觸發器以其獨特的觸發機制和穩定的性能,在DSP中扮演著至關重要的角色。以下將詳細介紹邊沿觸發器在DSP中的應用,包括其工作原理、優勢、具體應用實例以及未來發展趨勢。

2024-07-27 14:51:58 1728

1728 邊沿觸發器(Edge-Triggered Flip-Flop)是一種數字邏輯電路,其狀態變化由輸入信號的邊沿控制,即由輸入信號從低電平變為高電平或從高電平變為低電平的瞬間觸發。邊沿觸發器廣泛應用

2024-08-09 17:29:06 1766

1766 邊沿觸發器是一種數字邏輯電路,其動作特點主要體現在以下幾個方面: 觸發方式:邊沿觸發器的動作是由輸入信號的邊沿變化引起的。當輸入信號從低電平變為高電平或從高電平變為低電平時,觸發器的狀態會發生改變

2024-08-09 18:17:38 2022

2022 作為雙穩態電路的一種,其輸出狀態Q在時鐘信號的上升沿或下降沿(具體取決于觸發器的設計)到來時,會根據輸入信號D的狀態進行翻轉或保持不變,從而實現對信號的存儲和傳輸功能。 在數字電子系統中,邊沿式D觸發器被廣泛應用于各種

2024-08-22 10:15:40 2377

2377 邊沿JK觸發器是一種數字邏輯電路,廣泛應用于數字電路設計中。它具有多種功能,包括同步操作、存儲數據、實現時序邏輯等。以下是對邊沿JK觸發器功能的分析: 同步操作 邊沿JK觸發器是一種同步觸發器,它在

2024-08-28 09:50:12 2291

2291

電子發燒友App

電子發燒友App

評論