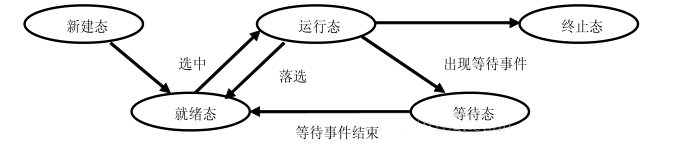

三態模型

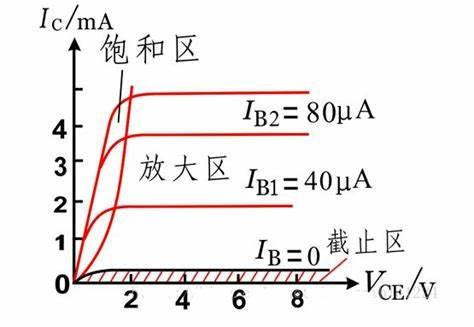

一個進程從創建而產生至撤銷而消亡的整個生命周期,可以用一組狀態加以刻劃,根據三態模型,進程的生命周期可分為如下三種進程狀態: 1. 運行態(running):占有處理器正在運行 2. 就緒態(ready):具備運行條件,等待系統分配處理器以便運行 3. 等待態(blocked):不具備運行條件,正在等待某個事件的完成。

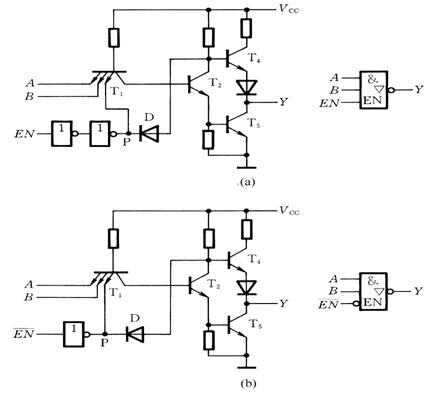

下面是三個狀態的轉換圖:

運行狀態的進程將由于出現等待事件而進入等待狀態,當等待事件結束之后等待狀態的進程將進入就緒狀態,而處理器的調度策略又會引起運行狀態和就緒狀態之間的切換。

引起進程狀態轉換的具體原因如下:

運行態—→等待態:等待使用資源;如等待外設傳輸;等待人工干預。

等待態—→就緒態:資源得到滿足;如外設傳輸結束;人工干預完成。

運行態—→就緒態:運行時間片到;出現有更高優先權進程。

就緒態—→運行態:CPU 空閑時選擇一個就緒進程。

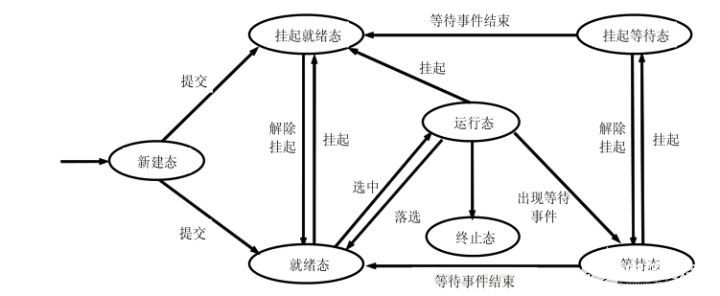

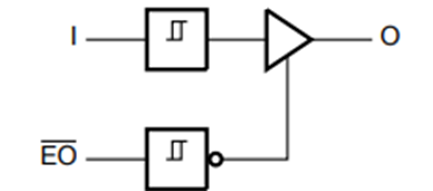

五態模型

在一個實際的系統里進程的狀態及其轉換比上節敘述的會復雜一些,例如引入專門的新建態(new)和終止態(exit )

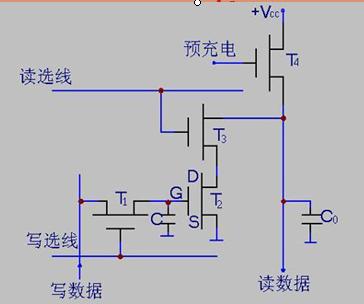

狀態轉換圖如下所示:

?

新建態對應于進程剛剛被創建的狀態。創建一個進程要通過兩個步驟,

為一個新進程創建必要的管理信息,

讓該進程進入就緒態。此時進程將處于新建態,它并沒有被提交執行,而是在等待操作系統完成創建進程的必 要操作。需要注意的是,操作系統有時將根據系統性能或主存容量的限制推遲新建態進程的提交

類似地,進程的終止也要通過兩個步驟,首先,是等待操作系統進行善后,然后,退出主存。當一個進程到達了自然結束點,或是出現了無法克服的錯誤,或是被操作系統所終結,或是被其他有終止權的進程所終結,它將進入終止態。進入終止態的進程以后不再執行,但依然臨時保留在操作系統中等待善后。一旦其他進程完成了對終止態進程的信息抽取之后,操作系統將刪除該進程。

引起進程狀態轉換的具體原因如下:

NULL—→新建態:執行一個程序,創建一個子進程。

新建態—→就緒態:當操作系統完成了進程創建的必要操作,并且當前系統的性能和虛擬內存的容量均允許。

運行態—→終止態:當一個進程到達了自然結束點,或是出現了無法克服的錯誤,或是被操作系統所終結,或是被其他有終止權的進程所終結。

終止態—→NULL:完成善后操作。

就緒態—→終止態:未在狀態轉換圖中顯示,但某些操作系統允許父進程終結子進程。

等待態—→終止態:未在狀態轉換圖中顯示,但某些操作系統允許父進程終結子進程。

七態模型

進程的掛起

到目前為止,我們或多或少總是假設所有的進程都在內存中。事實上,可能出現這樣一些情況,例如由于進程的不斷創建,系統的資源已經不能滿足進程運行的要求,這個時候就必須把某些進程掛起(suspend),對換到磁盤鏡像區中,暫時不參與進程調度,起到平滑系統操作負荷的目的。

引起進程掛起的原因是多樣的,主要有:

系統中的進程均處于等待狀態,處理器空閑,此時需要把一些阻塞進程對換出去,以騰出足夠的內存裝入就緒進程運行。

進程競爭資源,導致系統資源不足,負荷過重,此時需要掛起部分進程以調整系統負荷 ,保證系統的實時性或讓系統正常運行。

把一些定期執行的進程(如審計程序、監控程序、記賬程序)對換出去,以減輕系統負荷。

用戶要求掛起自己的進程,以便根據中間執行情況和中間結果進行某些調試、檢查和改正。

父進程要求掛起自己的后代進程,以進行某些檢查和改正。

操作系統需要掛起某些進程,檢查運行中資源使用情況,以改善系統性能;或當系統出現故障或某些功能受到破壞時,需要掛起某些進程以排除故障。

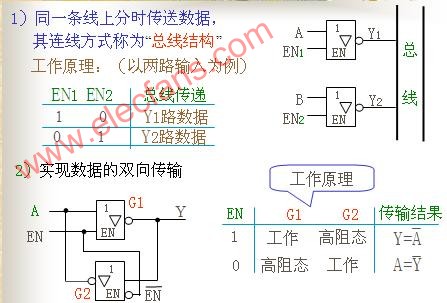

七態模型描述

下面是具有七態模型的進程狀態及其轉換:

?

?

在此類系統中,進程增加了兩個新狀態:

掛起就緒態(ready,suspend)

掛起就緒態表明了進程具備運行條件但目前在二級存儲器中,只有當它被對換到主存才能被調度執行 掛起等待態(blocked,suspend)掛起等待態則表明了進程正在等待某一個事件且在二級存儲器中。

引起進程狀態轉換的具體原因如下:

等待態—→掛起等待態:如果當前不存在就緒進程,那么至少有一個等待態進程將被對換出去成為掛起等待態;操作系統根據當前資源狀況和性能要求,可以決定把等待態進程對換出去成為掛起等待態。

掛起等待態—→掛起就緒態:引起進程等待的事件發生之后,相應的掛起等待態進程將轉換為掛起就緒態。

掛起就緒態—→就緒態:當內存中沒有就緒態進程,或者掛起就緒態進程具有比就緒態進程更高的優先級,系統將把掛起就緒態進程轉換成就緒態。

就緒態—→掛起就緒態:操作系統根據當前資源狀況和性能要求,也可以決定把就緒態進程對換出去成為掛起就緒態。

掛起等待態—→等待態:當一個進程等待一個事件時,原則上不需要把它調入內存。但是在下面一種情況下,這一狀態變化是可能的。當一個進程退出后,主存已經有了一大塊自由空間,而某個掛起等待態進程具有較高的優先級并且操作系統已經得知導致它阻塞的事件即將結束,此時便發生了這一狀態變化。

運行態—→掛起就緒態:當一個具有較高優先級的掛起等待態進程的等待事件結束后,它需要搶占 CPU,,而此時主存空間不夠,從而可能導致正在運行的進程轉化為掛起就緒態。另外處于運行態的進程也可以自己掛起自己。

新建態—→掛起就緒態:考慮到系統當前資源狀況和性能要求,可以決定新建的進程將被對換出去成為掛起就緒態。

可以把一個掛起進程等同于不在主存的進程,因此掛起的進程將不參與進程調度直到它們被對換進主存。

一個掛起進程具有如下特征:

該進程不能立即被執行。

掛起進程可能會等待一個事件,但所等待的事件是獨立于掛起條件的,事件結束并不能導致進程具備執行條件。

進程進入掛起狀態是由于操作系統、父進程或進程本身阻止它的運行。

結束進程掛起狀態的命令只能通過操作系統或父進程發出。

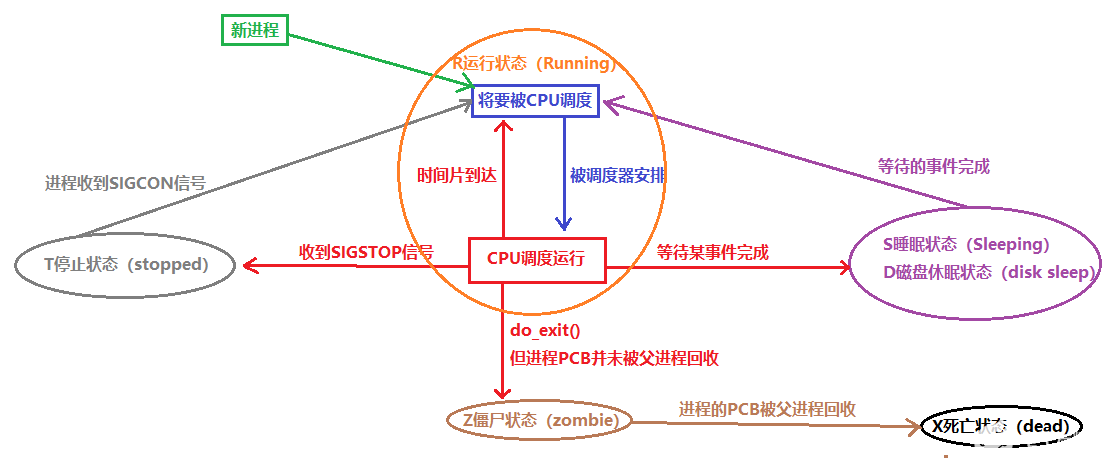

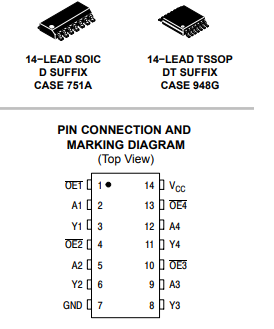

Linux操作系統的進程狀態轉換

Linux操作系統的進程

/*

* The task state array is a strange "bitmap" of

* reasons to sleep. Thus "running" is zero, and

* you can test for combinations of others with

* simple bit tests.

*/

static const char * const task_state_array[] = {

"R (running)", /* 0 */

"S (sleeping)", /* 1 */

"D (disk sleep)", /* 2 */

"T (stopped)", /* 4 */

"t (tracing stop)", /* 8 */

"X (dead)", /* 16 */

"Z (zombie)", /* 32 */

};

?

從Linux源碼中可以看出,Linux下有7中進程狀態:

R運行狀態(Running):處于運行狀態的進程并不帶表一定就正在被CPU調度運行,它包括了正在被CPU運行的進程和可以被CPU調度運行的程序,也就是說改狀態包含了三狀態模型中的就緒態和運行態。

S睡眠狀態(Sleeping):處于改狀態的進程表示該進程正在等待某時間的完成,通常也稱為可中斷睡眠狀態,該狀態屬于三狀態模型中的阻塞態。

D磁盤休眠狀態(disk sleep):該狀態也叫做不可中斷睡眠狀態,處于該狀態的進程通常都在等待I/O操作的結束,該狀態也屬于三狀態模型中的阻塞態。

T停止狀態(stopped):我們可以通過向進程發送SIGSTOP信號讓目標進程處于停止狀態,通過向處于停止狀態的進程發送SIGCON信號讓目標進程繼續運行,該狀態也屬于三狀態模型中的阻塞態。

t追蹤停止狀態(tracing stop):

X死亡狀態(dead):該狀態只是一個返回狀態,不會在任務列表中見到,該狀態屬于退出狀態。

Z僵尸狀態(zombie):當一個進程退出,但它的父進程并沒有去收回該進程的信息時,該進程所處的狀態叫做僵尸狀態,該狀態屬于退出狀態。

Linux系統進程狀態間的切換

?

創建一個新進程,操作系統會為該新進程創建一個空白PCB(task_struct),用來存儲該進程的各項信息。

電子發燒友App

電子發燒友App

評論