plc時序圖怎么看

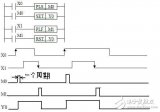

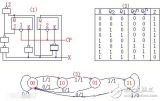

1. 用時序圖分析圖4-42所示梯形圖的工作原理。

2. 若X0信號如圖所示,請再分析該梯形圖的工作原理。

例題分析

(1) X0信號使Y0及T0線圈接通。

(2) T0線圈接通1S后,T0的常開觸點閉合,常閉觸點斷開。T0的常開觸點接通Y1及T1線圈,此過程均在一個掃描周期內完成,該掃描周期直至ED結束(注意:PLC是循環掃描工作方式)。

(3) 在T0觸點動作的下一個周期,T0的常閉觸點使Y0失電,Y0常開觸點斷開使T0線圈失電,使 T0常開觸點、常閉觸點同時復位。

(4) T1線圈接通1S后,T1的常開、常閉觸點均動作。

(5) 在下一個掃描周期T1的常開觸點使Y0接通,Y0的常開觸點又接通T0線圈。如此循環至X1信號到來使全系統復位。根據上述分析畫出如圖4-43所示的時序圖,因梯形圖中Y0、Y2、Y4、Y6、均為并聯關系,時序圖中只畫了Y0的圖形,Y1、Y3、T5、T7亦如此。

此題,是一個典型的霓虹燈控制程序,通過分析此題應更進一步理解PLC的循環掃描工作方式。

當X0為“ ”時在第③過程中只能將Y0關斷一個掃描周期,實際中裸眼觀察結果是Y0、Y2、Y4、Y6常亮。

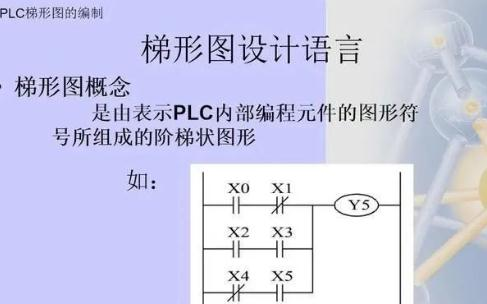

PLC梯形圖的分析方法和步驟

一、 總體分析

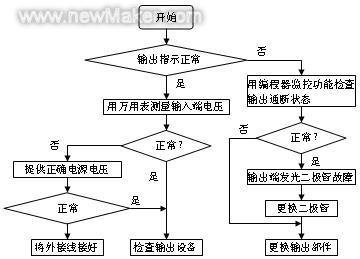

1 系統分析

依據控制系統所需完成的控制任務,對被控對象的工藝過程、工作特點以及控制系統的控制過程、控制規律、功能和特征進行詳細分析,明確輸入、輸出物理量是開關量還是模擬量,明確劃分控制的各個階段及其特點,階段之間的轉換條件,畫出完整的工作流程圖和各執行元件的動作節拍表。

2 看主電路

進一步了解工藝流程及其對應的執行裝置和元器件。

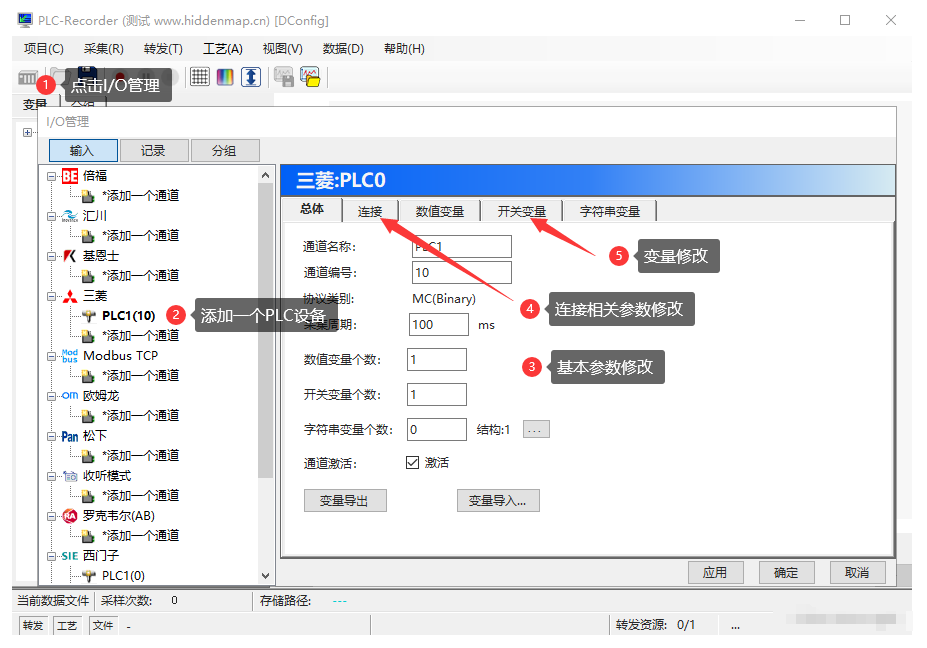

3 看PLC控制系統的I/O配置和PLC的I/O接線

了解輸入信號和對應輸入繼電器的配置、輸出繼電器的配置及其所接的對應負載。

在沒有給出輸入/輸出設備定義和PLC的I/O配置的情況下,應根據PLC的I/O接線圖或梯形圖和指令語句表,做出輸入/輸出設備定義和PLC的I/O配置。

4 通過PLC的I/O接線圖了解梯形圖

PLC的I/O接線是連接主電路和PLC梯形圖的紐帶。

1) 根據用電器(如電動機、電磁閥、電加熱器等)主電路控制電器(接觸器、繼電器)主觸點的文字符號,在PLC的I/O接線圖中找出相應編程元件的線圈,便可得知控制該控制電器的輸出繼電器,再在梯形圖或語句表中找到該輸出繼電器的程序段,并做出標記和說明。〖JP〗

2) 根據PLC的 I/O接線圖的輸入設備及其相應的輸入繼電器,在梯形圖(或語句表)中找出輸入繼電器的動合觸點、動斷觸點,并做出相應標記和說明。

二、 梯形圖的結構分析

1 PLC控制系統梯形圖的特點

(1) PLC控制系統的輸入信號和輸出負載

繼電器電路圖中的交流接觸器和電磁閥等執行機構用PLC的輸出繼電器來控制,它們的線圈接在PLC的輸出端。按鈕、控制開關、限位開關、接近開關等用來給PLC提供控制命令和反饋信號,它們的觸點接在PLC的輸入端。

(2) 繼電器電路圖中的中間繼電器和時間繼電器的處理

繼電器電路圖中的中間繼電器和時間繼電器的功能用PLC內部的輔助繼電器和定時器來完成,它們與PLC的輸入繼電器和輸出繼電器無關。

(3) 設置中間單元

在梯形圖中,若多個線圈都受某一觸點串/并聯電路的控制,為了簡化電路,在梯形圖中可設置用該電路控制的輔助繼電器,輔助繼電器類似于繼電器電路中的中間繼電器。

(4) 時間繼電器瞬動觸點的處理

時間繼電器除了延時動作的觸點外,還有在線圈得電或失電時立即動作的瞬動觸點。對于有瞬動觸點的時間繼電器,可以在梯形圖中對應的定時器的線圈兩端并聯輔助繼電器,后者的觸點相當于時間繼電器的瞬動觸點。

(5) 外部聯鎖電路的設立

為了防止控制正/反轉的兩個接觸器同時動作,造成三相電源短路,除了在梯形圖中設置與它們對應的輸出繼電器的線圈串聯的動斷觸點組成的軟互鎖電路外,還應在PLC外部設置硬互鎖電路。

2 梯形圖的結構分析

采用一般編程方法還是采用順序功能圖編程方法;采用順序功能圖的單序列結構還是選擇序列結構、并行序列結構,使用啟/保/停電路、步進順控指令進行編程還是用置位/復位指令進行編程。這部分內容見第四章和第五章。

梯形圖的分解由操作主令電路(如按鈕)開始,查線追蹤到主電路控制電器(如接觸器)動作,中間要經過許多編程元件及電路,查找起來比較困難。

無論多么復雜的梯形圖,都是由一些基本單元構成的。按主電路的構成情況,利用逆讀溯源法,把梯形圖和指令語句表分解成與主電路的用電器(如電動機)相對應的幾個基本單元,然后一個環節、一個環節地分析,最后再利用順讀跟蹤法把各環節串起來。

(1) 按鈕、行程開關、轉換開關的配置情況及作用

在PLC的I/O接線圖中有許多行程開關和轉換開關,以及壓力繼電器、溫度繼電器等,這些電器元件沒有吸引線圈,它們的觸點的動作是依靠外力或其他因素實現的,因此必須先把引起這些觸點動作的外力或因素找到。其中行程開關由機械聯動機構來觸壓或松開,(文章來源:http://www.dqjsw.com.cn)而轉換開關一般由手工操作,從而使這些行程開關、轉換開關的觸點在設備運行過程中便處于不同的工作狀態,即觸點的閉合、斷開情況不同,以滿足不同的控制要求,這是看圖過程中的一個關鍵。

這些行程開關、轉換開關的觸點的不同工作狀態單憑看電路圖難以搞清楚,必須結合設備說明書、電器元件明細表,明確該行程開關、轉換開關的用途,操縱行程開關的機械聯動機構,觸點在不同的閉合或斷開狀態下電路的工作狀態等。

(2) 采用逆讀溯源法將多負載(如多電動機電路)分解為單負載(如單電動機)電路

根據主電路中控制負載的控制電器的主觸點文字符號,在PLC的I/O接線圖中找出控制該負載的接觸器線圈的輸出繼電器,再在梯形圖和指令語句表中找出控制該輸出繼電器的線圈及其相關電路,這就是控制該負載的局部電路。

在梯形圖和指令語句表中,很容易找到該輸出繼電器的線圈電路及其得電、失電條件,但引起該線圈的得電、失電及其相關電路就不容易找到,可采用逆讀溯源法去尋找:

1) 在輸出繼電器線圈電路中串、并聯的其他編程元件觸點的閉合、斷開就是該輸出繼電器得電、失電的條件。

2) 由這些觸點再找出它們的線圈電路及其相關電路,在這些線圈電路中還會有其他接觸器、繼電器的觸點……

3) 如此找下去,直到找到輸入繼電器(主令電器)為止。

值得注意的是:當某編程元件得電吸合或失電釋放后,應該把該編程元件的所有觸點所帶動的前、后級編程元件的作用狀態全部找出,不得遺漏。

找出某編程元件在其他電路中的動合觸點、動斷觸點,這些觸點為其他編程元件的得電、失電提供條件或者為互鎖、聯鎖提供條件,引起其他電器元件動作,驅動執行電器。

(3) 將單負載電路進一步分解

控制單負載的局部電路可能仍然很復雜,還需要進一步分解,直至分解為基本單元電路。

(4) 分解電路的注意事項

1) 若電動機主軸接有速度繼電器,則該電動機按速度控制原則組成停車制動電路。

2) 若電動機主電路中接有整流器,表明該電動機采用能耗制動停車電路。

(5) 集零為整,綜合分析

把基本單元電路串起來,采用順讀跟蹤法分析整個電路。

三、 識讀梯形圖的具體方法

識讀PLC梯形圖和語句表的過程同PLC掃描用戶過程一樣,從左到右、自上而下,按程序段的順序逐段識圖。

值得指出的是:在程序的執行過程中,在同一周期內,前面的邏輯運算結果影響后面的觸點,即執行的程序用到前面的最新中間運算結果。但在同一周其內,后面的邏輯運算結果不影響前面的邏輯關系。該掃描周期內除輸入繼電器以外的所有內部繼電器的最終狀態(線圈導通與否、觸點通斷與否)將影響下一個掃描周期各觸點的通與斷。

由于許多讀者對繼電器接觸器控制電路比較熟悉,因此建議沿用識讀繼電器接觸器控制電路查線讀圖法,按下列步驟來看梯形圖:

1) 根據I/O設備及PLC的I/O分配表和梯形圖,找出輸入、輸出繼電器,并給出與繼電器接觸器控制電路相對應的文字代號。

2) 將相應輸入設備、輸出設備的文字代號標注在梯形圖編程元件線圈及其觸點旁。

3) 將梯形圖分解成若干基本單元,每一個基本單元可以是梯形圖的一個程序段(包含一個輸出元件)或幾個程序段(包含幾個輸出元件),而每個基本單元相當于繼電器接觸器控制電路的一個分支電路。

4) 可對每一梯級畫出其對應的繼電器接觸器控制電路。

5) 某編程元件得電,其所有動合觸點均閉合、動斷觸點均斷開。某編程元件失電,其所有已閉合的動合觸點均斷開(復位),所有已斷開的動斷觸點均閉合(復位)。因此編程元件得電、失電后,要找出其所有的動合觸點、動斷觸點,分析其對相應編程元件的影響。

6) 一般來說,可從第一個程序段的第一自然行開始識讀梯形圖。第一自然行為程序啟動行。按啟動按鈕,接通某輸入繼電器,該輸入繼電器的所有動合觸點均閉合,動斷觸點均斷開。

再找出受該輸入繼電器動合觸點閉合、動斷觸點斷開影響的編程元件,并分析使這些編程元件產生什么動作,進而確定這些編程元件的功能。值得注意的是:這些編程元件有的可能立即得電動作,有的并不立即動作而只是為其得電動作做準備。

由PLC的工作原理可知,當輸入端接動合觸點,在PLC工作時,若輸入端的動合觸點閉合,則對應于該輸入端子的輸入繼電器線圈得電,它的動合觸點閉合、動斷觸點斷開;當輸入端接動斷觸點且在PLC工作時,若輸入端的動斷觸點未動作,(文章來源:http://www.dqjsw.com.cn)則對應于該輸入端的輸入繼電器線圈得電,它的動合觸點閉合、動斷觸點斷開。如果該動斷觸點與輸出繼電器線圈串聯,則輸出繼電器線圈不能得電。因而,用PLC控制電動機的啟停,如果停止按鈕用動斷觸點,則與控制電動機的接觸器相接的PLC輸出繼電器線圈應與停止按鈕相接的輸入端子相對應的動合觸點串聯。在繼電接觸控制中,停止按鈕和熱繼電器均用動斷觸點,為了與繼電接觸控制的控制電路相一致,在PLC梯形圖中,同樣也用動斷觸點,這樣一來,與輸入端相接的停止按鈕和熱繼電器觸點就必須用動合觸點。在識讀程序時必須注意這一點。

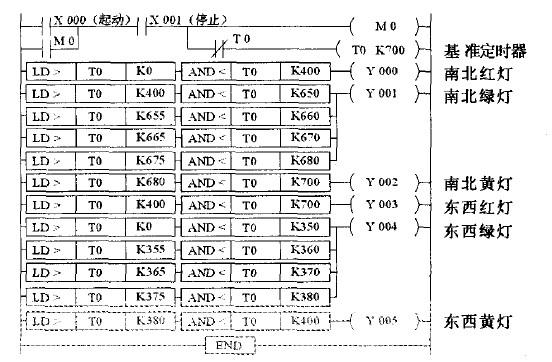

四、 識讀PLC梯形圖的示例

在分析PLC控制系統的功能時,可以將它想象成一個繼電器控制系統中的控制箱,其外部接線圖描述了這個控制箱的外部接線,梯形圖或語句表是這個控制箱的內部“線路圖”,梯形圖中的輸入繼電器和輸出繼電器是這個控制箱與外部世界聯系的“接口繼電器”,這樣就可以用分析繼電器電路圖的方法來分析PLC控制系統。在分析時可以將梯形圖中輸入繼電器的觸點想象成對應的外部輸入器件的觸點或電路,將輸出繼電器的線圈想象成對應的外部負載的線圈。外部負載的線圈除了受梯形圖的控制外,還可能受外部觸點的控制。

電子發燒友App

電子發燒友App

評論