今天看《集成電路時(shí)序分析與建模》中看到這么一個(gè)知識(shí)點(diǎn),覺(jué)得有點(diǎn)意思,就記錄下來(lái),與大家一起分享。

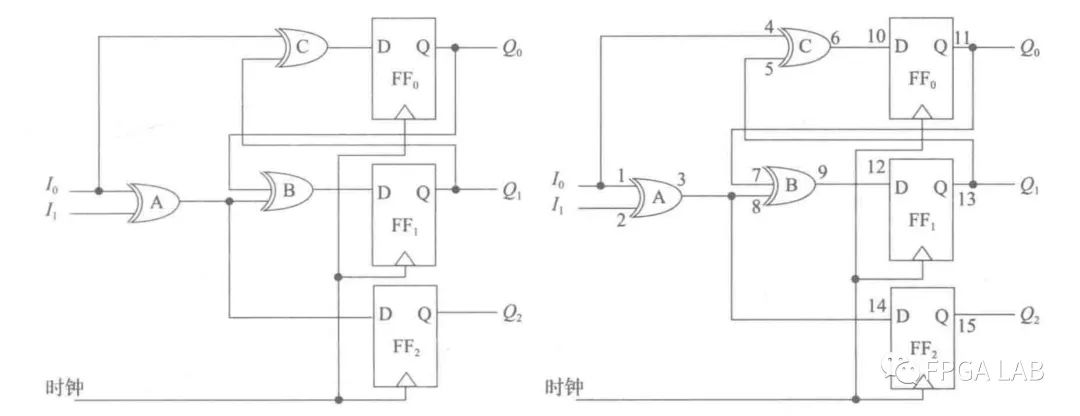

先看 如下電路圖:

左邊的電路圖是需要分析的電路,我們的目的是要對(duì)此電路進(jìn)行時(shí)序分析,那首先要找到該電路需要分析的時(shí)序路徑,既然找路徑,那找到時(shí)序分析的起點(diǎn)與終點(diǎn)即可。

尋找時(shí)序路徑的起點(diǎn)和終點(diǎn)的原則如下:

起點(diǎn):

設(shè)計(jì)邊界的數(shù)據(jù)輸入端口或信號(hào)輸入端口;如上圖右邊的I0,I1;

時(shí)序元件(一般指DFF)的輸出,例如上圖右邊的11,13,15;

存儲(chǔ)單元的數(shù)據(jù)輸出,其實(shí)這和第2條一致,時(shí)序單元也是存儲(chǔ)單元,例如DFF,但這里的存儲(chǔ)單元一般指存儲(chǔ)器,例如RAM等;

終點(diǎn):

時(shí)序單元的數(shù)據(jù)輸入,例如上圖右邊的10,12,14;

存儲(chǔ)單元的數(shù)據(jù)輸入,類(lèi)似于時(shí)序單元,但更多指存儲(chǔ)器等,例如RAM等;

設(shè)計(jì)邊界的輸出Q0,Q1,Q2;

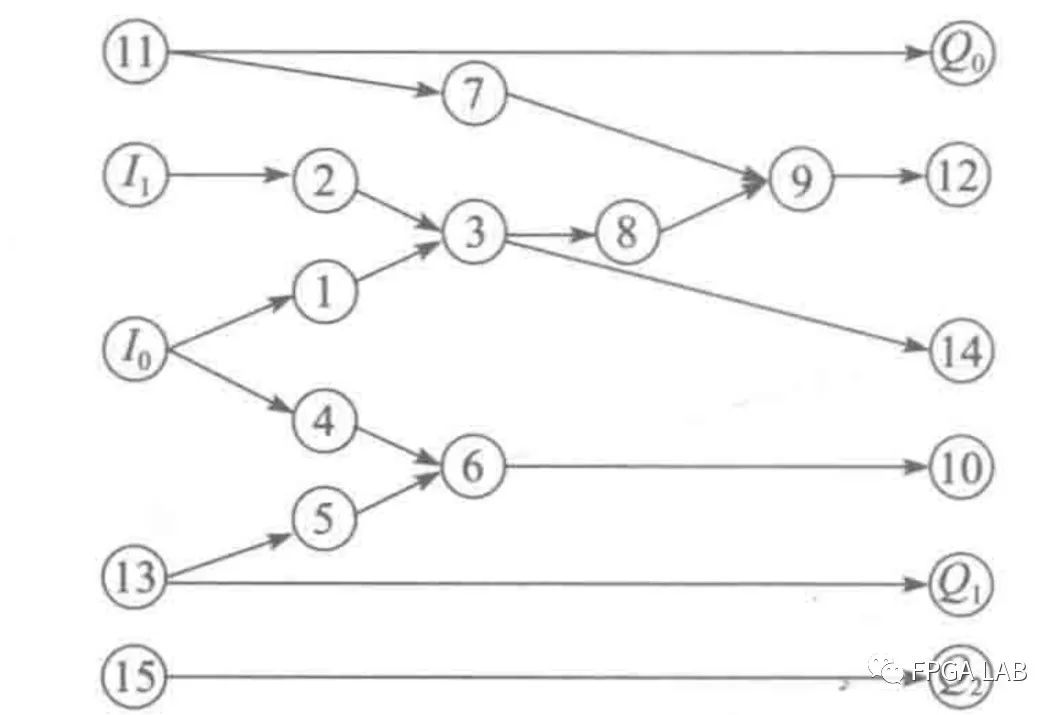

根據(jù)上述原則即可得到,時(shí)序分析的起點(diǎn)(最左邊)和終點(diǎn)(最右邊):

時(shí)序路徑

中間經(jīng)過(guò)的節(jié)點(diǎn)都可認(rèn)為是延遲單元。

實(shí)際進(jìn)行時(shí)序分析時(shí),可不必每次都這么轉(zhuǎn)換,但是不得不說(shuō),這種理論化的方式可以讓你的分析更具理論支撐,見(jiàn)多了熟悉了之后便可更快速的識(shí)別時(shí)序路徑。這是分析的第一步,祝入門(mén)快樂(lè)。

審核編輯 :李倩

-

集成電路

+關(guān)注

關(guān)注

5452文章

12571瀏覽量

374518 -

時(shí)序

+關(guān)注

關(guān)注

5文章

406瀏覽量

38853

原文標(biāo)題:【靜態(tài)時(shí)序分析】如何尋找時(shí)序路徑的起點(diǎn)與終點(diǎn)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

RGB時(shí)序燈條的工作原理講解

輸入引腳時(shí)鐘約束_Xilinx FPGA編程技巧-常用時(shí)序約束詳解

數(shù)字IC/FPGA設(shè)計(jì)中的時(shí)序優(yōu)化方法

vivado時(shí)序分析相關(guān)經(jīng)驗(yàn)

E203內(nèi)核移植到FPGA開(kāi)發(fā)板時(shí)出現(xiàn)時(shí)序違例的解決方式

時(shí)序約束問(wèn)題的解決辦法

喬遷大吉!新起點(diǎn),新征程

設(shè)備管理系統(tǒng)部署后效果不佳?5大核心問(wèn)題與落地解決方案

倍加福推出新型PGV視覺(jué)引導(dǎo)定位系統(tǒng)

智能路徑調(diào)度:AI驅(qū)動(dòng)負(fù)載均衡的異常路徑治理實(shí)踐

Pico示波器在電源時(shí)序測(cè)試中的應(yīng)用

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

一文詳解Vivado時(shí)序約束

AXI握手時(shí)序優(yōu)化—pipeline緩沖器

如何尋找時(shí)序路徑的起點(diǎn)與終點(diǎn)

如何尋找時(shí)序路徑的起點(diǎn)與終點(diǎn)

評(píng)論