本文介紹了一種基于NIOS II軟核處理器實現對LCD-LQ057Q3DC02控制的新方法。在設計中利用FPGA的Altera的SOPC Builder定制NIOS II軟核處理器及其與顯示功能相關的“軟” 硬件模塊來協同實現顯示控

2011-11-09 11:30:07 2304

2304

本帖最后由 forele 于 2015-1-16 22:11 編輯

Nios Ⅱ嵌入式處理器是ALTERA公司推出的采用哈佛結構、具有32位指令集的第二代片上可編程的軟核處理器, 其最大優勢

2015-01-16 22:10:42

Imagination Technologies 宣布,該公司的64位MIPS架構已獲得面向下一代企業、數據中心與服務提供商基礎架構等應用的Cavium新款低功耗OCTEON? III SoC處理器的采用。

2020-05-14 07:21:46

NIOS 軟核讀SD卡源碼 IDE 7[1].2下通過 (1)

2012-08-12 15:22:12

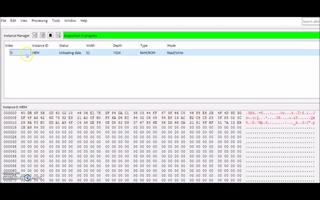

處理器上實現SD卡的讀寫。過程可以分為3個大的步驟:初始化sd卡、寫sd卡、讀sd卡。3.3.1.工作條件檢測卡在識別模式下的命令流程如圖3.1所示(英文版見標準SD卡協議P24)圖3.1 卡在識別模式下

2018-07-17 15:06:25

ARM具有哪幾種模式?ARM里寄存器、MMU是什么意思?ARM920T中有哪幾類地址?ARM處理器的架構及命名規則是什么?

2021-10-21 06:40:00

什么是ARM系列微處理器軟件架構工具?ARM系列微處理器軟件架構工具有哪些特征?

2021-11-05 06:40:18

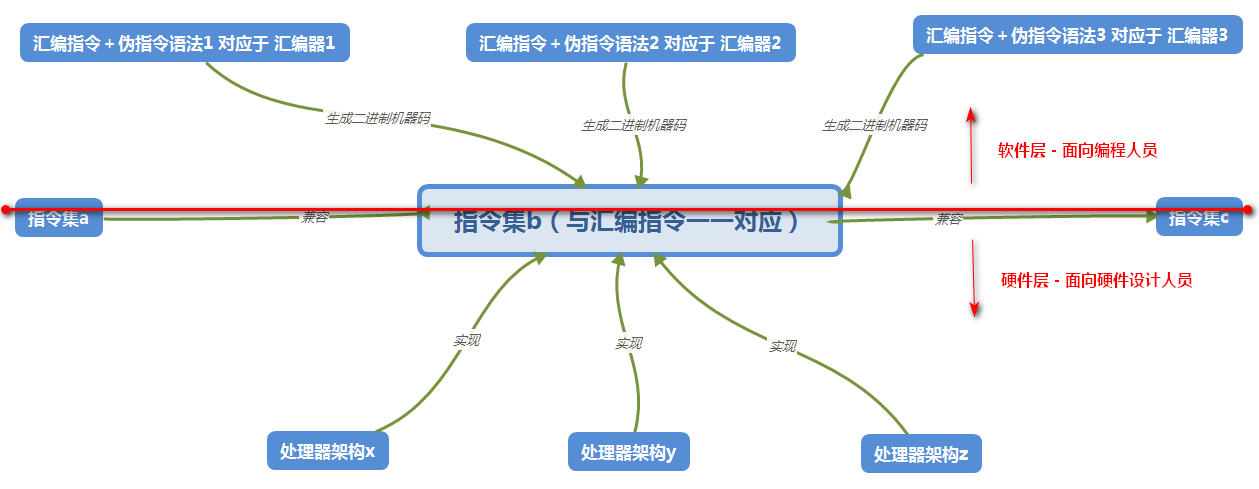

Cortex系列處理器是從ARM哪個架構開始的?arm架構和x86架構有什么區別?體系結構、指令、指令集之間的區別是什么?

2021-07-06 10:49:35

在其業內領先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎上,Altera現在推出了第二代產品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

1 引言 提到微處理器大家都會想到Intel公司和AMD公司的產品,但在當今嵌入式系統 應用 中還有一個同樣響亮的名字ARM微處理器,它是一種RISC 架構下嵌入式系統的核心部件,被廣泛地應用到 工業 控制、無線通訊、消費類 電子 產品等很多領域。

2019-07-15 06:49:14

“SHARC”是超級哈佛架構(Super Harvard ARChitecture)的縮寫,是ADI公司為他們的浮點處理器起的名字。

2020-03-12 09:00:16

得不使用microblaze作為圖像處理的處理器,不知道但不確定在哪里處理。我也查看了本機sd界面,但我明白這樣做需要許可嗎?我已經查看了logicbrick sdhc卡控制器,但我又知道它有一個與它相關的許可證。

2020-03-30 06:31:45

,不同位數的音頻數據7.BMP圖片的制作,以及在不同處理器架構下的處理,在SD卡存儲方式和取模出來的數據的不同現在分別介紹不同模塊的實現問題:一.首先最開始要實現的是音頻數據的播放音頻具有很多編碼,WAV

2012-04-25 15:25:45

第一章復習要點①微處理器 p12②微型計算機p13③總線微處理器:一般也稱中央處理器(CPU),是本身具有運算能力和控制功能,是微型計算機的核心。微處理器:由運算器,控制器和寄存器陣列組成!以及片

2021-07-22 06:48:44

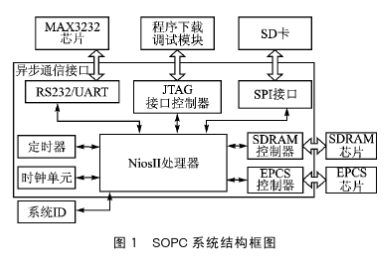

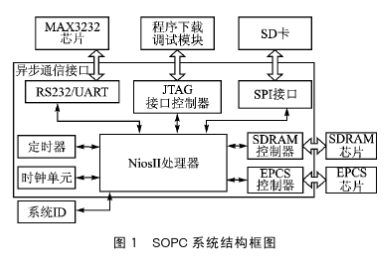

基于NIOS II 軟核處理器的SOPC 技術摘要:介紹了基于NIOS II 軟核處理器的SOPC 技術,分析了傳統方法和基于SOPC 技術的方法實現擴頻收發機的優劣,詳細說明了嵌有雙NIOS II

2009-10-06 15:05:24

大小核(big.LITTLE)晶片設計架構正快速崛起。在安謀國際(ARM)全力推廣下,已有不少行動處理器開發商推出采用big.LITTLE架構的新方案,期透過讓大小核心分別處理最適合的運算任務,達到兼顧最佳效能與節能效果的目的,以獲得更多行動裝置制造商青睞。

2019-09-02 07:24:33

SOPC技術是什么?多媒體廣告系統是由哪些構成的?如何利用Nios II處理器去設計多媒體廣告系統?

2021-04-08 06:23:49

如何利用ARM9處理器如何設計一種SD卡電路呢?

2022-07-19 14:24:57

嵌入式處理器原理及應用 Nios系統設計和C語言編程 294頁 17.9M

2016-09-28 08:44:02

嵌入式處理器原理及應用 Nios系統設計和C語言編程 294頁 17.9M

2016-09-29 08:45:16

哪位大神可以寫基于NIOS 2的sd卡驅動單元的程序,實現卡的讀寫

2016-05-14 13:01:48

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

求解答:除了TI、高通、FSL、三星、STE,還有哪些公司有開發ARM架構的應用處理器?最好是在國內有AE或FAE的,急等答案~~ 謝謝謝謝~~

2013-01-31 15:29:33

,新的 Cortex-M處理器家族設計的非常容易使用。因此,ARM 微控制器處理器在單片機和深度嵌入式系統市場非常成功和受歡迎。二、ARM三個系列處理器特點三、目前,有哪些處理器是應用「ARM 架構」進行

2020-08-18 12:04:06

第05章 Nios Ⅱ嵌入式處理器設計 242頁 1.5M

2016-09-27 08:50:50

請問一下ARM處理器與架構對應的關系是什么?

2021-11-04 07:51:15

片上Nios Ⅱ嵌入式軟核多處理器系統具有哪些優勢?如何實現片上嵌入式Nios Ⅱ軟核六處理器系統的設計?

2021-04-19 08:17:09

請問軟處理器屬不屬于IP core呀?比如MicroBlaze、Nios ii這些。

2014-11-08 18:47:00

的體積和布線難度,其設計方式正在受到越來越多設計者的重視。本文介紹的系統達到了預期目的,完成了基于NIOSⅡ軟核微處理器的應用設計,可以很方便的應用于PCI總線微處理器中。隨著新一代NIOS軟核處理器

2019-04-29 07:00:06

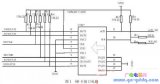

的硬件電路SD卡采用SPI總線方式與處理器連接,其電路原理如圖2所示。圖2 SD 卡接口電路圖1.5 NiosII的構建過程首先要考慮到的是使用什么樣的Nios II,Nios II分為幾個等級,有標準

2019-05-29 05:00:04

sd卡/tf卡速度測試軟件一個很小的軟件,用來測試TF卡SD卡和讀卡器的存儲速度。

2009-03-21 21:34:36 247

247 針對將uClinux 向NIOS 處理器移植過程中的啟動加載程序U-Boot bootloader 進行研究。首先介紹移植的步驟,然后利用bootloader 的設計思想,著重討論U-boot 在NIOS 中的設計與實現,最后對U-boo

2009-04-15 09:41:51 16

16 針對將uClinux 向NIOS 處理器移植過程中的啟動加載程序U-Boot bootloader 進行研究。首先介紹移植的步驟,然后利用bootloader 的設計思想,著重討論U-boot 在NIOS 中的設計與實現,最后對U-boo

2009-05-16 14:28:18 16

16 本文提出了一種全新的總線可重配置的多處理器架構。該架構結合了多核與可重配置處理器的優勢,具有并行性高、計算能力強、結構復雜度低并且應用領域廣泛靈活的特點。對

2009-06-13 14:11:04 11

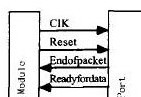

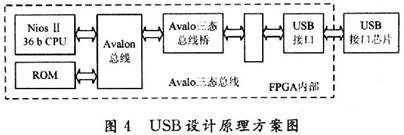

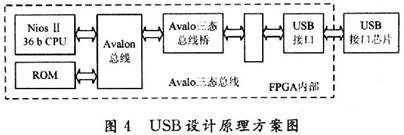

11 本文以Nios II 嵌入式軟處理器為核心,利用USB 控制芯片CH372,設計了基于Nios II 嵌入式軟處理器的USB 通信接口。本文重點介紹了USB 接口的硬件實現方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 SD卡總線拓撲及連接電路圖:本SD卡高度集成閃存,具備串行和隨機存取能力。可以通過專用優化速度的串行接口訪問,數據傳輸可靠。接口允許幾個卡垛疊,通過他們的外部連接。接

2009-11-01 15:23:26 141

141 SPI模式下SD卡驅動的設計與實現

SD卡以其優越的性能在嵌入式設備上得到廣泛的應用。介紹在 S1C33L05 處理器上利用 SPI總線進行 SD 卡的功能擴展。首先介紹具體

2010-02-11 08:50:27 240

240 以NIOS處理器為核心之RFID卡片閱讀機的研制

本論

2010-03-22 10:26:00 18

18 Nios II 嵌入式處理器 7.1 的新特性

2010-08-04 14:40:01 4

4 利用SD卡研究、設計一種大容量心電存儲及回放系統。系統基于高速低功耗的msp430單片機,利用串行外圍接口總線與SD卡相連,實現對sD卡的數據讀寫。為方便微處理器和pc機對sD卡

2010-10-20 16:07:43 814

814 SD卡詳細介紹

SD卡(Secure Digital Memory Card)是一種基于半導體快閃記憶器的新一代記憶設備。SD卡由

2009-04-12 12:30:26 1915

1915 摘要: 針對將uClinux向Nios處理器移植過程中的啟動加載程序U-boot bootloader進行研究。首先介紹移植的步驟,然后利用bootloader的設計思想,著重討論U-boot在Nios中的設計與實

2009-06-20 15:27:23 1222

1222

RAID卡的處理器 處理器描述了RAID卡核心處理芯片的名稱或者說是工作速度。目前市場上銷售的RAID控制卡

2010-01-09 10:44:10 1202

1202 NIOS II的特性及開發設計流程

NIOS的主要特點NIOS II是一個用戶可配置的通用RISC嵌入式處理器。Altera推出的NIOS II系列嵌入式處理器擴展了目前

2010-02-08 14:47:31 2100

2100 0 引言

本文采用了基于NiosⅡ軟核處理器的SOPC技術來實現數碼相框的設計,從根本上改變了傳統設計方案的不足。NiosⅡ軟核嵌入式處理器是Altera公司提供的SOPC解決

2010-08-23 10:22:39 1600

1600

基于NiosⅡ的SD

2011-01-06 17:42:45 80

80 摘要: 提出了一種基于ARM 7 處理器S3C44B0X、以SD 卡主控芯片W 86L 388D 為核心的設計方案, 為低端 嵌入式產品提供SD 卡功能。設計出了硬件電路圖, 并分析了SD 卡的控制協議, 給出了相應的軟

2011-03-24 16:11:22 254

254 本文設計了一種以嵌入式微處理器Nios為核心的電纜故障檢測儀,應用A/D器件和FPGA組成可變頻率的高速數據采集系統,利用低壓脈沖反射法原理來實現線纜的斷路、短路、斷路點、短路點

2011-04-23 10:47:07 1382

1382

Nios簡單介紹: Nios II是一個用戶可配置的通用RISC嵌入式處理器。在這兒,我引用了Altera公司關于NiosII的官方介紹: Altera推出的Nios? II系列嵌入式處理器擴展了目前世界上最流行的軟核嵌

2011-05-26 09:11:50 87

87 用一個時鐘在FPGA中計算直方圖,本方案提出了采用 SD 卡存儲配置數據的配置方案,使用了目前嵌入式系統中常見的ARM 微處理器和SD 卡, 不僅降低了成本,而且利用了現有資源,節省了電路板

2011-09-06 11:58:30 2568

2568

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和 Cyclone系列FPGA全面支持Nios II處理器,以

2011-11-30 16:33:33 6663

6663

電子發燒友網核心提示 :與其他軟核處理器相比,世界上越來越多的設計人員使用了Nios II嵌入式處理器,該處理器一直是FPGA和HardCopy ASIC設計的業界標準處理器。NiosII系列嵌入式處理器

2012-10-17 13:50:04 8129

8129 Nios II 系列處理器配置選項:This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 怎樣使用Nios II處理器來構建多處理器系統 Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 通過以太網遠程配置Nios II 處理器 應用筆記 Firmware in embedded hardware systems is frequently updated over

2012-10-17 15:26:18 16

16 電子發燒友網核心提示 :Nios II 嵌入式處理器獨特的優勢是能夠為您的應用選擇合適的系統,包括處理器性能、混合外設以及系統配置等(請參考圖1)。而且,開發平臺還可以幫助您迅

2012-10-17 15:05:03 2699

2699 本設計基于SoPC以NIOSⅡ軟核處理器為控制核心,根據標準的FAT32文件系統規范,完成了對SD卡的基礎操作。該設計雖比硬件讀取占用稍稍多點的資源,但是方便了開發者對嵌入式設備外設

2013-01-04 14:19:34 9890

9890

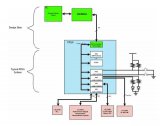

為了實現對嵌入式系統中大量數據存儲的需求,提出了一種基于NIOS II的SD卡存儲系統設計方案,并完成系統的軟硬件設計。該存儲系統使用SPI模式對SD卡進行讀寫訪問,SPI時序由NIOS II的

2013-07-25 16:19:49 66

66 基于NIOSⅡ嵌入式軟核處理器的LCD控制方法研究,很好的設計資料,快來學習吧。

2016-05-09 15:46:27 6

6 SD卡學習資料,感興趣的小伙伴們可以瞧一瞧。

2016-11-22 11:15:44 0

0 只要出現麒麟處理器,那么必定會有很多人糾結于其使用的是ARM的公版架構,或者用之作為麒麟處理器的弱點進行攻擊。那么,在筆者看來,拿采用ARM公版架構來否認麒麟處理器或者否認麒麟處理器的進步是不公平的也是不理智的。

2017-01-04 16:24:00 3763

3763

基于STM32處理器與PCI_1104總線的發電廠故障錄波同步授時卡的設計和實現

2017-09-25 11:15:38 7

7 Nios系統的所有外設都是通過Avalon總線與Nios CPU相接的,Avalon總線是一種協議較為簡單的片內總線,Nios通過Avalon總線與外界進行數據交換。

2018-01-27 22:03:12 5466

5466 。SD卡支持SPI和SD兩種通信模式,S3C2440A具有SD卡接口,支持SD總線模式,所以不再像低端的ARM處理器那樣采用SPI模式,而是采用SD總線模式,這樣可以大大提高SD卡的讀寫速度。

2018-04-07 08:56:00 1793

1793

嵌入式系統的核心是RISC 處理器,具有代表性的RISC軟核處理器是Nios Ⅱ處理器。軟核處理器是指用編程的方法生成的處理器。是一種將硬件邏輯、智能算法、硬件描述語言和編程有機的結合出來,設計處理器硬件電路的新技術。

2018-04-07 09:27:00 1444

1444

許多FPGA設計使用嵌入式處理器實現控制。典型的解決方案是使用Nios這樣的軟處理器,雖然內置硬處理器的FPGASoC也變得很流行了。

2018-05-02 17:38:48 5658

5658

FPGA在嵌入式設計中的應用越來越普遍。了解怎樣采用流行的Nios? II 軟核處理器來輕松開發FPGA嵌入式系統軟件。

在這一5分鐘的視頻中,您將:

觀看Cyclone? III

2018-06-22 02:01:00 5267

5267 使用 Nios II 處理器進行設計”第二部分

2018-06-11 14:36:40 5830

5830

介紹Modular Scatter-Gather DMA IP及如何與 Nios II 處理器搭配使用

2018-06-22 09:38:00 4001

4001

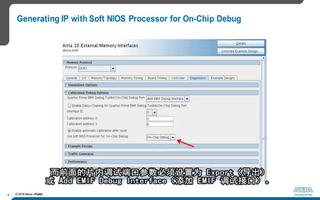

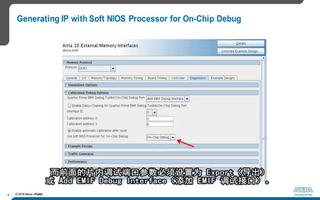

使用片內調試 Nios 軟核處理器

2018-06-20 05:53:00 3888

3888

使用 Nios II 處理器進行設計”第一部分

2018-06-20 00:17:00 4606

4606

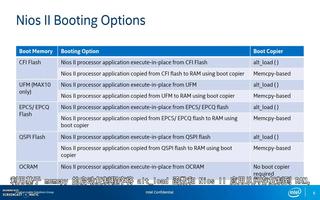

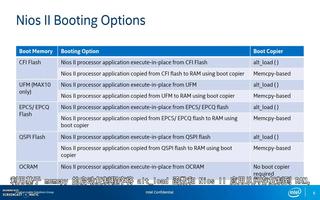

Nios II 處理器的各種啟動方法

2018-06-20 01:22:00 4342

4342

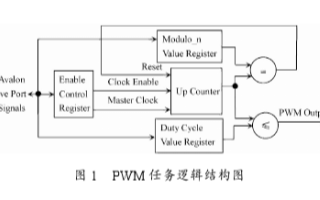

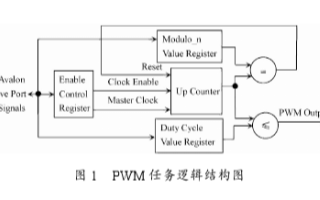

SoPCBuilder環境下加載使用,方便了用戶開發一個自定制的片上系統。本文通過在NiosⅡ嵌入式系統內部集成了基于Avalon總線的脈沖寬度調制(PWM)從外設,介紹了自定制Avalon設備的過程。將其應用在嵌入式智能小車監控系統,為采用NiosII處理器的開發者提供了一些方法和建議。

2020-03-18 08:00:00 2544

2544

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS, Altera的Stratix、Stratix GX、Stratix II和Cyclone系列FPGA全面支持Nios II處理器。

2018-10-31 09:34:00 3058

3058

本文檔的主要內容詳細介紹的是FPGA視頻教程之如何使用NIOS II處理器詳細資料免費下載。

2019-03-20 14:35:26 6

6 本文主要闡述了音頻處理器的架構與音頻處理器延時的調整方法。

2020-04-09 11:01:51 5884

5884 在嵌入式系統或移動設備上使用SD卡,接口的構建和文件系統實現是必須解決的問題。本文探討在CycloneII平臺為基礎的嵌入式系統上,實現SD卡接口和文件系統的實現方法。

2020-07-10 10:19:28 2757

2757

本章將介紹Nios 處理器的硬件開發環境和硬件開發的整個流程。一個簡單Nios 開發系統包括Nios 嵌入式處理器和連接外設的輸入輸出設備, 硬件開發就是利用SOPC Builder 整合處理器

2021-01-15 15:57:49 5

5 Nios 嵌入式處理器是一個優化了的CPU 軟核,用于可編程邏輯器件上的SOPC 設計。Nios 處理器使用了Altera 的SOPC Builder 系統設計工具軟件。SOPC Builder

2021-01-15 15:58:00 1

1 Nios 嵌入式處理器是一個優化了的CPU 軟核,用于可編程邏輯器件上的SOPC 設計。Nios 處理器使用了Altera 的SOPC Builder 系統設計工具軟件。SOPC Builder

2021-01-15 15:58:00 17

17 本教程介紹Altera的Nios R II處理器,這是一種可以在Altera FPGA設備上實例化的軟處理器。描述了NiosⅡ的基本體系結構及其指令集。通過使用Altera的SOPC Builder和Quartus R II軟件,Nios II處理器及其相關的內存和外圍組件可以很容易地實例化。

2021-01-22 15:34:00 7

7 數字設備。為此,本文首先介紹了單片機在SPI協議下與SD卡硬件接口電路,然后簡要闡述了SPI總線模式以及軟件模擬的SPI總線字節傳輸,最后給出了具體實現SD卡的初始化和讀寫的軟件流程。

2021-03-17 16:07:58 50

50 EE-335:將SD卡與Blackfin處理器接口

2021-04-23 09:20:15 8

8 電子發燒友網為你提供NiOSⅡ處理器的Avalon總線架構資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-27 08:54:47 9

9 **SD卡介紹**SD 卡(Seecure Digital Memory Cardl)是一種基于 Flash 的新一代存儲器,具有體積小、容量大、數據傳輸快、移動靈活、安全性能好等優點,是許多便攜式

2021-12-31 19:22:41 17

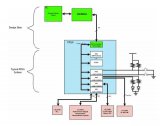

17 許多 FPGA 設計使用嵌入式處理器進行控制。一個典型的解決方案涉及使用 Nios 等軟處理器,盡管帶有內置硬處理器的 FPGA SoC 也變得很流行。圖 1顯示了一個典型的 Altera FPGA

2023-04-08 11:08:03 1650

1650 用于移動應用程序的多媒體處理器 EMMA Mobile1for SD 存儲卡接口

2023-04-20 19:27:09 0

0 大家天天都在使用手機,你知道你的手機使用的什么處理器?處理器又是何種架構呢?今天筆者就來談談處理器的架構和指令集。 我們知道一臺手機最重要的就是處理器,也就是處理器,那么什么是處理器呢? 處理器就是

2023-04-26 11:40:34 8364

8364

電子發燒友網站提供《基于NIOS II的SD卡讀寫控制設計.pdf》資料免費下載

2023-11-06 10:06:43 7

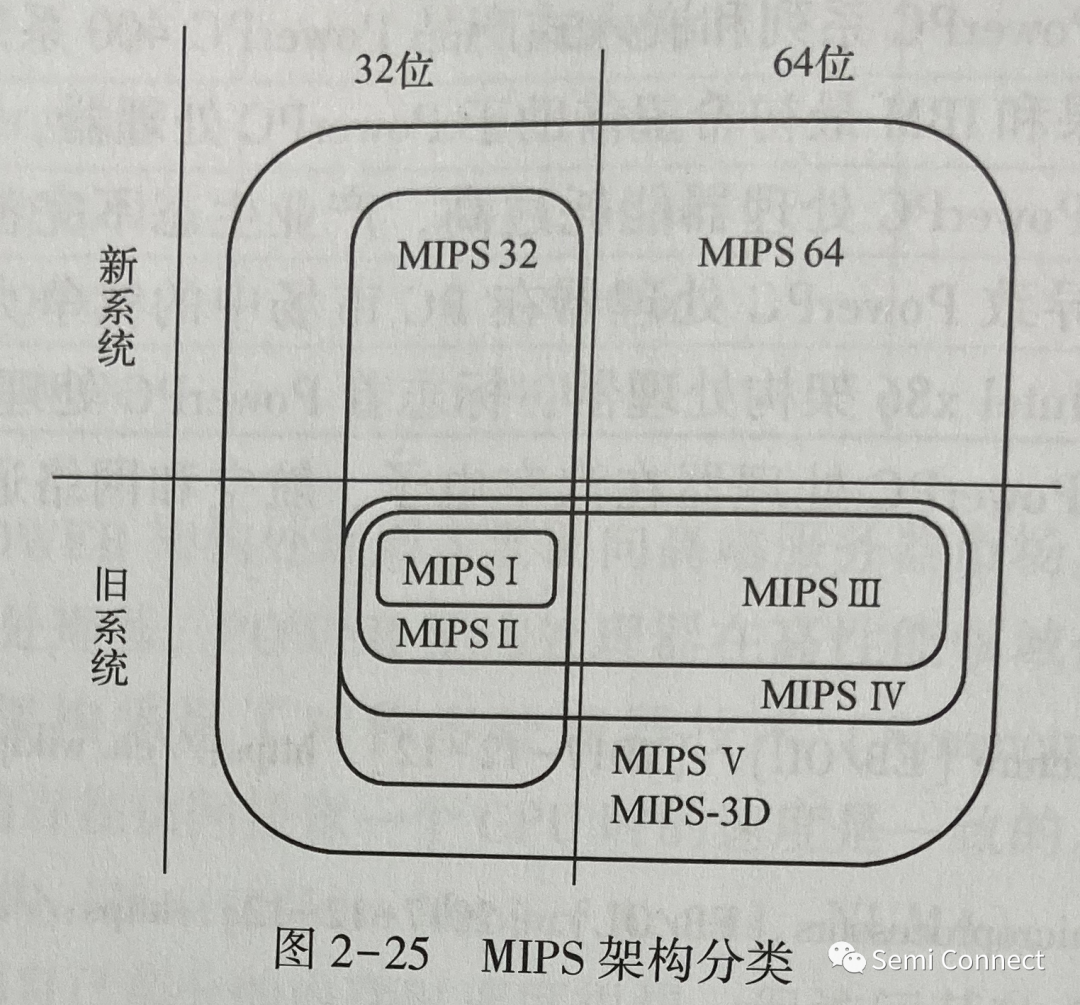

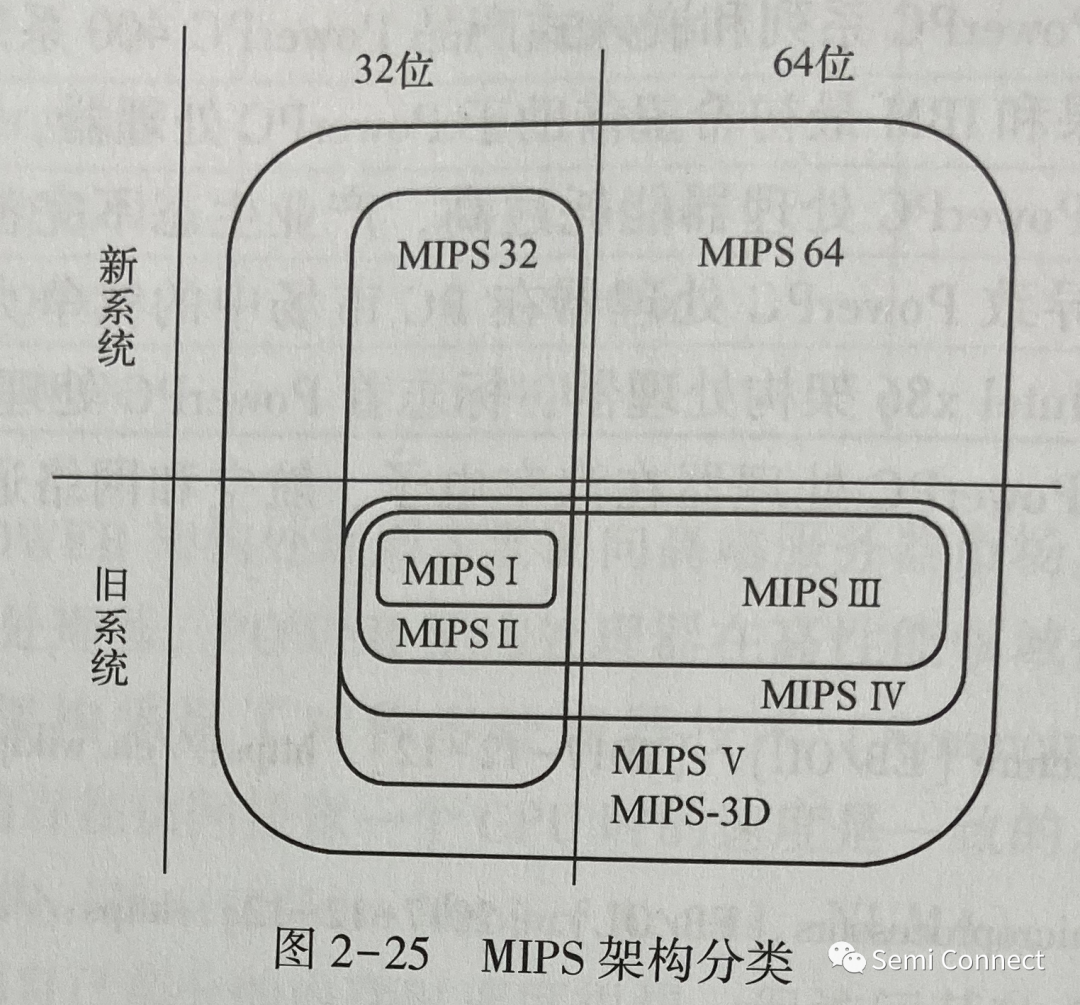

7 無互鎖流水級微處理器 (Microprocessors without Interlocked Pipeline Stages,MIPS) 是流行的 RISC 架構處理器之一。其原理是盡量利用軟件

2023-11-29 09:14:11 3622

3622

SD卡連接器是數字設備中用于連接SD卡的一種硬件接口。隨著數字設備的普及,SD卡已成為存儲數據的一種常見方式。為了方便地將SD卡插入到設備中,SD卡連接器應運而生。 SD卡連接器通常采用金手指

2024-03-04 10:48:29 9092

9092 存儲程序指令和數據。通常包括內部存儲器(如RAM和ROM)和外部擴展存儲器(如閃存、SD卡等)。 總線系統:連接處理器和其他外部設備的通信通道。它可以分為數據總線、地址總線和控制總線,用于傳送數據、地址和控制信號。 定時器模塊:用

2024-04-21 09:55:58 1860

1860 電子發燒友網站提供《EE-335:SD卡與Blackfin處理器的接口.pdf》資料免費下載

2025-01-06 14:15:59 0

0

電子發燒友App

電子發燒友App

評論