Manager定義 在IO-Link規(guī)范中,特別定義了一個(gè)Parameter Manager這個(gè)模塊,它要負(fù)責(zé)處理完整的數(shù)據(jù)檢查以及參數(shù)的

2025-12-12 21:51:31 5768

5768

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog HDL代碼書(shū)寫(xiě)規(guī)范

2017-10-21 20:53:14

1. 目的本規(guī)范的目的是提高書(shū)寫(xiě)代碼的可讀性、可修改性、可重用性,優(yōu)化代碼綜合和仿真的結(jié)果,指導(dǎo)設(shè)計(jì)工程師使用VerilogHDL規(guī)范代碼和優(yōu)化電路,規(guī)范化可編程技術(shù)部的FPGA設(shè)計(jì)輸入,從而做到

2017-12-08 14:36:30

Verilog HDL代碼書(shū)寫(xiě)規(guī)范

2017-09-30 08:55:28

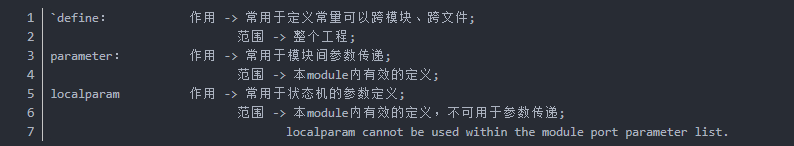

Verilog 預(yù)編譯Verilog 語(yǔ)言支持宏定義(`define),參數(shù) parameter,局域參數(shù)(localparam)以及`include等內(nèi)容。這些數(shù)據(jù)常量的支持極大方便數(shù)字系統(tǒng)

2021-08-11 09:31:48

就可以了。3、作用parameter可以用作例化時(shí)的參數(shù)傳遞。具體方法參見(jiàn)《Verilog例化時(shí)的參數(shù)傳遞》一文在使用狀態(tài)機(jī)時(shí)候區(qū)別挺大的狀態(tài)機(jī)的定義可以用parameter 定義,但是不

2013-04-25 14:32:24

在Verilog定義函數(shù)的時(shí)候,有位寬的定義,我想問(wèn)下諸位大俠,這個(gè)定義可以不要嗎?這個(gè)位寬是不是該函數(shù)處理數(shù)據(jù)的能力的一種?還是有其他用途。請(qǐng)諸位大神賜教

2013-07-20 10:00:56

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog語(yǔ)法基礎(chǔ)講解之參數(shù)化設(shè)計(jì)

2017-10-21 20:56:17

PARAMETERS//*****************************parameter//函數(shù)名、宏定義、參數(shù)定義用大寫(xiě)//*****************************// DEFINE

2015-03-09 20:22:13

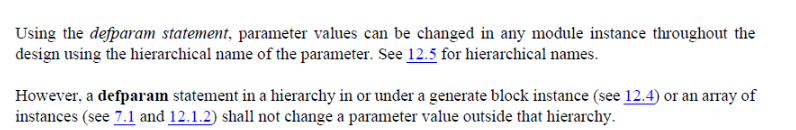

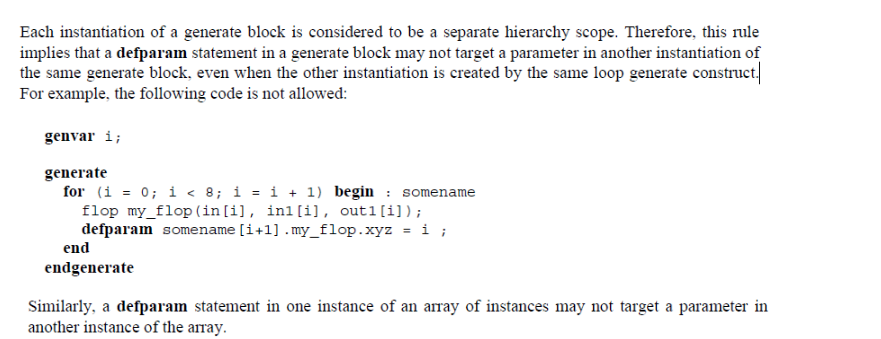

generate為verilog中的生成語(yǔ)句,當(dāng)對(duì)矢量中的多個(gè)位進(jìn)行重復(fù)操作時(shí),或者當(dāng)進(jìn)行多個(gè)模塊的實(shí)例引用的重復(fù)操作時(shí),或者根據(jù)參數(shù)的定義來(lái)確定程序中是否應(yīng)該包含某段Verilog代碼的時(shí)候

2020-12-23 16:59:15

verilog中初值定義 -----initial是否可以被綜合。

2018-09-14 11:49:40

明德?lián)P設(shè)計(jì)規(guī)范對(duì)電路設(shè)計(jì)做了較高的要求,其目就在于用最簡(jiǎn)單的代碼、最簡(jiǎn)潔的方式,設(shè)計(jì)出最易讀、最健壯、最高效的Verilog代碼。按照明德?lián)P設(shè)計(jì)規(guī)范進(jìn)行代碼設(shè)計(jì)的具體要求如下。下面是初學(xué)者學(xué)習(xí)時(shí)定

2015-05-22 17:01:04

`FPGA寶貴實(shí)戰(zhàn)經(jīng)驗(yàn)及Verilog編程規(guī)范`

2013-06-10 12:03:11

此篇將圍繞設(shè)計(jì)操作規(guī)程中的建元件庫(kù)、做元件這一步驟展開(kāi),在此您不但可以學(xué)到PCB元件制作的標(biāo)準(zhǔn)、了解PCB設(shè)計(jì)的操作規(guī)程,讓您的設(shè)計(jì)工作規(guī)范化;同時(shí)還可以學(xué)會(huì)使用PowerPCB軟件做元件的相關(guān)操作方法,最終掌握并達(dá)到通過(guò)PowerPCB來(lái)實(shí)現(xiàn)設(shè)計(jì)標(biāo)準(zhǔn)化的目的。點(diǎn)擊下載

2019-04-29 13:49:28

本文討論了一些System Verilog問(wèn)題以及相關(guān)的SystemVerilog 語(yǔ)言參考手冊(cè)規(guī)范。正確理解這些規(guī)格將有助于System Verilog用戶避免意外的模擬結(jié)果。

2020-12-11 07:19:58

本文討論了一些System Verilog問(wèn)題以及相關(guān)的SystemVerilog 語(yǔ)言參考手冊(cè)規(guī)范。正確理解這些規(guī)格將有助于System Verilog用戶避免意外的模擬結(jié)果。

2020-12-24 07:07:04

PYCPLD的IP 設(shè)計(jì)規(guī)范本文討論建立一種Python的模塊腳本,將verilog語(yǔ)言變成python的程序塊,方便以python的方式來(lái)組織IP,方便應(yīng)用工程師更快的使用IP. 1. 如何將IP

2016-12-12 22:27:39

時(shí)鐘頻率是中代碼計(jì)時(shí)計(jì)數(shù)器的重要參數(shù),為提高代碼的可讀性及移植性,可通過(guò)一個(gè)參數(shù)定義時(shí)鐘頻率參數(shù),請(qǐng)用parameter定義CLK_FRE為50MHz的時(shí)鐘頻率參數(shù)

2023-08-29 09:30:19

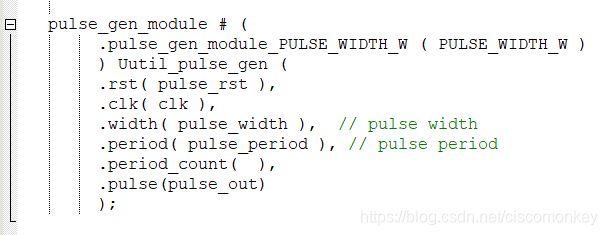

基于上一題目模塊中定義的parameter參數(shù),在例化該模塊時(shí)實(shí)現(xiàn)參數(shù)傳遞

2023-08-30 11:23:51

這幾天一直忙著辦理離職手續(xù),整理以前做的工作,方便交接,小鋼炮的使用就暫時(shí)擱淺了。前面看到 小鋼炮的源碼時(shí),覺(jué)得分類不規(guī)范,看的蛋疼。接合原子的例子,特意重新建了一個(gè)工程。下面是分類:典型的原子風(fēng)格

2016-02-24 15:32:59

FPGA verilog代碼書(shū)寫(xiě)規(guī)范,很好的借鑒

2015-05-21 11:36:27

,參數(shù)定義建議大寫(xiě),另外信號(hào)命名最好體現(xiàn)信號(hào)的含義。規(guī)范建議以下是一些書(shū)寫(xiě)規(guī)范的要求:1、用有意義的有效的名字如sum、cpu_addr等。2、用下劃線區(qū)分詞語(yǔ)組合,如cpu_addr。3、采用一些前綴

2020-09-21 16:48:48

/jishu_524793_1_1.html29【芯航線FPGA學(xué)習(xí)平臺(tái)眾籌進(jìn)度帖】Verilog語(yǔ)法基礎(chǔ)講解之參數(shù)化設(shè)計(jì):https://bbs.elecfans.com/jishu_528770_1_1.html30【連載視頻教程

2015-11-26 10:50:51

的定義和使用,參數(shù)型常數(shù)經(jīng)常用于定義延遲時(shí)間和變量寬度。

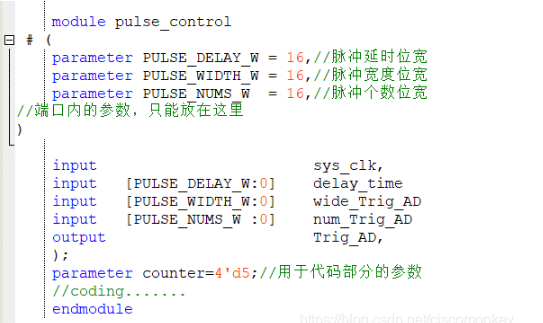

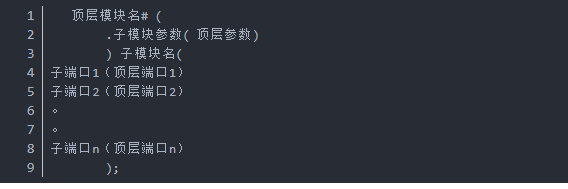

parameter可用作在頂層模塊中例化底層模塊時(shí)傳遞參數(shù)的接口,localparam的作用域僅僅限于當(dāng)前module,不能作為參數(shù)傳遞的接口

2023-05-17 16:26:53

代碼規(guī)范化如何學(xué)習(xí),單片機(jī)也要求規(guī)范化么?

2023-10-12 07:19:17

關(guān)于發(fā)帖標(biāo)題規(guī)范化管理公告由于論壇管理事物繁重,很多時(shí)候由不得我們幾個(gè)管理員的眼睛和手指去處理,為了大家的問(wèn)題能夠更好,更直接的讓各位大大們過(guò)目,讓大家的問(wèn)題都能得到解決,管理員團(tuán)隊(duì)特出發(fā)帖標(biāo)題規(guī)范

2014-11-04 17:11:07

] b; //定義一個(gè)八位的wire數(shù)據(jù)reg [7:0] b; //定義一個(gè)八位的reg數(shù)據(jù)其中。[7:0]表示位寬,只要是整數(shù)就好,當(dāng)然分號(hào)左邊的數(shù)要大于右邊的。4、參數(shù)定義:parameter

2016-03-16 10:45:02

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載34:Verilog代碼書(shū)寫(xiě)規(guī)范特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 雖然沒(méi)有

2017-12-27 09:41:12

求大神給下我單片機(jī)C語(yǔ)言模塊化程序,讓我好好學(xué)習(xí),規(guī)范化我的代碼編寫(xiě)

2013-07-23 14:57:44

很反感很反感很反感很反感

2016-06-27 14:14:17

方式:some.where.else.theSignal.pull()在生成RTL代碼時(shí),會(huì)講該信號(hào)聲明一個(gè)端口鏈接偷穿到我們這一級(jí)的Component。Component參數(shù)化設(shè)計(jì)與我們編寫(xiě)Verilog時(shí)相同,在SpinalHDL里

2022-07-21 14:20:23

有沒(méi)有人對(duì)如何用參數(shù)化加法器樹(shù)編寫(xiě)Verilog有任何建議,輸入參數(shù)是操作數(shù)的數(shù)量?加布里埃爾以上來(lái)自于谷歌翻譯以下為原文Does anyone have any suggestions

2019-04-25 13:28:42

本文檔為作者 在嵌入式和嵌入式 linux C語(yǔ)言的學(xué)習(xí)和工作中所總結(jié)的代碼規(guī)范 ,是作者從 STM32單片機(jī)開(kāi)發(fā)向 Linux C開(kāi)發(fā)的時(shí)候?yàn)榱藬[脫遺留的編碼規(guī)范陋習(xí)而編寫(xiě)的 。因此,本文檔 主要

2020-01-14 10:25:08

電力企業(yè)安全工器具規(guī)范化操作指導(dǎo)系統(tǒng) 一、系統(tǒng)概述 對(duì)電力生產(chǎn)人員來(lái)說(shuō),了解各種安全工器具的性能和用途,正確掌握它們

2010-11-18 14:02:42

》踩到的坑在很早之前,曾寫(xiě)過(guò)如何在SpinalHDL中例化之前用Verilog/SystemVerilog所寫(xiě)的代碼,可參照文章《[SpinalHDL——集成你的RTL代碼]》一文。在

2022-08-31 14:58:31

貼片知識(shí)課堂九,PCB設(shè)計(jì)規(guī)范化第一節(jié)PCB設(shè)計(jì)和生產(chǎn)的關(guān)系到底有多大?這一直是許多工程師懷疑,甚至想弄明白的問(wèn)題!今天麥斯艾姆(massembly)貼片知識(shí)課堂,為廣大工程師朋友直觀地講解一些

2012-09-14 09:24:42

本帖最后由 eehome 于 2013-1-5 10:04 編輯

麥斯艾姆(massembly)貼片知識(shí)課堂十一,PCB設(shè)計(jì)規(guī)范化第三節(jié)麥斯艾姆(massembly)貼片知識(shí)課堂繼續(xù)上次的話

2012-10-31 14:16:16

麥斯艾姆(massembly)貼片知識(shí)課堂十,PCB設(shè)計(jì)規(guī)范化第二節(jié)麥斯艾姆(massembly)貼片知識(shí)課堂繼續(xù)上次的話題“PCB設(shè)計(jì)規(guī)范化”。1, 散熱焊盤(pán),對(duì)于某些功率器件,包括功放,電源

2012-10-31 14:12:59

麥斯艾姆(massembly)貼片知識(shí)課堂十,PCB設(shè)計(jì)規(guī)范化第二節(jié)麥斯艾姆(massembly)貼片知識(shí)課堂繼續(xù)上次的話題“PCB設(shè)計(jì)規(guī)范化”。1, 散熱焊盤(pán),對(duì)于某些功率器件,包括功放,電源

2012-09-18 09:43:27

s-parameter calculator:S參數(shù)計(jì)算工具.input S11,S22,S12,S21等參數(shù),就可以進(jìn)行參數(shù)計(jì)算。

2008-10-23 15:24:23 31

31 利用多項(xiàng)式擬合的規(guī)范化方法來(lái)融合溫度信息,實(shí)現(xiàn)了壓力傳感器的非線性修正和溫漂補(bǔ)償,得到了壓力解析表達(dá)式;同時(shí)利用單片機(jī)進(jìn)行采集和處理信息,實(shí)現(xiàn)了壓力傳感器的

2009-01-07 15:47:26 24

24 Verilog代碼書(shū)寫(xiě)規(guī)范

本規(guī)范的目的是提高書(shū)寫(xiě)代碼的可讀性、可修改性、可重用性,優(yōu)化代碼綜合和仿真的結(jié)果,指導(dǎo)設(shè)計(jì)工程師使用

2010-04-15 09:47:00 106

106 云計(jì)算作為物聯(lián)網(wǎng)快速增長(zhǎng)的重要部分,市場(chǎng)規(guī)模年均復(fù)合增長(zhǎng)達(dá)到91.5%。為更好地完善和建立云計(jì)算服務(wù)市場(chǎng)準(zhǔn)入制度,加快云計(jì)算服務(wù)質(zhì)量、資源整合,云計(jì)算產(chǎn)業(yè)發(fā)展擬定五項(xiàng)規(guī)范化要求。

2013-06-13 17:00:27 810

810 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:43:38 24

24 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:42:02 149

149 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:36:05 35

35 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:31:27 63

63 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:28:34 37

37 verilog代碼規(guī)范,學(xué)會(huì)寫(xiě)代碼還不行,我們需要更加的規(guī)范。

2016-03-25 14:26:26 24

24 適合verilog初學(xué)者的教程,可以好好參考學(xué)習(xí)。

2016-03-25 14:06:32 12

12 適合verilog初學(xué)者的教程,可以好好參考學(xué)習(xí)。

2016-03-25 14:04:35 17

17 適合verilog初學(xué)者的教程,可以好好參考學(xué)習(xí)。

2016-03-25 14:03:14 11

11 本章講述Verilog HDL指定用戶定義原語(yǔ)UDP的能力。UDP的實(shí)例語(yǔ)句與基本門的實(shí)例語(yǔ)句完全相同,即U D P實(shí)例語(yǔ)句的語(yǔ)法與基本門的實(shí)例語(yǔ)句語(yǔ)法一致。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 12

12 在C語(yǔ)言中我們不遵循編譯器就會(huì)報(bào)錯(cuò)的規(guī)定叫規(guī)則;約定成俗但不遵守也不會(huì)出錯(cuò)的規(guī)定叫規(guī)范。比如變量必須先定義后使用,如果我們不定義就直接使用就會(huì)出錯(cuò)。

2016-07-26 15:44:42 5

5 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 華為公司規(guī)范化編程的實(shí)例,值得大家作為編程參考

2016-11-10 11:17:01 18

18 低速電動(dòng)車由于高性價(jià)比,近年來(lái)在三四線城市城郊及鄉(xiāng)鎮(zhèn)農(nóng)村地區(qū)迎來(lái)快速增長(zhǎng),但行業(yè)同時(shí)存在企業(yè)未經(jīng)許可進(jìn)行生產(chǎn)、產(chǎn)品安全性能低、質(zhì)量差等亂象,此次標(biāo)準(zhǔn)制定將促使行業(yè)向規(guī)范化發(fā)展。

2016-11-02 14:48:30 1097

1097 cordic算法verilog實(shí)現(xiàn)(簡(jiǎn)單版)(轉(zhuǎn)載)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0]

2017-02-11 03:06:11 3533

3533

華為的verilog編碼規(guī)范

2017-11-01 08:41:26 41

41 推特文本中包含著大量的非標(biāo)準(zhǔn)詞,這些非標(biāo)準(zhǔn)詞是由人們有意或無(wú)意而創(chuàng)造的。對(duì)很多自然語(yǔ)言處理的任務(wù)而言,預(yù)先對(duì)推特文本進(jìn)行規(guī)范化處理是很有必要的。針對(duì)已有的規(guī)范化系統(tǒng)性能較差的問(wèn)題,提出一種創(chuàng)新的無(wú)

2017-12-15 14:12:59 0

0 (試行)》(以下分別簡(jiǎn)稱為《方案》《規(guī)則》),從調(diào)度操作層面制定了41條消納清潔能源的具體措施,全面落實(shí)國(guó)家及公司關(guān)于清潔能源消納的要求,推動(dòng)能源生產(chǎn)和消費(fèi)革命。這是南方電網(wǎng)首次把清潔能源調(diào)度工作制度化、規(guī)范化。

2018-06-05 14:12:00 1769

1769 在該工程中,國(guó)網(wǎng)河北省電力公司嚴(yán)格落實(shí)規(guī)范化開(kāi)工要求,占地協(xié)調(diào)、林木清理、三線遷改等工程通道補(bǔ)償協(xié)議簽訂及合規(guī)性手續(xù)辦理已全面滿足連續(xù)施工條件。 3月22日,北京西—石家莊1000千伏交流 特高壓

2018-04-07 19:35:00 4457

4457 對(duì)關(guān)系的規(guī)范化是改造關(guān)系模式過(guò)程,首先,根據(jù)一組不同級(jí)別的范式判定關(guān)系的規(guī)范化程度,確定不正常的數(shù)據(jù)依賴關(guān)系,通過(guò)模式分解將一個(gè)低一級(jí)范式的關(guān)系模式,轉(zhuǎn)換為若干個(gè)高一級(jí)的范式的關(guān)系模式的集合,消除其中不合適的數(shù)據(jù)依賴,以解決插入異常、刪除異常、更新異常和數(shù)據(jù)冗余問(wèn)題。

2018-09-05 14:26:00 5

5 設(shè)計(jì)規(guī)范化與自由創(chuàng)作之間沒(méi)有任何矛盾。它只是制約了那些可能出錯(cuò)或者低效的行為,令設(shè)計(jì)思路更加明朗、設(shè)計(jì)效率得到提高、設(shè)計(jì)質(zhì)量充分保證。

2018-10-09 11:10:23 3625

3625 參考鏈接:http://www.fpgaw.com/thread-112099-1-1.html跟李凡老師學(xué)FPGA之VHDL基礎(chǔ)D01(課堂筆記)寄存器要自己猜。阻與不阻隨便來(lái)。常數(shù)當(dāng)作參數(shù)用

2019-07-15 15:35:23 4951

4951 視頻監(jiān)控技術(shù)在公安領(lǐng)域的應(yīng)用由來(lái)已久,是公安破案的主力技術(shù),能夠及時(shí)準(zhǔn)確地為公安人員提供視頻、圖像以及精準(zhǔn)的海量視頻監(jiān)控?cái)?shù)據(jù),幫助公安人員更加快速地找到目標(biāo)人物。近幾年,伴隨著智慧公安建設(shè)的深入開(kāi)展,利用監(jiān)控技術(shù)推動(dòng)公安執(zhí)法規(guī)范化,發(fā)揮著越來(lái)越重要的作用。

2019-08-29 15:02:40 5474

5474 圓滿舉辦。作為注冊(cè)于歐洲的國(guó)際性標(biāo)準(zhǔn)組織,IPEC致力于建立開(kāi)放、透明、公平、公正的光電標(biāo)準(zhǔn)平臺(tái),滿足5G、物聯(lián)網(wǎng)、人工智能等新業(yè)務(wù)對(duì)光互聯(lián)產(chǎn)品規(guī)范化的需求,促進(jìn)光電標(biāo)準(zhǔn)的協(xié)同與創(chuàng)新。

2020-09-10 13:49:59 2330

2330 receive_clk_b; ③ 由parameter定義的常量要求全部字母大寫(xiě),自己定義的參數(shù)、類型用大寫(xiě)標(biāo)識(shí),推薦使用parameter來(lái)定義有實(shí)際意義的常數(shù),包括單位延時(shí)、版本號(hào)、板類型、單板在位信息、LED亮

2020-11-24 12:12:08 4994

4994 AD9650 S-Parameter

2021-01-28 09:56:09 2

2 ADL5725 S-Parameter

2021-03-11 13:11:30 0

0 ADRF6780 S-Parameter

2021-03-11 13:55:32 0

0 時(shí)的檢測(cè)效果不理想。因此,提出一種基于規(guī)范化函欻的深度金字塔模型(Norm-DP)算法,使用規(guī)范化函數(shù)融合可變形部件模型和卷積神經(jīng)網(wǎng)絡(luò)模型,直接從金字塔特征中提取正負(fù)樣本,使用隱變量攴持向量杋進(jìn)行模型訓(xùn)練,結(jié)合柔性非

2021-03-30 14:09:02 14

14 作者 | 濤姐濤哥 鏈接 | cnblogs.com/taojietaoge/p/11575376.html 如何更規(guī)范化編寫(xiě)Java 代碼 Many of the happiest people

2021-08-27 09:31:30 4107

4107 SD規(guī)范之物理層簡(jiǎn)化規(guī)范電子版

2021-09-06 15:29:48 0

0 的完整 Verilog 代碼 。 在這個(gè)FPGA Verilog項(xiàng)目中,一些簡(jiǎn)單的處理操作都是在Verilog中實(shí)現(xiàn)的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 15:50:21 7240

7240 鋼網(wǎng)開(kāi)孔設(shè)計(jì)規(guī)范定義

2021-10-18 11:27:31 14

14 parameter關(guān)鍵字定義模塊特定的參數(shù),該參數(shù)在特定模塊實(shí)例的范圍生效。參數(shù)用于為模塊實(shí)例提供不同的自定義,例如,輸入或輸出端口的寬度。以下是使用parameter關(guān)鍵字的示例:

2022-06-26 10:46:20 1871

1871 在前一章中,我們介紹了Verilog HDL提供的內(nèi)置基本門。本章講述Verilog HDL指定用戶定義原語(yǔ)U D P的能力。

2022-08-08 11:46:46 1616

1616 在實(shí)際工作中,許多公司對(duì)Verilog程序編寫(xiě)規(guī)范都有要求。在公司內(nèi)部統(tǒng)一Verilog程序編寫(xiě)規(guī)范不僅可以增強(qiáng)程序的可讀性、可移植性,而且也有助于邏輯工程師之間交流、溝通,提升邏輯組成員之間的團(tuán)隊(duì)協(xié)作能力。本文就大部分公司常見(jiàn)的Verilog程序編寫(xiě)規(guī)范作一個(gè)介紹。

2022-09-15 09:35:58 4816

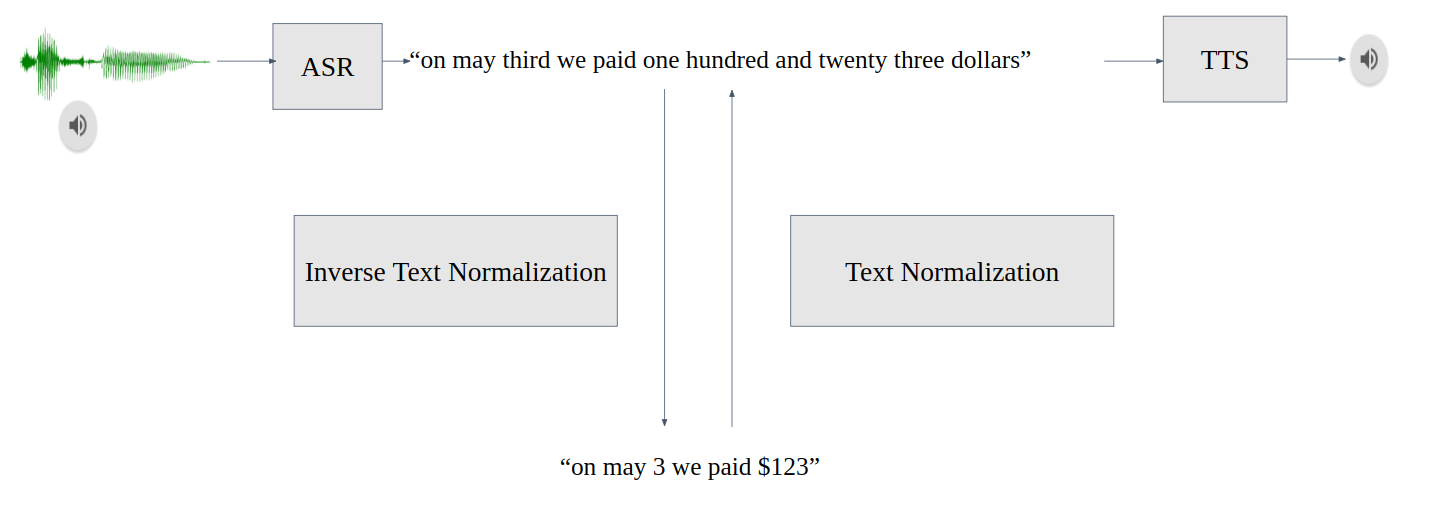

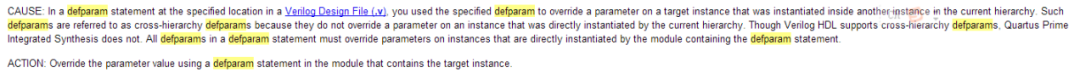

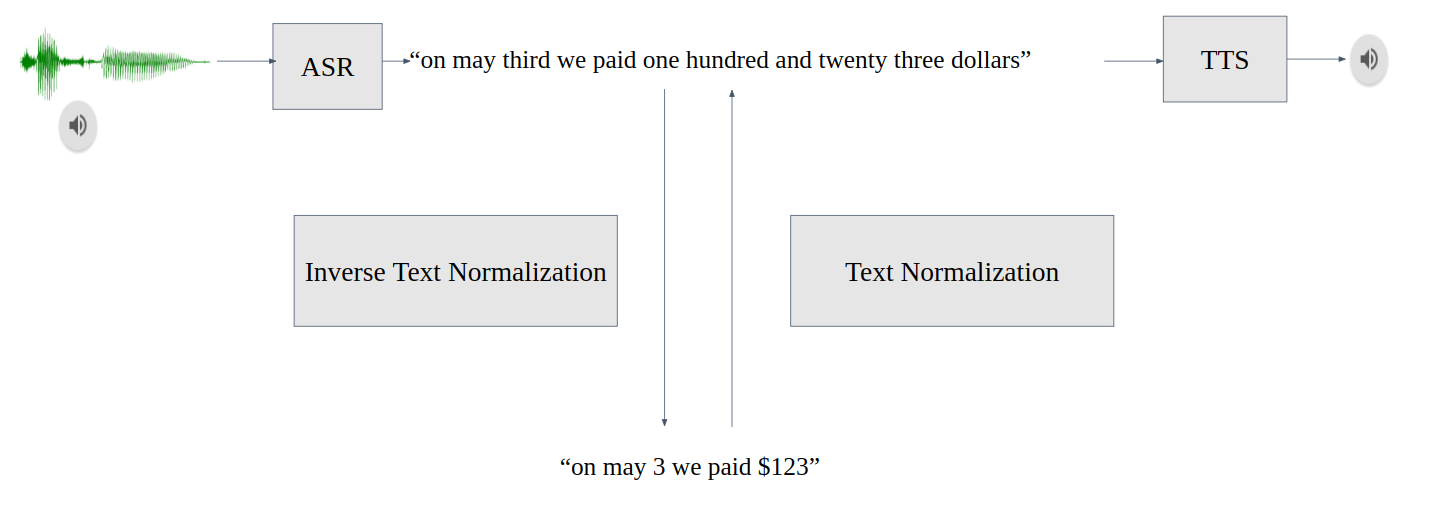

4816 文本規(guī)范化( TN )將文本從書(shū)面形式轉(zhuǎn)換為口頭形式,是文本到語(yǔ)音( TTS )之前的一個(gè)重要預(yù)處理步驟。 TN 確保 TTS 可以處理所有輸入文本,而不會(huì)跳過(guò)未知符號(hào)。例如,“ 123 美元”轉(zhuǎn)換為“一百二十三美元”

2022-10-11 11:41:12 2968

2968

本規(guī)范的目的是提高書(shū)寫(xiě)代碼的可讀性 可修改性 可重用性 優(yōu)化代碼綜合和仿真的結(jié) 果 指導(dǎo)設(shè)計(jì)工程師使用VerilogHDL規(guī)范代碼和優(yōu)化電路 規(guī)范化公司的ASIC設(shè)計(jì)輸入從而做到。

2022-11-23 17:28:18 1907

1907 在testbench中避免使用絕對(duì)的時(shí)間,如#20,#15或#(CYC+15)等,應(yīng)該在文件前面使用parameter定義一些常量,使得時(shí)間的定義象#(CYC+OFF0)的形式,便于修改。

2022-11-25 09:26:41 1863

1863 FPGA 設(shè)計(jì)的硬件語(yǔ)言Verilog中的參數(shù)化有兩種關(guān)鍵詞:define 和 paramerter,參數(shù)化的主要目的是代碼易維護(hù)、易移植和可讀性好。

2022-12-26 09:53:10 1349

1349 ,因?yàn)槲覀兛梢愿p松地將代碼從一個(gè)設(shè)計(jì)移植到另一個(gè)設(shè)計(jì)。

我們?cè)?b class="flag-6" style="color: red">verilog中有兩個(gè)可用的結(jié)構(gòu),可以幫助我們編寫(xiě)可重用的代碼 - 參數(shù)化和generate語(yǔ)句。這兩種結(jié)構(gòu)都允許我們創(chuàng)建更通用的代碼,當(dāng)我們實(shí)例化組件時(shí),我們可以輕松修改這些代碼以滿足我們的需求。

2023-05-11 15:59:21 1759

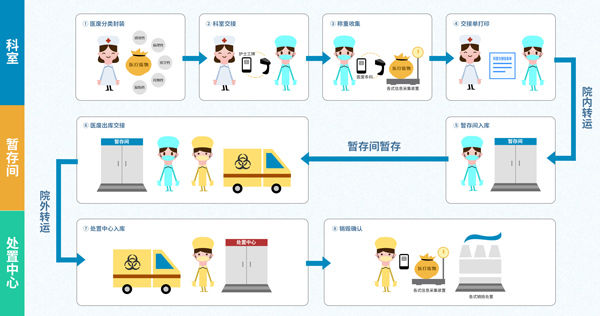

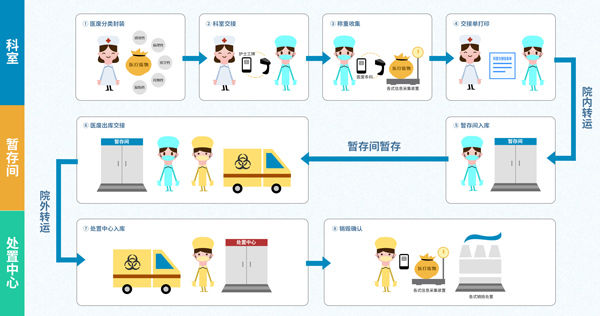

1759 醫(yī)療廢物在線監(jiān)測(cè)系統(tǒng)助力醫(yī)院醫(yī)廢規(guī)范化管理 醫(yī)療廢物在線監(jiān)測(cè)系統(tǒng)的應(yīng)用是預(yù)防疾病傳播、保護(hù)生態(tài)環(huán)境、保障群眾身心健康的重要舉措。通過(guò)建設(shè)醫(yī)療廢物在線監(jiān)測(cè)系統(tǒng),可以完成對(duì)醫(yī)療廢物產(chǎn)生和流轉(zhuǎn)的實(shí)時(shí)信息

2023-05-30 18:02:00 1018

1018

高校低值易耗品管理日益精細(xì)化,做好低值易耗品管理有利于降低成本、提高效率、防止資產(chǎn)流失、確保使用安全等。那么,高校低值易耗品,如何科學(xué)規(guī)范化管理呢?

2022-03-17 09:21:54 731

731

硬件開(kāi)發(fā)的標(biāo)準(zhǔn)化是公司管理過(guò)程中的重要組成部分,它離不開(kāi)硬件開(kāi)發(fā)文檔的規(guī)范化,很多公司并不了解開(kāi)發(fā)文檔的重要性,容易將其忽視。沐渥科技認(rèn)為一個(gè)項(xiàng)目開(kāi)發(fā)完成后,還有著漫長(zhǎng)的生命周期、售后維護(hù)和更新迭代

2022-11-28 19:29:30 1550

1550

硬件電路開(kāi)發(fā)流程是指導(dǎo)硬件工程師按規(guī)范化方式進(jìn)行開(kāi)發(fā)的準(zhǔn)則,規(guī)范了硬件電路開(kāi)發(fā)的全過(guò)程。

2023-08-03 10:31:22 2418

2418

注:以R起頭的是對(duì)編寫(xiě)Verilog代碼的IP設(shè)計(jì)者所做的強(qiáng)制性規(guī)定,以G起頭的條款是建議采用的規(guī)范。每個(gè)設(shè)計(jì)者遵守本規(guī)范可鍛煉命名規(guī)范性。

2023-08-15 16:23:41 3428

3428 Verilog規(guī)范對(duì)于一個(gè)好的IC設(shè)計(jì)至關(guān)重要。

2023-08-17 10:14:07 2500

2500

醫(yī)療廢物管理系統(tǒng)提高醫(yī)廢規(guī)范化管理 醫(yī)療廢物是引起疾病傳播或相關(guān)公共衛(wèi)生問(wèn)題的重要危險(xiǎn)性因素。我國(guó)衛(wèi)生部明確規(guī)定,醫(yī)院里的醫(yī)療廢物必須封閉存儲(chǔ)、定點(diǎn)存放、專人運(yùn)輸,醫(yī)療廢物必須進(jìn)行焚燒處理,以確保

2023-11-22 16:29:17 718

718

移動(dòng)設(shè)備增強(qiáng)現(xiàn)實(shí)系統(tǒng)應(yīng)用接口》正式下達(dá)。 推動(dòng)移動(dòng)設(shè)備增強(qiáng)現(xiàn)實(shí)大規(guī)模、規(guī)范化應(yīng)用 商湯科技一直致力于增強(qiáng)現(xiàn)實(shí)標(biāo)準(zhǔn)化工作,在國(guó)家標(biāo)準(zhǔn)層面,作為增強(qiáng)現(xiàn)實(shí)國(guó)家標(biāo)準(zhǔn)研究組副組長(zhǎng)單位,持續(xù)推動(dòng)增強(qiáng)現(xiàn)實(shí)標(biāo)準(zhǔn)體系建設(shè)。 其中,《信息技

2023-12-27 15:35:02 1431

1431

Verilog 中被廣泛用于對(duì)電路進(jìn)行模塊化設(shè)計(jì),以簡(jiǎn)化和組織代碼。 本文將詳細(xì)介紹 Verilog 函數(shù)的用法,并探討函數(shù)在硬件設(shè)計(jì)中的重要性和實(shí)際應(yīng)用場(chǎng)景。 一. Verilog 函數(shù)概述 Verilog 函數(shù)通過(guò)提供一種結(jié)構(gòu)化的方式來(lái)組織代碼,并可以根據(jù)需要重復(fù)使用。它們可以在模塊內(nèi)部或外部定義,

2024-02-22 15:49:27 8456

8456 在數(shù)字化浪潮的變革中,企業(yè)規(guī)范化管理與人才發(fā)展日益成為行業(yè)關(guān)注的焦點(diǎn)問(wèn)題。3月25日,普元電力召開(kāi)盛大的績(jī)效項(xiàng)目啟動(dòng)會(huì),軟通咨詢作為普元電力績(jī)效項(xiàng)目的合作伙伴受邀出席。

2024-03-27 09:42:10 753

753

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論