賽靈思針對回程應用推出完全自適應千兆位級點對點微波調制解調器IP,此款1024QAM微波調制解調器IP解決方案將完全可編程的硬件和API軟件相結合,支持新一代智能寬帶無線解決方案

2013-02-25 10:05:07 1670

1670 對于這一越來越復雜的情形,需要其他的解決方案。高速串行互聯一直主要用于通信行業,在較長的距離上傳輸數據流。采用高級硅片工藝技術,在很多系統中,這些串行鏈路的接口變得非常小,而數據速率足夠高,多千兆位串行鏈路替代了并行總線,甚至是異步I/O。

2013-03-12 11:41:44 1678

1678 嗨,我對Xilinx ISE中生成的報告有疑問。我有一個設計,我正在檢查綜合和布局和路線報告。我對我的設計進行了一些更改并實施了它。我想檢查更改的啟動和邏輯利用率,但報告是相同的。我嘗試了很多次更改

2019-02-20 07:19:58

描述 PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2022-09-21 07:56:06

描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2018-08-29 08:42:24

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2022-09-27 06:46:35

利用 IBERT 進行 GTX 信號眼圖測試8.5.4.1 概述Vivado中提供了1種IBERT工具用于對Xilinx FPGA芯片的高速串行收發器進行板級硬件測試。通過IBERT我們可...

2021-07-20 07:28:23

、外部中斷1、定時器/計數器0、定時器/計數器1、串行中斷)。通過I/O篇與中斷篇的學習,其實基本學習完51單片機了。應用篇的出現是為了更好的利用單片機去做項目,通過做項目更好的利用單片機中I/O與中斷系統。言歸正傳,開始本文內容。在I/O篇的綜合練習中,矩陣鍵盤用作輸入,單片...

2022-01-27 07:26:05

什么是千兆級LTE?千兆級LTE技術的關鍵特性和實現原理

2020-12-25 06:01:29

電磁兼容方面的問題也更加突出。 信號完整性是指信號在信號線上傳輸的質量,主要問題包括反射、振蕩、時序、地彈和串擾等。信號完整性差不是由某個單一因素導致,而是板級設計中多種因素共同引起。在千兆位設備的PCB

2018-09-11 15:19:49

描述PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2022-09-26 06:32:49

`描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2015-05-11 10:30:22

`描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2015-05-11 10:27:03

約束;

● 利用UltraScale FPGA收發器進行設計;

● 高速存儲接口設計;

● 利用以太網 MAC 控制器進行設計;

● 利用千兆位級串行 I/O 進行

2024-06-05 10:09:53

描述PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2018-09-10 09:02:14

目前,隨著多媒體應用的普及,千兆位以太網已經發展成為主流網絡技術。大到成千上萬人的大型企業,小到幾十人的中小型企業,在建設企業局域網時都會把千兆位以太網技術作為首選的高速網絡技術。千兆位以太網技術甚至正在取代ATM技術,成為城域網建設的主力軍。

2019-10-15 07:57:39

要使用FPGA實現150M的光纖通訊,使用XILINX XAPP244的串行數據恢復功能感覺有些麻煩。使用XILINX的ROCKET I/O 實現150M的光纖通信合適/可行嗎?

2013-03-26 16:06:30

你好,在哪里可以找到有關如何連接zynq和以太網千兆位控制器(ksz9021)的文檔?它是RGMI。這是標準連接嗎?

2020-08-07 10:17:15

可用于基于 EtherCAT 的 PLC 或運動控制應用。EtherCAT 主站在 AM572x 處理器的千兆位以太網和(...)主要特色提供在千兆位開關 (CPSW) 和 PRU-ICSS 以太網端口

2018-12-26 14:40:25

采用串行技術進行高端系統設計已占很大比例。在《EETimes》雜志最近開展的一次問卷調查中,有92%的受訪者表示2006年已開始設計串行I/O系統,而在2005年從事串行設計的僅占64%。 串行技術

2019-04-12 07:00:11

采用串行技術進行高端系統設計已占很大比例。在《EETimes》雜志最近開展的一次問卷調查中,有92%的受訪者表示2006年已開始設計串行I/O系統,而在2005年從事串行設計的僅占64%。串行技術在

2019-04-16 07:00:07

嵌入式測試是什么?如何用FPGA技術去實現嵌入式設計?如何測試FPGA中的高速串行I/O?

2021-04-13 07:03:58

將FPGA內嵌PowerPC硬核處理器、Xilinx精簡嵌入式操作系統Xilkernel,以及相應的外設IP Core相結合,完成嵌入式串行千兆以太網的設計。

2020-04-09 07:57:07

選擇合適的千兆位收發器(GT)是通信和實時處理領域尤其需要重點考慮的設計事項,但特定的市場領域可能會存在太多的標準、協議或使用模型。有時針對某一種應用就會涉及到好幾種標準,為了選擇最適合的千兆位收發器,必須對各種協議的最新發展情況了如指掌。

2019-10-31 06:57:54

你好Xilinx收發器使用CML IOSTANDARD。在xilinx 7系列示例設計中,有固定的GTREFCLK位置,但其他引腳未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引腳未配置CML I / O標準。我如何配置CML I / O標準?

2020-08-13 10:10:53

描述此設計用于對兩個工業級 DP83867IR 千兆位以太網 PHY 和 Sitara? 主機處理器(含集成式以太網 MAC 和交換機)進行性能評估。此設計旨在滿足關于 EMI 和 EMC 的工業

2018-10-08 08:39:10

采用串行技術進行高端系統設計已占很大比例。在《EETimes》雜志最近開展的一次問卷調查中,有92%的受訪者表示2006年已開始設計串行I/O系統,而在2005年從事串行設計的僅占64%。 串行

2019-05-05 09:29:30

怎么實現千兆位以太網用光纖收發器的設計?

2021-05-27 06:32:55

描述PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2018-08-31 08:59:25

隨著802.11n的廣泛部署,企業開始關注千兆位無線LAN。IEEE標準802.11ac和802.11ad(仍在進行中)都計劃在不同的頻道提供千兆位速度的無線LAN。802.11ac被特許在小于6

2019-07-01 07:42:05

用于10千兆位互連分析的Stripline TRL校準裝置

2019-10-09 09:08:56

描述PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流和電壓

2018-08-10 09:36:45

`用于千兆以太網保護的低壓瞬變二極管集成芯片SLVU2.8SLVU2.8-4SLVU2.8-8SLVU2.8系列的設計是為了保護以太網線路。它的低電容使它與千兆位以太網兼容。SLVU2.8-4A1被

2019-11-11 15:22:13

`描述此設計用于對兩個工業級 DP83867IR 千兆位以太網 PHY 和 Sitara? 主機處理器(含集成式以太網 MAC 和交換機)進行性能評估。此設計旨在滿足關于 EMI 和 EMC 的工業

2015-04-27 15:17:16

描述此設計用于對兩個工業級 DP83867IR 千兆位以太網 PHY 和 Sitara? 主機處理器(含集成式以太網 MAC 和交換機)進行性能評估。此設計旨在滿足關于 EMI 和 EMC 的工業

2022-09-21 08:02:24

請問多核架構在微波鏈路上如何實現千兆位傳輸?

2021-04-19 06:57:52

嗨,我們正在設計處理10千兆位流量的邏輯,我們想知道是否有人對基于xilinx的工具包有這樣的開發經驗/建議。謝謝

2019-08-16 10:23:44

選擇合適的FPGA千兆位收發器為什么至關重要?

2021-04-13 06:58:27

輕松實現高速串行I/OFPGA應用設計者指南輸入/輸出(I/O)在計算機和工業應用中一直扮演著關鍵角色。但是,隨著信號處理越來越復雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數據對齊

2020-01-02 12:12:28

本文主要介紹的是均衡千兆位銅纜連接的IC。

2009-04-22 11:36:34 9

9 本文介紹了利用美國WONDERWARE 公司的Wonderware ® FactorySuite™2000 I/O Server Toolkit 如何開發用戶自己的I/O

2009-08-14 09:41:59 39

39 具有串行接口的I/O 擴展器EM83010 及其應用作者:南京大學電子科學與工程系 曹立進 高敦堂 都思丹 孫宗琪 吳 勇 來源:《電子技術應用》摘 要: 介紹了具有串行接口的I/O 擴

2009-11-01 14:41:02 6

6 Cisco Catelyst 6500系列交換機和千兆位以太網幫助思科圣何塞總部適應未來需要

本案例研究介紹了思科IT部門如何在思科總部的網絡中部署Cisco Catelyst 6500系列交換

2010-02-26 08:52:27 15

15 描述 MAX9275/MAX9279是3.12Gbps千兆位多媒體串行鏈路(GMSL)串行器,具有并行LVCMOS輸入和CML串行輸出,可編程用于50ω同軸電纜或100ω屏蔽雙絞線(STP

2023-12-07 10:30:47

摘要: 介紹了采用Videx-ⅡPR0系列FPCA設計的應用于下一代無線通信系統中的高速I/O。由于充分利用芯片中集成的Rocket I/O模塊,并采用差分輸入參考時鐘、

2009-06-20 10:45:35 1632

1632

選擇合適的FPGA千兆位收發器至關重要

選擇合適的千兆位收發器(GT)是通信和實時處理領域尤其需要重點考慮的設計事項,但特定的市場領域可能會存在太多的標準、

2009-11-04 10:05:02 638

638

千兆位設備PCB的信號完整性設計

本文主要討論在千兆位數據傳輸中需考慮的信號完整性設計問題,同時介紹應用PCB設計工具解

2009-11-18 08:59:52 630

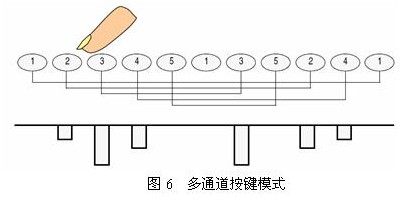

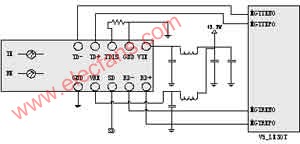

630 利用普通I/O口實現電容觸摸感應方案

技術背景

現在電子產品中,觸摸感應技術日益受到更多關注和應用,不僅美觀

2010-04-22 10:16:16 1952

1952

本文設計的基于Xilinx FPGA的千兆位以太網及E1信號的光纖傳輸系統采用Xilinx XC5VLX30T芯片,通過以太網測試儀和數據誤碼儀對本系

2010-07-06 09:09:10 3060

3060

本文介紹的用 89C51 單片機I/O 口模擬實現串行通信的方法,已成功地應用在某電壓數據采集系統中

2011-06-30 11:25:45 2178

2178 MAX3748多速率限制數據量化為SONET,光纖通道,千兆位以太網光接收器的放大器功能。

2011-08-03 09:49:25 1729

1729

主要介紹了千兆位以太網技術及其在多速率局域網的組網設計、優化方案和運用多種網絡技術的千兆位以太網組網工程實例。全書共9章,內容包括OSI參考模型與TCP/IP協議簡介,以太網基

2012-01-04 15:34:46 0

0 XAPP520將符合2.5V和3.3V I/O標準的7系列FPGA高性能I/O Bank進行連接 The I/Os in Xilinx 7 series FPGAs are classified

2012-01-26 18:47:15 75

75 一名設計工程師怎樣才能真正充分利用串行I/O的各種技術呢?在開始設計之前,我們需要知道什么對于實現串行I/O是有益的。我們需要研究一些基于串行設計的單元器件,從而了解一下

2012-04-01 15:01:36 29

29 I2C串行總線的組成及工作原理的PPT課程

2015-11-16 19:08:17 0

0 Xilinx FPGA工程例子源碼:Xilinx 官方網站提供的一個利用DCT進行圖像壓縮的設計參考

2016-06-07 15:07:45 7

7 PMP9407 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。此設計采用一個 5V 輸入且配有一個

2017-02-08 09:14:00 1123

1123 PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。 它利用一個 PMBus 接口來實現電流和電壓

2017-02-08 09:22:11 734

734 PMP10520 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌(1V/20A、 1.2V/30A

2017-02-08 15:59:50 1377

1377 Xilinx? 更新語言課程: ? 使用 ?VHDL? 進行設計 、 ? 高級 ?VHDL? 、 使用 ?Verilog? 進行設計 ? 、 使用 ?SystemVerilog? 進行

2017-02-09 02:18:11 313

313 片上的數據也越來越多。數據必須經過緩存,然后再次以DDR存儲器形式通過并行I/O或以串行存儲器標準(如混合內存立方體(HMC)和MoSys 帶寬引擎)形式再次通過串行I/O。數據從并行和串行I/O返回后,在傳送到下個目的地之前必須在邏輯和DSP中進行處理。

2018-07-12 14:33:00 2060

2060

隨著802.11n的廣泛部署,企業開始關注千兆位無線LAN。IEEE標準802.11ac和802.11ad(仍在進行中)都計劃在不同的頻道提供千兆位速度的無線LAN。802.11ac被特許在小于6

2017-11-23 06:09:02 1176

1176 進行嵌入式串行千兆以太網開發成為可能。本設計使用Xilinx公司65 nm工藝級別的Virtex5 FXT系列芯片,滿足嵌入式系統設計所應具備的高性能、高密度、低功耗和低成本的要求。

2017-11-23 10:14:46 3913

3913 32mb串行閃存133mhz多I/O SPI和四I/O QPI DTR接口數據手冊

2018-01-30 14:37:50 20

20 此設計符合 EMI 和 EMC 標準,具有寬輸入電壓范圍 (17-60V),采用兩個 DP83867IR 千兆位以太網PHY 和 AM3359 Sitara? 處理器,適用于嚴苛的工業環境。

2018-05-08 16:13:06 28

28 千兆位級串行I/O技術有著極其出色的優越性能,但這些優越的性能是需要條件來保證的,即優秀的信號完整性。例如,有個供應商報告說,他們第一次試圖將高速、千兆位級串行設計用于某種特定應用時,失敗率為90%。為了提高成功率,我們可能需要進行模擬仿真,并采用更復雜的新型旁路電路。

2018-06-20 14:24:00 2817

2817

了解設計人員在使用Zynq-7000 All Programmable SoC器件時可用的不同I / O,從標準I / O到串行收發器以及模擬輸入。

2018-11-26 06:36:00 3345

3345 千兆位級串行I/O技術有著極其出色的優越性能,但這些優越的性能是需要條件來保證的,即優秀的信號完整性。例如,有個供應商報告說,他們第一次試圖將高速、千兆位級串行設計用于某種特定應用時,失敗率為90%。為了提高成功率,我們可能需要進行模擬仿真,并采用更復雜的新型旁路電路。

2019-04-17 15:50:40 1813

1813

RTL代碼),也可以在某些場合加速設計與驗證(例如在FPGA上實現OpenCV函數),但個人還是喜歡直接從RTL入手,這樣可以更好的把握硬件結構。Xilinx官方文檔表示利用HLS進行設計可以大大加速設計進度:

2019-07-31 09:45:17 7434

7434

加利福尼亞州圣何塞, Jan。 20,2016 /PRNewswire/- Cancence Design Systems,Inc。(納斯達克股票代碼:CDNS)今天宣布推出Sigrity?2016技術組合,通過增強的PCB設計和分析方法改善產品創建時間是多千兆位接口的理想選擇。

2019-08-08 09:56:41 1769

1769 賓夕法尼亞州哈里斯堡 - 泰科電子宣布其Z-Pack HM-Zd連接器產品線現在將被歸類為能夠支持每秒10千兆位(Gbit/s)的串行速度。這是對3到5 Gbit/s范圍內差分應用的連接器的原始性能分類的更新。

2019-09-15 16:45:00 2871

2871 多內核處理器可為越來越多的高性能、數據密集型應用帶來優勢,如無線基站與高性能計算平臺等,因此系統可擴展性只能通過大容量嵌入式互連實現。千兆位串行鏈路不但可降低系統成本,減少面積占用與引腳數,同時還可提高并行性,改進性能與容量,從而有助于實現系統可擴展性。

2020-01-19 10:15:00 1604

1604 以太網技術聯盟(EthernetTechnologyConsortium)提出了800千兆位以太網的規范,該行業聯盟包括Arista、Broadcom、Cisco、Dell、Google、Mellanox和Microsoft。

2020-05-18 16:03:22 4049

4049 當在輸入和輸出中遇到換行符時,標準I/O庫執行I/O操作。這允許我們一次輸出一個字符,但只有在寫了一行之后才進行實際I/O操作。標準輸入和標準輸出對應終端設備(如屏幕)時通常是行緩沖的。

2020-07-01 17:17:01 2863

2863 1 I/O延遲約束介紹 要在設計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設計環境(IDE)僅在FPGA邊界內識別時序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 6236

6236 自嵌入式系統問世以來,現場固件更新一直是每個嵌入式系統的關鍵組件。訪問諸如JTAG或SWD編程器之類的編程工具以及對編程端口進行物理訪問通常需要使用額外接口(如USB,CAN,串行端口等)來更新固件。

2021-04-28 10:27:56 2441

2441

電子發燒友網站提供《Ultrascale FPGA多路千兆位收發器電源解決方案.zip》資料免費下載

2022-09-06 10:35:56 0

0 電子發燒友網站提供《符合EMI/EMC標準的工業溫度級雙端口千兆位以太網設計.zip》資料免費下載

2022-09-06 10:05:51 5

5 電子發燒友網站提供《Ultrascale FPGA多路千兆位收發器(MGT)電源解決方案.zip》資料免費下載

2022-09-07 09:45:59 3

3 電子發燒友網站提供《FPGA多路千兆位收發器(MGT)電源解決方案.zip》資料免費下載

2022-09-08 14:10:10 3

3 Google I/O 洞見科技未來" 征文活動 也向身為技術愛好者的你發出召喚 ?往下閱讀,了解課程更新和征文活動吧! Google 開發者在線課程? (Google Developers

2023-05-12 12:00:01 1029

1029

電子發燒友網站提供《使用千兆位收發器分數PLL的全數字VCXO替代方案.pdf》資料免費下載

2023-09-14 14:49:30 0

0 電子發燒友網站提供《用于千兆位收發器應用的全數字VCXO替代方案(UltraScale FPGA).pdf》資料免費下載

2023-09-14 14:55:30 1

1 電子發燒友網站提供《利用千兆位收發器和相關PLL中的功能來替代VCXO電路.pdf》資料免費下載

2023-09-15 10:08:09 0

0 電子發燒友網站提供《DP83561-SP千兆位以太網PHY數據表.pdf》資料免費下載

2024-06-22 10:19:38 0

0 電子發燒友網站提供《SN65LVCP402千兆位2×2交叉點開關數據表.pdf》資料免費下載

2024-07-08 11:11:45 0

0 電子發燒友網站提供《SN65LVCP204千兆位4×4交叉點開關數據表.pdf》資料免費下載

2024-07-08 11:00:40 0

0 電子發燒友網站提供《SN65LVCP202千兆位2×2交叉點開關數據表.pdf》資料免費下載

2024-07-08 10:59:34 0

0 電子發燒友網站提供《通過各種不同長度和數據速率的介質進行高速千兆位數據傳輸.pdf》資料免費下載

2024-09-29 09:44:11 0

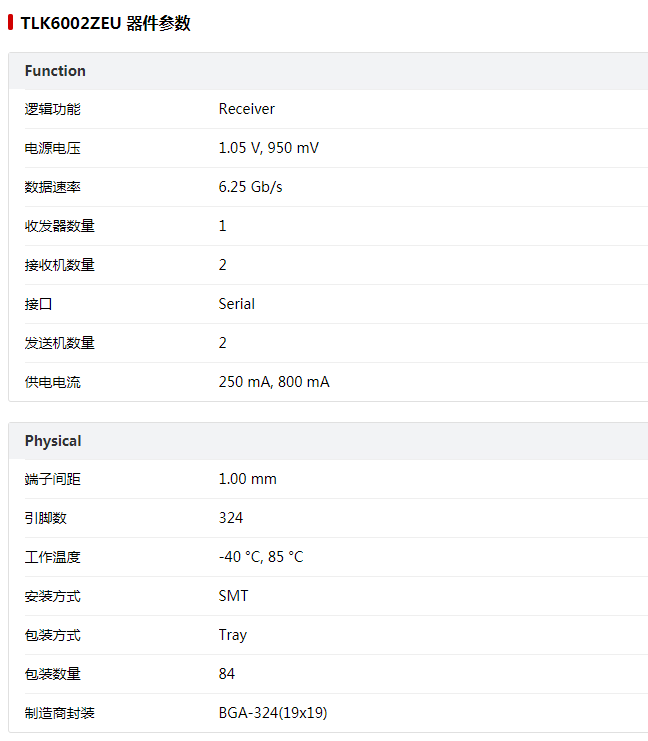

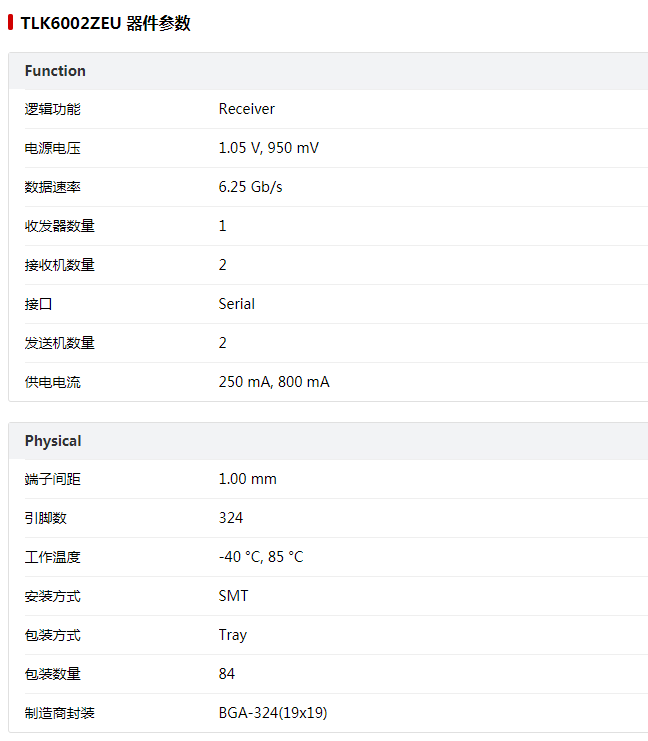

0 Texas Instruments TLK6002ZEU 6千兆位每秒 (Gbps) 的雙通道串行器-解串器 EDA模型與數據手冊解析

2025-06-10 17:17:56 788

788

電子發燒友App

電子發燒友App

硬聲App

硬聲App

1670

1670 1678

1678 39

39 6

6 15

15 1632

1632

638

638

3060

3060

0

0 75

75 29

29 7

7 1123

1123 734

734 1377

1377 313

313 2060

2060

1176

1176 3913

3913 20

20 28

28 2817

2817

3345

3345 1813

1813

7434

7434

1769

1769 2871

2871 1604

1604 4049

4049 2863

2863 6236

6236 2441

2441

3

3 1029

1029

1

1 788

788

評論