在FPGA研發及學習過程中,有一個關鍵步驟就是 下板實現 ,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此,相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。 最近我就遇到

2023-12-04 07:40:02 2632

2632

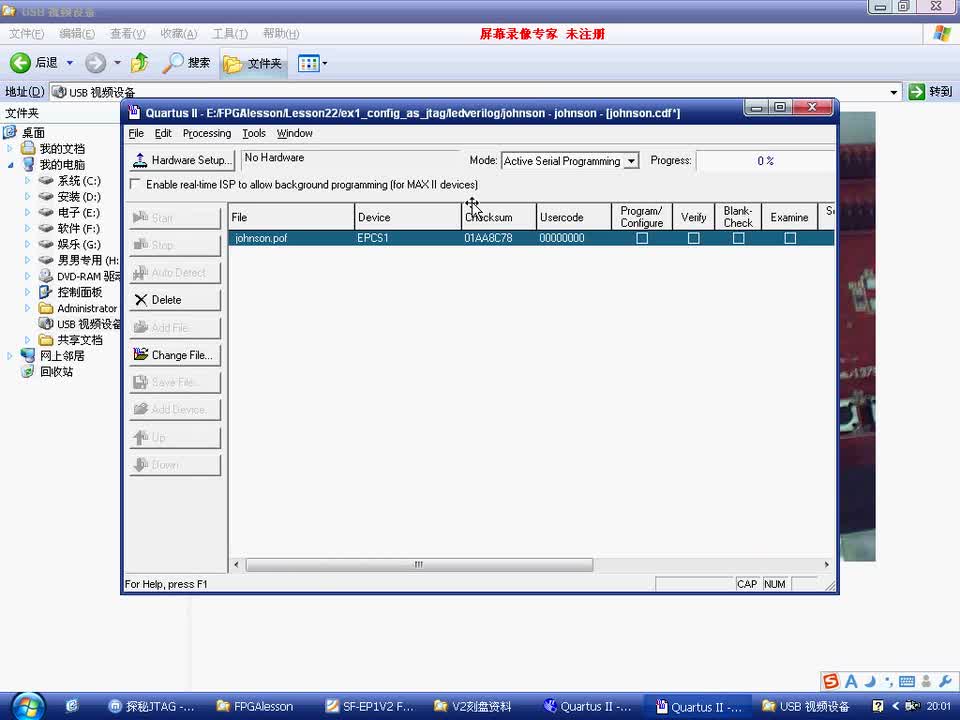

電子發燒友網核心提示: 根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔JTAG下載接口,否則會損壞FPGA芯片的JTAG口信號管腳。 現象: 在排除了下載線的問題

2012-09-05 09:00:42 14317

14317 由JTAG標準決定,通過JTAG寫/讀一個字節要一系列的操作,根據我的分析,使用簡單JTAG電纜,利用打印口,通過JTAG輸出一個字節到目標板,平均需要43個打印口I/O, 在我機器上(P4

2018-06-15 09:06:26 12083

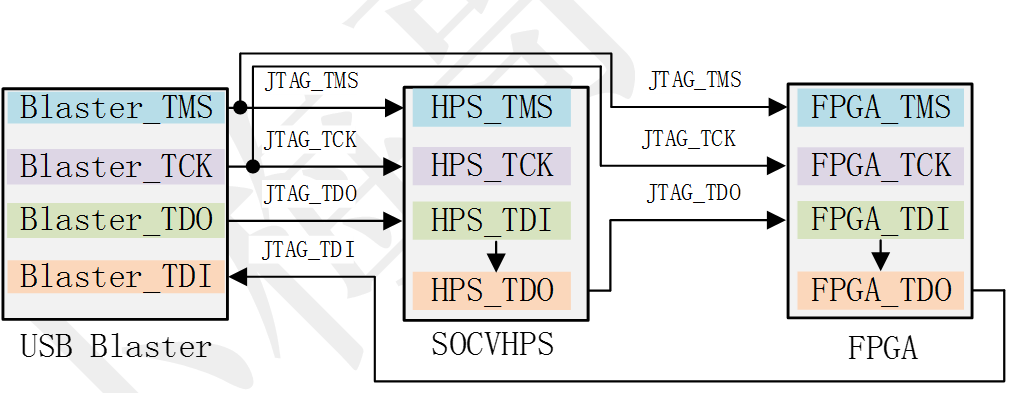

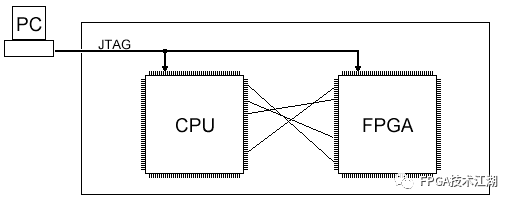

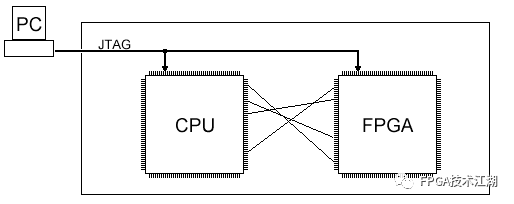

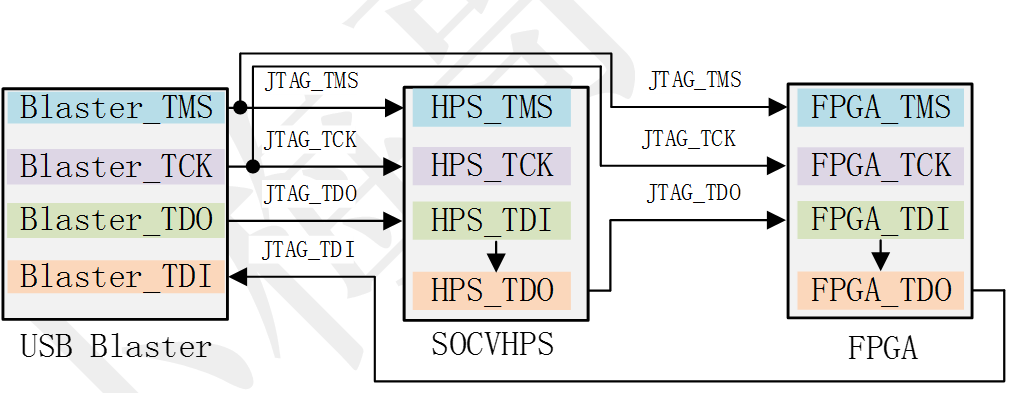

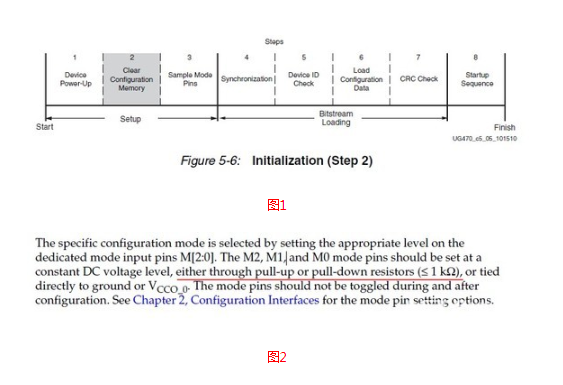

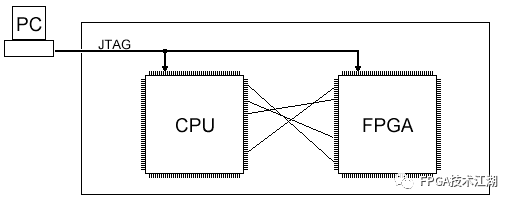

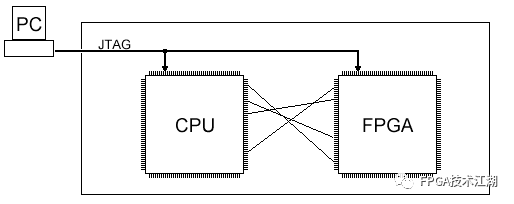

12083 SoC FPGA作為在同一芯片上同時集成了FPGA和HPS的芯片,其JTAG下載和調試電路相較于單獨的FPGA或ARM處理器都有一些差異,但是同時兩者又有緊密的聯系。

2020-08-08 10:08:00 2276

2276

在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。最近我就遇到了這類事情

2022-07-20 09:15:18 13793

13793 FPGA的管腳主要包括:用戶I/O(UserI/O)、配置管腳、電源、時鐘及特殊應用管腳等。其中有些管腳可有多種用途,所以在設計FPGA電路之前,需要認真的閱讀相應

2019-09-18 07:34:49

=FLASE繞過PAR的檢查,這樣就只是將本該接入專用時鐘管腳(或者叫做全局時鐘管腳)的信號,接到了普通IO口上,但并沒有做好如何用普通IO口來引入全局時鐘,Xilinx官方論壇上更是有老外直接指出這只

2019-07-09 08:00:00

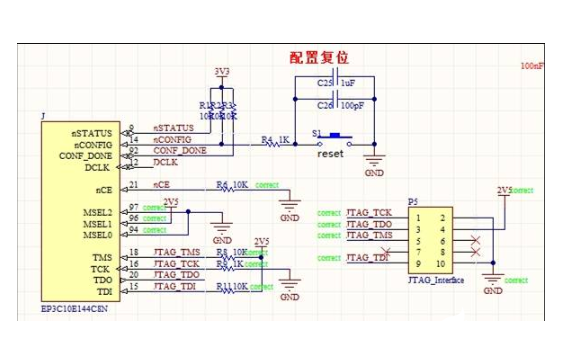

Buffer,支持施密特觸發器的磁滯功能。20/26. nCONFIG專用的輸入管腳。這個管腳是一個配置控制輸入腳。如果這個腳在用戶模式下被置低,FPGA就會丟失掉它的配置數據,并進入一個復位狀態,并將所有

2014-12-29 11:46:33

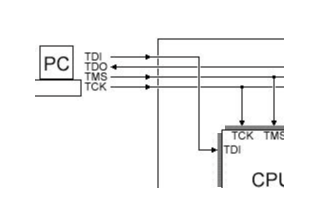

現象: 在排除了下載線的問題后,還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示JTAG信號管腳已經損壞。

2019-05-31 07:01:06

情況下不會發生任何問題。仍然有很小的概率因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。

有人懷疑是否是D版的USB Blaster或者ByteBlasterII設計簡化,去處

2024-06-10 09:41:38

FPGA的JTAG接口和ARM的JTAG接口線是否可以共用同一線呢?是否可以用同usb轉JTAG線給ARM和FPGA以及dsp調試程序呢?

2022-08-10 14:54:43

今天下載時,下載一直失敗,經測量后發現JTAG的TDI引腳與地短路了,請問這能說明是FPGA芯片內部的JTAG接口壞了嗎?還是有肯能是別的問題?有誰遇見過沒?

2013-04-05 22:49:11

電源部分。使用萬用表進行測試,排除電源短路等情況后,上電測量電壓是否正確。(2)然后焊接FPGA及相關的下載電路。再次測量電源地之間是否有短路現象,上電測試電壓是否正確,然后將手排除靜電后觸摸FPGA

2012-08-12 11:52:54

JTAG口如何配置?怎么使用?

2021-10-29 07:22:26

我設計的是FPGA的板子,用JTAG燒寫。直接燒FPGA是沒有問題的,但是燒ROM就會出錯,IDCODE=ff檢驗不通過。網上有人說是JTAG的電平不夠。求問是不是布線的時候JTAG口距離FPGA一定要近一些,線短一些才行?

2013-07-26 15:29:20

“DONE沒有變高”,而當我拿出芯片內核或來自內核的一些信號時,編程成功但之后我的JTAG停止工作。如果我嘗試在iMPACT中初始化JTAG鏈,它會詢問我是否有此設備的BSDL或BIT文件,或者如果我嘗試

2018-10-08 11:19:37

jtag口可以成功下載,as口下載成功但是程序不運行,找了好久一直沒找到原因,電路配置都沒有問題。

2018-01-30 21:30:04

的程序員正常工作7-I檢查我的jtag鏈是否確保電氣關閉(有一個跳線,你可以擴展你的jtag鏈認為FMC連接器)8-我在程序員和fpga板之間使用了兩條不同的電纜(電纜沒問題)解決了所有嫌疑人之后,我

2019-07-11 13:04:21

重點檢查涌浪吸收電路、過電壓保護電路、整流電路是否有故障。如果是行輸出管擊穿,可能保險電阻燒毀,這時應重點檢查行逆程電容是否開焊或燒毀,+B電壓是否過高等故障。燒毀:往往是由于過電流引起,或欠激勵

2013-01-25 21:41:06

我想通過JTAG在我的設計中內部訪問寄存器。1)如何掛鉤fpga JTAG鏈?2)是否有JTAG控制器IP?我看了,沒看到一個。謝謝,弗雷德

2020-05-29 06:13:24

CYCLONE IV FPGA 想用JTAG口編程FLASH,MSEL所在BANK被用于DDR,IO電壓為1.8V,手冊的配置方案表中AS模式的配置電壓標準沒有1.8V。是否可以理解成在JTAG方式

2019-03-21 10:24:44

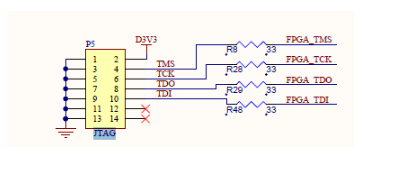

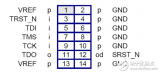

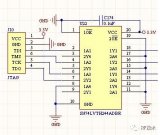

本人學生一枚,在畫的第一塊FPGA板上采用的EP3C25E144這個片子,實際調試中遇到了如下問題,焊上去之后整個JTAG口無法正常工作,TMS與TDI電壓時鐘與VCCIO存在一個壓降,VCCIO用的為3.3v,而這個量管腳的電壓為2.5v,各為幫忙看下JTAG口這部分電路是否存在問題,謝謝的了。

2013-03-30 21:24:12

`各位大佬們,為啥我一上電24V,電容發熱,熱敏電阻被擊穿啊`

2019-11-16 11:02:24

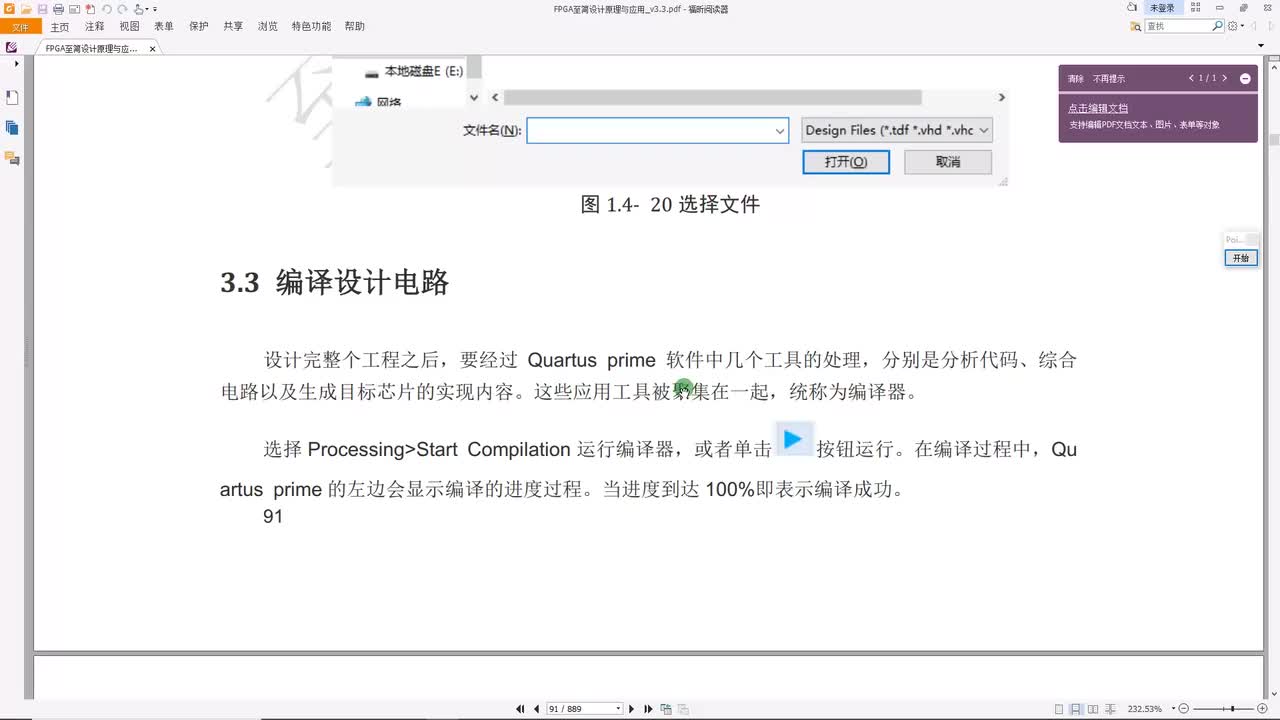

Quartus II 下FPGA管腳鎖定在新建工程、編輯文件、編譯、排錯完成后就進入管腳鎖定以及電平設置階段。這里還是以一位全加器為例介紹管腳鎖定。開發板使用FII-PRA006. 開發工具

2021-07-30 15:09:59

`網上看到了各種版本,有說JTAG口要用3.3V,有說要用2.5V的。手頭有個USB_BLASTER的下載器。不知道具體要用多少伏的。還有一個問題,看官方手冊,說JTAG口的6腳不接。但是我手頭有個開發板,JTAG的6腳與4腳接在一起了。`

2017-10-18 11:29:10

對JTAG的資料認識:(2)JTAG小知識我們經常為了方便,隨意插拔JTAG下載口,在多數情況下不會發生任何問題。仍然有很小的概率因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿

2015-05-23 15:51:49

,RTCK管腳一般是用來控制是否使能JTAG接口的,請查閱數據手冊;F - 如果你用的芯片比較特殊,例如STR91X,因為內部掃描鏈是串接的,請設置好TAP,以讓仿真器知道掃描鏈的長度;

2011-11-30 10:18:29

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。JTAG協議制定了一種邊界掃描的規范,邊界掃描架構提供了有效的測試布局緊湊的PCB板上元

2020-02-25 18:40:45

什么是電容擊穿?電容器被擊穿的條件是什么?電容擊穿是開路還是短路?電容擊穿的原因是什么?如何避免介質擊穿?

2021-06-18 09:59:11

下面的問題,因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。至此,也有人懷疑是否是盜版的USB Blaster或者ByteBlasterII設計簡化,去除了保護電路導致的。但經過很多

2023-05-19 19:47:36

我司在使用一片DLP3010的時候,出現工作一段時間后被擊穿的現象,取下來進行檢查發現VRST管腳對地電阻僅有5歐姆,外觀無任何異常。我們想確定問題的原因,ESD/熱/電擊穿,結果在OM顯微鏡下出現了下面的圖像,猜測可能是問題點。

請問針對可能的原因或者下一步的排查方向,是否有什么建議呢?

2025-02-18 06:38:24

熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。至此,也有人懷疑是否是盜版的USB Blaster或者ByteBlasterII設計簡化,去除了保護電路導致的。但經過很多實際情況的反饋

2024-01-19 21:19:29

右鍵然后點擊 show IO banks,這個時候就會看到FPGA的管腳被幾種顏色劃分開了。一種顏色下的IO口代表一組bank。你在吧管腳的locaTIon約束完成以后。IO Bank會自動填充完畢

2019-04-03 07:00:00

JTAG 管腳屬性都是inout,在模塊里面用了IOBUF原語做了IO管腳的IO方向適配,因此,當DO的輸出有效時,其高低電平由E203的JTAG模塊確定,而當DO輸出無效時,該管腳被IOBUF定義為

2025-10-28 07:38:36

嗨,我一直在看這個問題:http://forums.xilinx.com/t5/Xilinx-Boards-and-Kits/spartan6-fpga-Jtag

2019-08-01 08:17:03

AVR單片機使用JTAG口作為普通I/O口的方法有哪幾種?JTAG口的配置方式是什么?如何去使用JTAG口?使用JTAG口需要注意什么事項?

2021-07-07 06:22:05

小妹正在做一個軟件,想通過編程把數據傳到PC的并口在從其與jtag接口相連通過從JTAG口TDI串入數據和指令,再從TDO串出掃描結果,在主機上進行比對以實現測試,目前我主要用VC來編程。請問一下我

2008-08-15 16:21:01

我想知道是否有人能指出一份文件,該文件為Xilinx FPGA中的JTAG操作提供了深入的技術細節。我正在考慮將自己的TAP控制器構建到JTAG程序/更新FPGA。我還想了解Xilinx特定JTAG

2019-01-24 09:36:40

的糾紛。防護的話加齊納穩壓管保護。 現在的mos管沒有那么容易被擊穿,尤其是是大功率的vmos,主要是不少都有二極管保護。vmos柵極電容大,感應不出高壓。與干燥的北方不同,南方潮濕不易產生靜電。還有

2018-10-22 15:35:34

司用UF1M的二極管(1A1000V)接在14管腳上,低壓啟動100V時,二極管的電流過大1.2A會擊穿二極管,高壓220V時電壓在1A左右沒有問題,請大神分析下,在它負極端接一個10的電阻對不對,能不能起到限流的作用呢?

2019-01-11 08:00:00

是這樣的。。 LPC2103的 JTAG口 也就是P0.27-P0.31口 如果想作為I/O口的話應該怎么樣設置呢? 光對這幾個管腳進行管腳配置好像沒有用的。。是不是應該對JTAG功能進行屏蔽呢,該怎么屏蔽啊?有沒有大神來指導一下。。

2014-01-14 15:06:02

現在懷疑板子上的電容被擊穿了,請問電容被擊穿是開路還是短路?謝謝

2016-11-29 21:04:02

本帖最后由 yangk1990 于 2013-3-8 17:11 編輯

本人初學,需要設計一個示波器觀測電容器被擊穿的波形(或者可變電容逐漸減小到變成導體也行),但電容器的擊穿著實不會...希望大神們能夠指點一下!

2013-03-07 20:38:47

XAPP1251說明顯示,可以在Zynq ARM處理器上運行XVC服務器來控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一個FPGA中控制PL JTAG?可以使用運行在設備PS部分上

2020-07-30 13:51:19

TM4C將jtag口鎖定后解鎖,就會將flash全部擦除。而在bootloader中只看到編程的命令,沒有讀取的命令。那這樣的話是否將jtag口鎖定后是否就能起到保護flash代碼的作用,而不需要使用MPU。因為MPU部分沒做過,看文檔也是看得云里霧里的。

2019-09-09 07:43:19

本帖最后由 一只耳朵怪 于 2018-6-21 15:55 編輯

JTAG調試的下載器選用TI有配套的么?JTAG口在電路設計上可以如FPGA的JTAG口一樣設計為2.54間距的排針么

2018-06-21 04:41:08

什么是JTAG 到底什么是JTAG呢? JTAG(Joint Test Action Group)聯合測試行動小組)是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG

2007-06-05 12:10:48 98

98 本檢查清單向你揭示了如何提高你的FPGA設計的速度和可靠性,本檢查清單適用于Xilinx公司的Virtex系列FPGA.采用這些技巧應該能改進你的設計性能,本檢查清單應該能幫助所有的FPGA設計

2009-02-07 10:21:06 28

28 通過JTAG 實現對Flash 在線編程。首先, 介紹JTAG 的定義、結構及引腳的定義, 并闡述JTAG 狀態機的工作原理。然后,介紹JTAG口的邊界掃描寄存器,給出實現JTAG在線寫Flash的電路, 和

2009-04-16 10:00:04 62

62 LM3S系列單片機JTAG口解鎖應用筆記

介紹LM3S系列單片機的JTAG口被設置為GPIO后,恢復JTAG功能的方法。

2010-04-07 16:20:46 52

52 LM3S系列單片機JTAG口解鎖應用筆記

2010-07-19 15:32:12 52

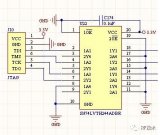

52 本內容向大家提供了JTAG功能及系統設計 JTAG也是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG協議,如DSP、FPGA器件等。標準的JTAG接口是

2011-03-30 10:04:32 0

0 如何檢查光耦是否損壞?

2012-07-02 14:02:13 7784

7784 Xilinx的JTAG電纜可以通過FPGA“直接”燒寫SPI/BPI。很多對xilinx開發環境不熟悉的用戶,如果第一次接觸這種燒寫模式可能會有疑惑,FPGA是如何做到JTAG和Flash之間的橋接

2017-02-08 02:40:11 10305

10305

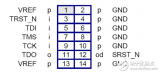

JTAG接口都滿足IEEE 1149.1的標準。滿足IEEE 1149.1標準的14腳JTAG接口如圖1所示。 圖1 14腳仿真口引腳 一般情況下,最小系統板需要引出雙排的14腳插針和圖2所示的一致

2017-12-02 09:46:46 1856

1856

的測試電路TAP(TestAccessPort,測試訪問口),通過專用的JTAG測試工具對內部節點進行測試。

2018-01-11 09:45:50 32649

32649

?Action?Group)是1985年制定的檢測PCB和IC芯片的一個標準,1990年被修改后成為IEEE的一個標準,即IEEE1149.1-1990。通過這個標準,可對具有JTAG口芯片的硬件電路

2018-09-20 18:26:04 2976

2976 同志們,根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔你的JTAG下載接口,否則會損壞FPGA芯片的JTAG口信號管腳。

2019-07-31 17:35:00 0

0 MOS管為什么會被靜電擊穿?靜電擊穿是指擊穿MOS管G極的那層絕緣層嗎?擊穿就一定短路了嗎?JFET管靜電擊穿又是怎么回事?

2019-05-20 17:21:00 36881

36881 JTAG是串行接口,使用打印口的簡單JTAG電纜,利用的是打印口的輸出帶鎖存的特點,使用軟件通過I/O產生JTAG時序。

2019-10-18 11:47:00 2731

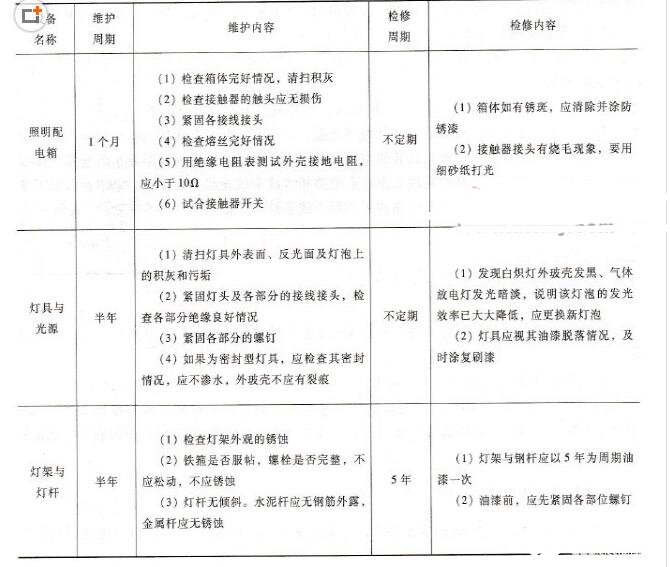

2731 檢查照明燈具上的燈泡容量是否超過額定容量,100W以上燈具的燈口應使用瓷質燈口。

2019-11-30 17:18:37 7624

7624

問題是FPGA使用JTAG口能把程序到FPGA,FPGA也能跑得動,當配置模式選擇MASTER SPI時,通過JTAG口下載也可以下載成功,但是問題是重新上電發現FPGA無法讀出FLASH的配置文件。

2020-03-15 16:08:00 4039

4039

JTAG是Joint Test Action Group的縮寫,是IEEE 1149.1標準。使用JTAG的優點:JTAG的建立使得集成電路固定在PCB上,只通過邊界掃描便可以被測試。在ARM7TDMI處理器中,可以通過JTAG直接控制ARM的內部總線、I/O口等信息,從而達到調試的目的。

2020-07-20 14:46:30 6393

6393 檢查文件是否存在的方法, 在Python3 文件操作中經常被用到, 因為,只有文件存在, 我們才可以對文件進行下一步處理, 那么,常用的檢查文件存在的方法有哪些呢?以下是Python3 檢查文件是否存在的幾種方法。

2020-10-26 17:08:14 14

14 本文檔的主要內容詳細介紹的是FPGA JTAG工具設計的教程說明。

2020-12-31 17:30:55 18

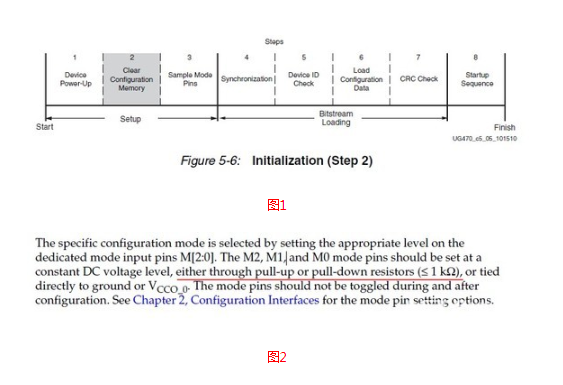

18 賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[1:0] 的電平,都可用采用該配置模式。JTAG模式不需要額外的掉電非易失

2020-12-31 17:30:55 13

13 最近我就遇到了這類事情,FPGA的JTAG口突然就不能下載程序了,而且這種事情已經不是第一次了,之前在做項目的時候也出現過,而且出現的形式也極其相似,之前還用的好好的,第二天就不行了,真是讓人郁悶。

2021-03-04 16:14:18 4484

4484

在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。

2021-03-17 14:05:33 13115

13115

介紹IO口與FPGA管腳對應關系表。

2021-03-18 10:02:26 12

12 開發板(在本文中將其簡稱為“FPGA開發板”)和專用 JTAG 調試器(在本文中將其簡稱為“JTAG 調試器”)。

2021-03-23 10:00:28 41

41 ?小編給大家詳細的講解一下力士樂葉片泵油封被擊穿而串油的原因分析如下: 一、零部件制造質量較差 1、油封質量:唇口幾何形狀不合格,縮緊彈簧太松等,造成氣密性試驗漏氣,力士樂葉片泵裝入主機后容易使油封被擊穿而串油。應

2021-05-14 11:55:45 668

668 在stm32 IAP例程中,跳轉到APP區的時候,都會檢查棧頂地址是否合法,以及reset地址是否正確等信息,那么這些判斷具體依據什么原理???以stm32H743為例說明↓↓↓↓檢查棧頂是否合法

2021-12-16 16:58:19 11

11 單片機燒錄程序時易忽視錯誤及解決方案錯誤:串口打開失敗!請檢查指定串口是否存在或者已被打開1、檢查COM口是否沖突解決方法: 將沖突COM口改為其他COM口號步驟:一、打開此電腦,點擊管理二、打開

2021-12-20 18:44:53 0

0 關注、星標公眾號,直達精彩內容素材來源:FPGA資源俠客在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠...

2021-12-31 19:16:14 1

1 今天在焊PCB板的時候,原本是好好的,可以燒錄程序,但后來焊了一些元件之后發現下載不了,并且元件燙的出奇。經檢查,發現原來是電容的問題。 顯然,電容壞了。電容擊穿的方式,有兩種:1、熱擊穿,當介質

2022-01-11 14:50:36 4

4 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 3151

3151

根據查閱資料及本人的一些實踐經驗所得,在使用JTAG下載接口的過程中,請不要隨意帶電插拔,否則會損壞FPGA芯片的JTAG口信號管腳。那么如何去確認JTAG口已經損壞了呢。首先你要去排除基本的幾項因素

2022-07-26 09:29:34 1861

1861 在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。最近我就遇到了這類事情

2023-06-07 12:35:31 2994

2994

在線仿真、調試,它在芯片內部封裝了專門的測試電路 TAP ( Test Access Port ,測試訪問口),通過專用的JTAG測試工具對芯片進行測試。現在多數的高級器件都支持JTAG協議,如以以ARM

2023-06-14 09:15:46 17020

17020

晶閘管被擊穿有什么影響? 晶閘管是一種半導體器件,它在控制電路中起著非常關鍵的作用。然而,當晶閘管被擊穿時,它會受到損壞,從而影響整個電路的正常運行。因此,了解晶閘管被擊穿的影響非常重要。本文將對

2023-09-13 16:39:51 4410

4410 如何檢查消防應急燈是否正常工作? 檢查消防應急燈是否正常工作需要按照以下步驟進行: 一、查看外觀是否完整 首先,要檢查消防應急燈的外觀是否完整,有無破損或損壞的情況。消防應急燈的外觀應整潔,無裂紋

2023-11-08 16:41:32 9098

9098 如何判斷故障點是否擊穿放電?若故障點未擊穿能否長時間帶電測量? 判斷故障點是否擊穿放電的方法通常有以下幾種: 1. 視覺檢查:故障點周圍是否存在燒焦、熔化或濺融等現象。如果存在這些現象,說明故障點有

2023-12-26 16:01:51 1046

1046 MOS管的敏感性使其容易受到靜電放電(ESD)的損害,這可能導致器件性能下降甚至完全失效。本文將深入探討MOS管被擊穿的原因,并提出相應的解決方案,以幫助電子工程師和技術人員更好地理解和處理這一

2024-10-04 16:44:00 5742

5742 預防電容器被擊穿的風險需要從設計、安裝、運行和維護等多個方面進行管理。

2024-10-24 17:56:03 1590

1590 在展開今天的文章前,先來討論一個問題:FPGA的jtag接口燒了怎么辦?JTAG接口的輸入引腳通常設計為高阻抗,這使得它們對靜電電荷積累非常敏感,由于JTAG接口需要頻繁連接調試器、下載線纜等外

2025-04-27 11:01:56 2301

2301

電子發燒友App

電子發燒友App

評論