引言:本文介紹最常見的外部噪聲源以及它們?nèi)绾斡绊懜咚?a target="_blank">信號鏈的總動態(tài)系統(tǒng)性能,另外給出了一些模擬和數(shù)字小技巧,可用來改善您下一款設(shè)計(jì)的信噪比(SNR)。

簡介

高速模擬信號鏈的設(shè)計(jì)可能非常具有挑戰(zhàn)性,因?yàn)橛腥绱硕嗟脑肼曉葱杓右钥紤]。無論頻率為高速(>10 MHz)或低速,轉(zhuǎn)換器都應(yīng)視為高速混頻器,從而所有輸入引腳——無論它們pin信號的類型如何(比如模擬、時(shí)鐘或電源)——都能讓這些pin腳的噪聲引入到輸出頻譜。

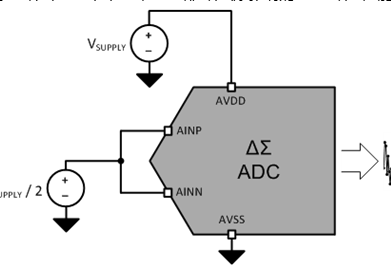

轉(zhuǎn)換器受限于工藝水平會有特定的底噪,其取決于內(nèi)部節(jié)點(diǎn)和偏置。大部分情況下,高速ADC采用0.18 μCMOS設(shè)計(jì),這意味著模擬電源(AVDD)為+1.8 V。這種趨勢會持續(xù)擴(kuò)大周邊其它驅(qū)動模擬輸入和時(shí)鐘的支持器件極限,導(dǎo)致轉(zhuǎn)換器產(chǎn)生偏壓。

由于這一轉(zhuǎn)換器裕量不斷受限,每一款新的設(shè)計(jì)都會面臨保持?150 dBFS/Hz或更低的極低噪聲頻譜密度的挑戰(zhàn)。設(shè)計(jì)人員需認(rèn)識到周邊噪聲貢獻(xiàn)因素對整個(gè)信號鏈解決方案的重要性,而這就是這種認(rèn)識至為重要的原因。

誠然,有很多噪聲原理。本指南涉及其中的兩條原理:噪聲帶寬和噪聲源疊加。

噪聲帶寬

噪聲帶寬不同于典型的放大器或濾波器截止點(diǎn)的?3 dB帶寬。噪聲波形具有不同的形狀(矩形),表示帶寬的總積分。這表示考慮噪聲帶寬貢獻(xiàn)因素時(shí),您需要略為調(diào)整噪聲計(jì)算。

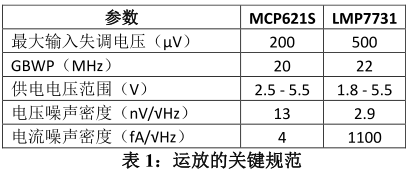

對于一階系統(tǒng)而言——比如一階低通濾波器——噪聲帶寬會寬57%。對于二階系統(tǒng),噪聲帶寬會寬22%;而三階系統(tǒng)為15.5%,以此類推。在計(jì)算中納入噪聲帶寬時(shí),可快速參考表1。

?

噪聲源

噪聲源五花八門;添加噪聲源時(shí),它們互不相關(guān),并且會分解為更小的單位,而非直接相疊加。因此,有利于突破目前受單個(gè)器件所限制的極限。因此,它所帶來的優(yōu)勢是可以突破目前受單個(gè)器件所限制的極限。它所帶來的優(yōu)勢——如果能夠在應(yīng)用中加以利用的話——就是您可以疊加驅(qū)動器/放大器或轉(zhuǎn)換器(或兩者)來改善系統(tǒng)的SNR動態(tài)范圍。

例如,對四個(gè)ADC的輸出求和可改善SNR 6 dB,或1位。每一個(gè)ADC的輸入由信號項(xiàng)(VS)和噪聲項(xiàng)(VN)組成。對四個(gè)噪聲電壓源求和可產(chǎn)生總電壓VT,數(shù)值為四個(gè)信號電壓與四個(gè)信號電壓與四個(gè)噪聲電壓的RSS的線性求和參見公式1:總噪聲公式)。

?

?

?

表2顯示了對多個(gè)器件的輸出進(jìn)行求和后得到的SNR提升。從簡化設(shè)計(jì)角度來說,根據(jù)面積、功耗和封裝等方面考慮,對四個(gè)器件求和顯然是非常合適的選擇。某些關(guān)鍵情況下,可能會用到更多數(shù)量的器件,具體取決于其它系統(tǒng)規(guī)格(包括成本)以及可用的電路板面積,當(dāng)然還有功耗。

?

?

圖1. 四個(gè)并聯(lián)ADC求和的基本框圖

最近,較新的設(shè)計(jì)會繼續(xù)降低ADC的內(nèi)核功耗,從而使得四通道和八通道ADC可即刻投放市場,比如四通道、14位、125 MSPS ADC AD9253。對于多個(gè)ADC系統(tǒng)而言,這意味著部署更簡單、節(jié)省的空間更多。因此,通過對四個(gè)14位轉(zhuǎn)換器輸出進(jìn)行求和,設(shè)計(jì)人員便可彌補(bǔ)額外的一位,并將系統(tǒng)級ENOB擴(kuò)展至13位(或80 dB)。

同樣的技巧還可用于雙通道和4道放大器,降低進(jìn)入轉(zhuǎn)換器的加性噪聲。

?

圖2. 求和SNR性能與頻率的關(guān)系

噪聲貢獻(xiàn)因素

幾乎所有電路元件都存在一定的固有噪聲,尤其是有源器件。電阻是小噪聲的源泉,會產(chǎn)生一定量的熱噪聲。它們的貢獻(xiàn)因素較小,但如果設(shè)計(jì)人員使用高數(shù)值電阻圍繞放大器來驅(qū)動轉(zhuǎn)換器,則它的噪聲貢獻(xiàn)因素相比所需性能會變得非常巨大。在該電阻周圍采用小增益會得到更大的噪聲。

?

例如,圖3顯示的是采用AD8138放大器的放大器噪聲模型。該模型顯示了如何對所有電阻噪聲求和并將增益納入考慮,以便獲得折合到輸出的總噪聲。

?

圖3. 放大器噪聲模型

注意,放大器具有某些電壓噪聲源(En1和En2),以及某些電流噪聲源(In1和In2)。這些噪聲源可在放大器數(shù)據(jù)手冊的規(guī)格中找到。另外,數(shù)據(jù)手冊還會定義每一個(gè)電阻噪聲源。

通過簡單的計(jì)算便可以定義下述公式,并得到圖3中放大器電路折合到輸出(RTO)的總噪聲。

?

注意,放大器與運(yùn)算放大器的區(qū)別僅僅在于前者內(nèi)部含有阻性元件。因此,噪聲計(jì)算包含在總噪聲貢獻(xiàn)因素中,并由數(shù)據(jù)手冊定義。

在數(shù)據(jù)手冊中,它一般表示為“折合到輸入”(RTI)的噪聲。通過選擇放大器電路增益,可以快速使用RTI數(shù)值,并將其調(diào)整為:

RTI = 1.3 nV/√(Hz)

增益 = 16 dB

從而有:RTO = 1.3 × 10(16/20) = 8.2 nV/√(Hz)

出于噪聲分析的目的,使用內(nèi)置電阻的放大器要方便的多。

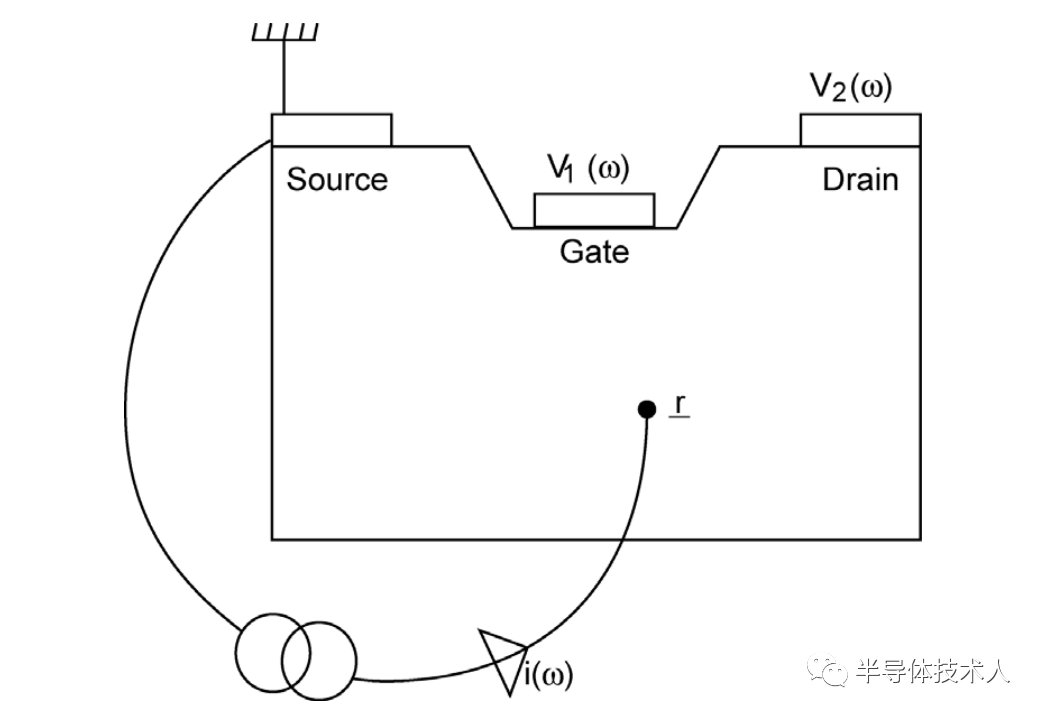

抖動

時(shí)鐘噪聲或抖動影響轉(zhuǎn)換器性能。如果您對如何確定該噪聲的系數(shù)有初步了解——比如說在寬帶中確定——那么很容易對該指標(biāo)所導(dǎo)致的性能下降有所感受。

只需使用寬帶抖動噪聲數(shù)秒(最好是fs級別或更短的時(shí)間)以及模擬輸入頻率或目標(biāo)IF頻率, 當(dāng)時(shí)鐘幅度為最大值并假定輸入為正弦波,那么就會產(chǎn)生最大誤差。可以導(dǎo)出一個(gè)簡單的公式,以獲得RMS電壓誤差。例如,30 MHz模擬輸入IF和100 fs時(shí)鐘抖動便可產(chǎn)生18.8 μV或2 × π 30 M × 100 fs的寬帶電壓噪聲。

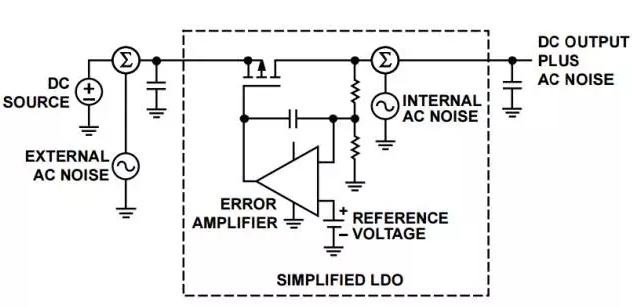

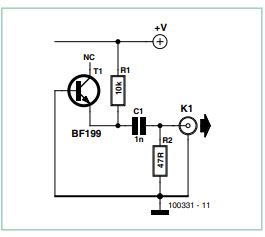

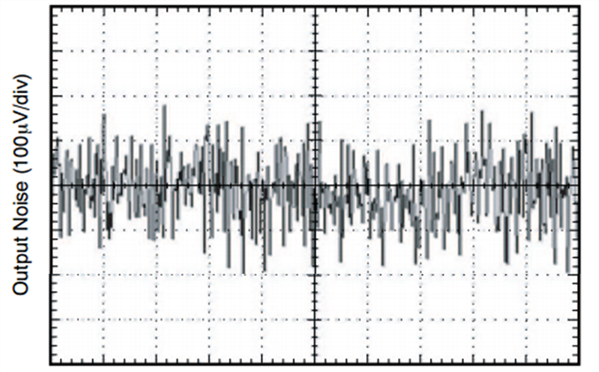

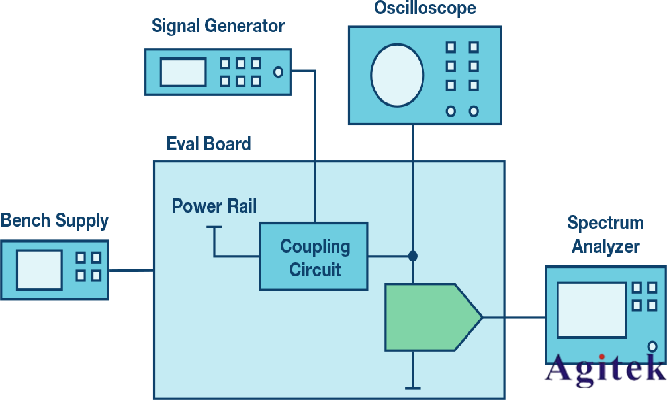

電源噪聲

探索電源噪聲需要知道LDO本身的噪聲及其測量頻段。這些數(shù)據(jù)同樣可在調(diào)節(jié)器數(shù)據(jù)手冊中找到。例如,一個(gè)調(diào)節(jié)器在100 kHz帶寬內(nèi)可能具有225 μV噪聲。如果這是已知的,并且噪聲視為白噪聲,則可以用來估計(jì)它對ADC噪聲性能(SNR)的貢獻(xiàn)。然而,您需要知道ADC電源抑制(PSR)。

大部分情況下,在模擬電源域內(nèi)(AVDD),第一奈奎斯特區(qū)的電源抑制為?40 dB至?60 dB。因此,為了簡便起見,本例中假定為?40 dB。由此可知,有效噪聲貢獻(xiàn)為7.12 nV或225 μV/√(100 kHz) × 10(?40/20)。記住,這只是一個(gè)電源域的情況。所有電源域都需要進(jìn)行同樣的評估,而每一個(gè)域在ADC、放大器等器件內(nèi)可能具有不同的PSR值。

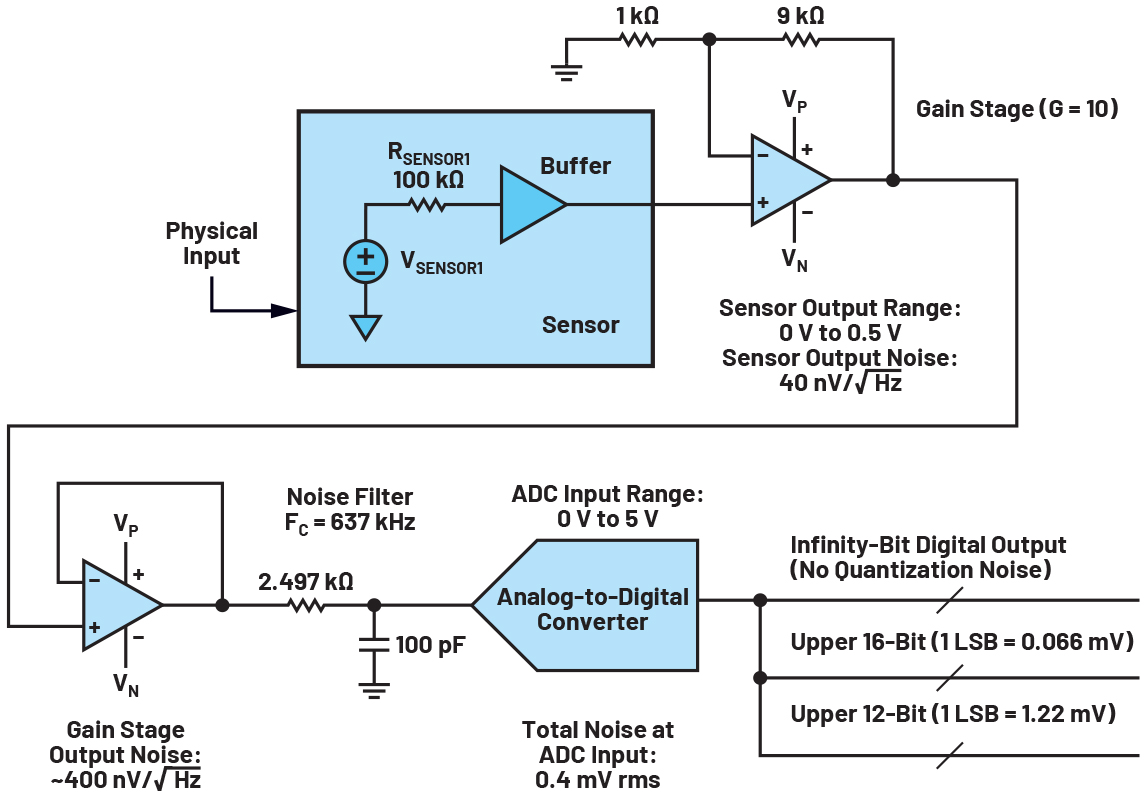

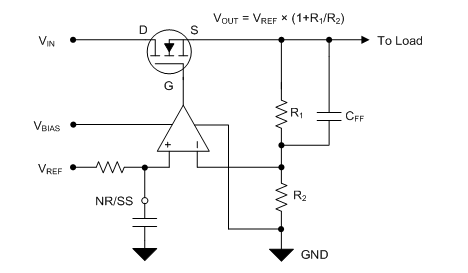

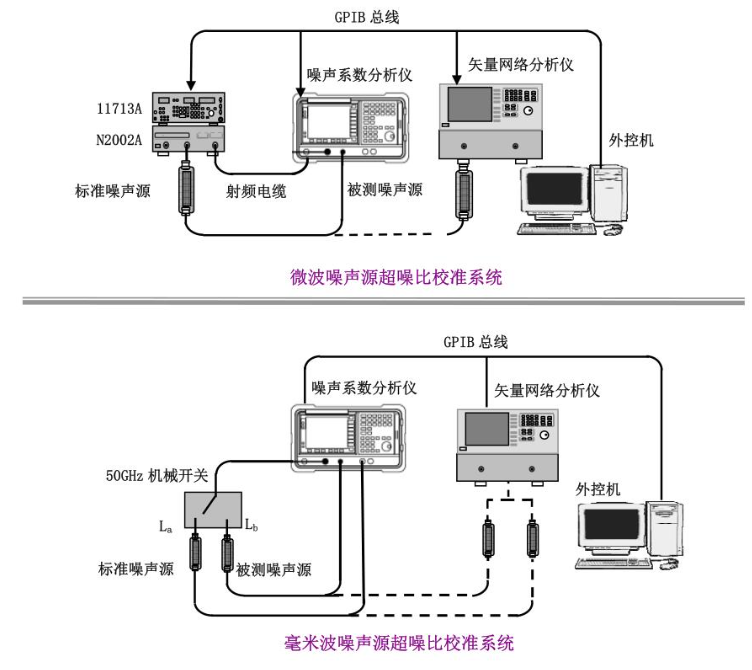

在信號鏈設(shè)計(jì)中考慮噪聲因素

下面的示例會幫助鞏固這個(gè)原則,并將進(jìn)一步展示整個(gè)信號鏈的總動態(tài)性能。該示例采用ADL5566放大器驅(qū)動AD9643 ADC和獨(dú)立電源(ADP1708和ADP1706),并分別偏置放大器和轉(zhuǎn)換器,如圖4所示。

?

圖4. 示例信號鏈框圖

由于上一節(jié)完成了很多前期工作,下一步需要計(jì)算的就是ADC熱噪聲。

對于AD9643,模擬輸入滿量程為差分1.75 V p-p,其數(shù)據(jù)手冊中的SNR為71.7 dBFS。通過反向計(jì)算SNR公式,可知熱噪聲為:

SNR = 20 × log(滿量程V rms)/熱噪聲 (V rms))

或者

71.7 = 20 × log((1.75/2/√(2))/熱噪聲 (V rms))

或者

熱噪聲 = 161 μV rms

下一步,確定電源的噪聲貢獻(xiàn)因素。示例計(jì)算表明ADC模擬電源的AVDD貢獻(xiàn)因素為7.12 nV rms。

為轉(zhuǎn)換器的DRVDD和放大器的AVDD電源執(zhí)行同樣的計(jì)算。進(jìn)行這些計(jì)算時(shí),DRVDD的PSRR為?80 dB,放大器AVDD的PSRR為?60 dB。在同一個(gè)頻段內(nèi),這分別等于71.2 pV rms和1.42 nV rms噪聲貢獻(xiàn)因素

?

對于這個(gè)放大器示例而言,ADL5566在最大16的dB增益的條件下,RTO噪聲為8.2 nV/√(Hz)。接下來,需定義帶寬。通常可在放大器輸出以及轉(zhuǎn)換器輸入之間使用一個(gè)抗混疊濾波器, 否則所有的放大器寬帶噪聲都會折回帶內(nèi)。對此噪聲進(jìn)行限制,假定濾波器帶寬為150 MHz(?3 dB點(diǎn))。使用此數(shù)值是因?yàn)锳D9643是一個(gè)250 MSPS ADC,并且其奈奎斯特頻段為fs/2或125 MHz。通常,為了捕捉整個(gè)目標(biāo)奈奎斯特頻段,會將AAF設(shè)計(jì)得略大。如圖7所示,放置一個(gè)2階或雙極點(diǎn)LC濾波器用于抗混疊抑制。這樣使得噪聲帶寬為:150 MHZ × 1.22 = 183 MHz。因此,計(jì)算可知,放大器的噪聲貢獻(xiàn)因素為111 μV rms,或8.2 nV/√(183 MHZ)。現(xiàn)在,只需采用如下標(biāo)準(zhǔn)SNR公式,對所有示例中推導(dǎo)出的噪聲源執(zhí)行RSS計(jì)算:

這樣就得到了關(guān)于SNR的總信號動態(tài)范圍。如果仔細(xì)查看這些貢獻(xiàn)因素,便可輕松理解信號鏈的哪一部分具有最大的貢獻(xiàn)。理解這些噪聲源可以明白如何進(jìn)行權(quán)衡取舍,才能讓所選相關(guān)設(shè)備發(fā)揮最佳整體性能。

?

圖5. ADL5566和AD9643測得的FFT/噪底性能

信號鏈設(shè)計(jì)性能

理解噪聲權(quán)衡取舍以及信號鏈中產(chǎn)生噪聲的根本原因可以使前期的設(shè)計(jì)變得更為簡單。這篇小型指南解釋了所有器件——無論有源器件或無源器件——如何在信號鏈中交互,以便準(zhǔn)確預(yù)測整個(gè)信號鏈的SNR動態(tài)范圍性能結(jié)果。進(jìn)行下一款信號鏈設(shè)計(jì)時(shí),應(yīng)牢記這些原則。

電子發(fā)燒友App

電子發(fā)燒友App

評論