根據(jù)線陣CCD圖像檢測(cè)和識(shí)別系統(tǒng)的要求,分析線陣CCD圖像與子圖像的位置關(guān)系,采用“圖像轉(zhuǎn)置緩沖區(qū)”和讀寫(xiě)狀態(tài)機(jī)的處理方式,設(shè)計(jì)基于FPGA 的線陣CCD 子圖像提取模塊,具有FPGA 資源占用少、邏輯清晰的特點(diǎn)。用MATLAB 和Modelsim 軟件進(jìn)行聯(lián)合仿真,驗(yàn)證了設(shè)計(jì)的正確性。

2014-02-18 15:34:54 1778

1778

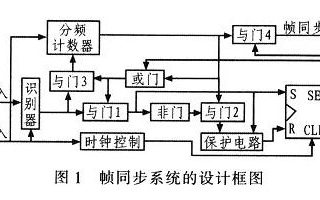

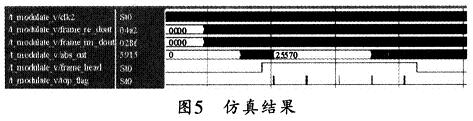

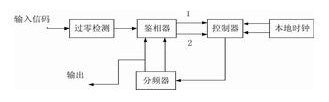

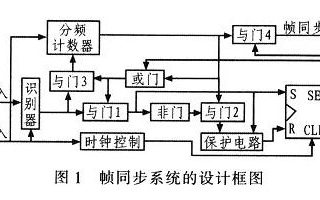

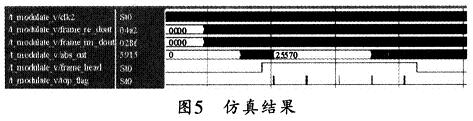

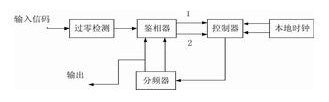

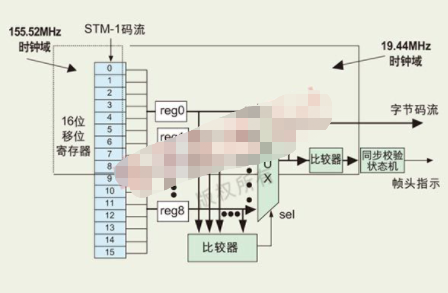

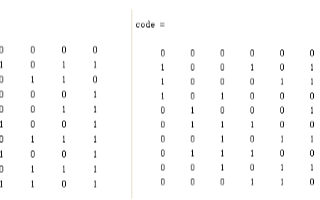

實(shí)現(xiàn)幀同步的關(guān)鍵是把同步碼從一幀幀數(shù)據(jù)流中提取出來(lái)。本設(shè)計(jì)的一幀信碼由39位碼元組成。其中的巴克碼為1110010七位碼,數(shù)據(jù)碼由32位碼元組成。只有當(dāng)接收端收到一幀信號(hào)時(shí),才會(huì)輸出同步信號(hào)。幀同步系統(tǒng)的設(shè)計(jì)框圖如圖1所示。

2020-01-08 16:30:06 13264

13264

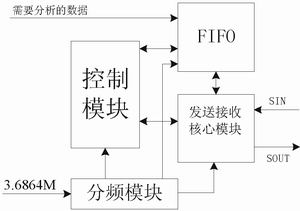

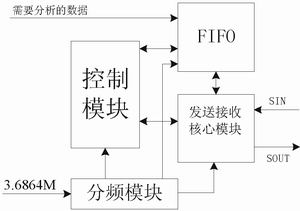

本次的設(shè)計(jì)為多路UART/SPI通信系統(tǒng),可以實(shí)現(xiàn)一對(duì)多的通信。系統(tǒng)可以運(yùn)行在UART模式,也可以運(yùn)行在SPI模式。我選擇這一課題的原因主要是目前我所在的實(shí)驗(yàn)室需要寫(xiě)基于UART的快速通信。這一

2022-10-24 10:55:09 1746

1746 架構(gòu)、嵌入式系統(tǒng)、實(shí)時(shí)操作系統(tǒng)、數(shù)字信號(hào)處理、圖像與視頻處理和數(shù)字通信等,可以實(shí)現(xiàn)片上課程理念。七、教學(xué)大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的課程安排如下: 第一天 課程目標(biāo)

2009-07-21 09:22:42

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開(kāi)頭和末尾時(shí)刻卻無(wú)法由

2012-08-11 16:22:49

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開(kāi)頭和末尾時(shí)刻卻無(wú)法由

2012-08-11 17:44:43

在FPGA圖像處理中矩陣提取是個(gè)有趣的東東,本文僅限個(gè)人DIY,是否具有工程價(jià)值不做論述,權(quán)當(dāng)一樂(lè)。無(wú)處不在的line buffer現(xiàn)在FPGA圖像處理中,凡事?tīng)可娴骄仃囘\(yùn)算的算法里面基本都有l(wèi)ine

2022-07-15 14:51:07

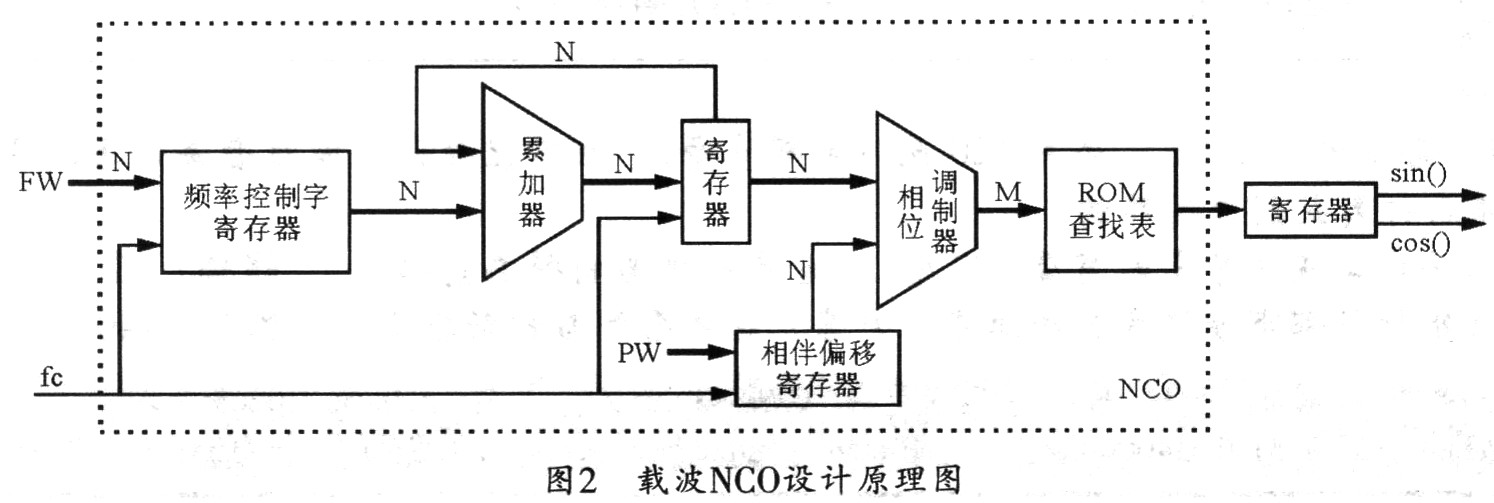

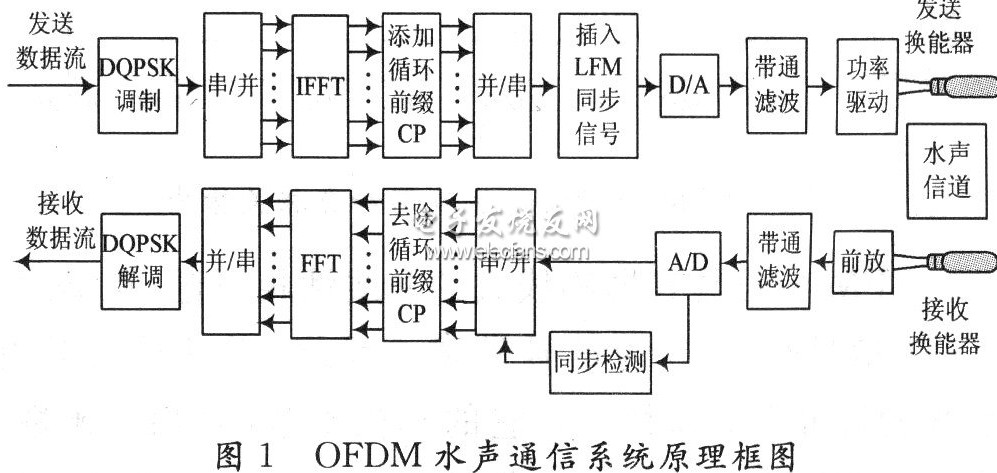

本文主要介紹各部分的算法方案及電路實(shí)現(xiàn)時(shí)所用的FPGA元件的基本結(jié)構(gòu)、設(shè)計(jì)思路。最后通過(guò)對(duì)電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿(mǎn)足多載波傳輸系統(tǒng)的同步要求。

2021-05-07 06:52:34

架構(gòu)、嵌入式系統(tǒng)、實(shí)時(shí)操作系統(tǒng)、數(shù)字信號(hào)處理、圖像與視頻處理和數(shù)字通信等,可以實(shí)現(xiàn)片上課程理念。七、教學(xué)大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的課程安排如下:第一天 課程目標(biāo)

2009-07-21 09:20:11

模塊的算法和FPGA實(shí)現(xiàn)進(jìn)行詳細(xì)探討,內(nèi)容涵蓋一個(gè)完整無(wú)線通信系統(tǒng)的絕大部分模塊,包括擾碼、編碼、交織、OFDM調(diào)制/解調(diào)、幀同步、頻偏校正、符號(hào)同步、采樣時(shí)鐘同步、信道均衡、viterbi解碼等

2012-11-02 11:09:37

同步,就不能正確的提取信息,導(dǎo)致通信失敗。本文主要講述了CDMA碼元同步的FPGA的實(shí)現(xiàn)。首先介紹國(guó)內(nèi)外CDMA擴(kuò)頻通信技術(shù)的發(fā)展趨勢(shì)。然后介紹了modelsim和quartus II開(kāi)發(fā)工具

2015-10-16 21:39:57

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個(gè)同步系統(tǒng),以實(shí)現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。一個(gè)簡(jiǎn)單的接收系統(tǒng)框圖如圖1所示。

2019-09-17 06:28:08

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個(gè)同步系統(tǒng),以實(shí)現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。

2019-09-19 07:28:51

基于FPGA的CAN總線通信系統(tǒng)為了克服單片機(jī)固有的缺陷, 滿(mǎn)足航天控制的需求, 文章提出了如何利用FPGA采用查詢(xún)的方式控制CAN控制器SJA1000,從而實(shí)現(xiàn)CAN總線數(shù)據(jù)通信的方法; 介紹了

2012-08-11 11:55:19

基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn){:soso_e129:}文章下載鏈接:http://www.3532n.com/soft/5/2012/20120518272336.html

2012-05-22 22:33:59

驗(yàn)證也稱(chēng)版圖后仿真,它是在FPGA實(shí)現(xiàn)之后,提取出門(mén)級(jí)網(wǎng)表和延時(shí)信息進(jìn)行驗(yàn)證,測(cè)試平臺(tái)文件與行為級(jí)一樣。器件驗(yàn)證結(jié)果是比較接近真實(shí)硬件的結(jié)果。完全通過(guò)這3層的驗(yàn)證,基本上可以保證設(shè)計(jì)的結(jié)果與測(cè)試平臺(tái)

2019-04-25 07:00:05

、野外試驗(yàn)以及生產(chǎn)應(yīng)用,證明結(jié)合FPGA技術(shù),時(shí)鐘恢復(fù)和系統(tǒng)同步技術(shù)在地震勘探儀器中具有獨(dú)到的優(yōu)勢(shì),其精度可達(dá)us級(jí),而且穩(wěn)定,實(shí)現(xiàn)方便。地震勘探儀器是一個(gè)高度集成的網(wǎng)絡(luò)采集系統(tǒng),在這些地震勘探儀器中

2019-06-18 08:15:35

單片機(jī)的串行通信。實(shí)現(xiàn)了任意字體、16×16 到64×64 不同點(diǎn)陣格式的字模的提取,軟件仿真可以全面的觀察出上位機(jī)字模數(shù)據(jù)的傳送以及單片機(jī)對(duì)于數(shù)據(jù)的接收及存儲(chǔ)情況,為單片機(jī)應(yīng)用開(kāi)發(fā)提供了一種新的方法和手段。關(guān)鍵詞:字模提取;串行通信;VB;Proteus;聯(lián)合仿真;

2009-06-28 01:12:37

1990年,美國(guó)海軍實(shí)驗(yàn)室研究人員Pecora和Carroll首次利用驅(qū)動(dòng)一響應(yīng)法實(shí)現(xiàn)了兩個(gè)混沌的同步后,混沌同步技術(shù)和混沌保密通信成為國(guó)際、國(guó)內(nèi)通信領(lǐng)域的一個(gè)研究熱點(diǎn)。國(guó)際上相繼提出了各種混沌通信

2019-09-27 07:04:30

我想做多個(gè)FPGA的時(shí)鐘同步,目前的想法是用一個(gè)FPGA的內(nèi)部時(shí)鐘,復(fù)制到外接IO口,接到另一個(gè)FPGA的外部時(shí)鐘引腳,波形有較小的相移但是可以保證同步。想問(wèn)一下可以復(fù)制多次,驅(qū)動(dòng)多個(gè)FPGA的同步嗎。對(duì)驅(qū)動(dòng)能力有什么要求?其中每一個(gè)FPGA都用的是一個(gè)EP4CE的最小系統(tǒng)板。

2019-01-21 15:07:41

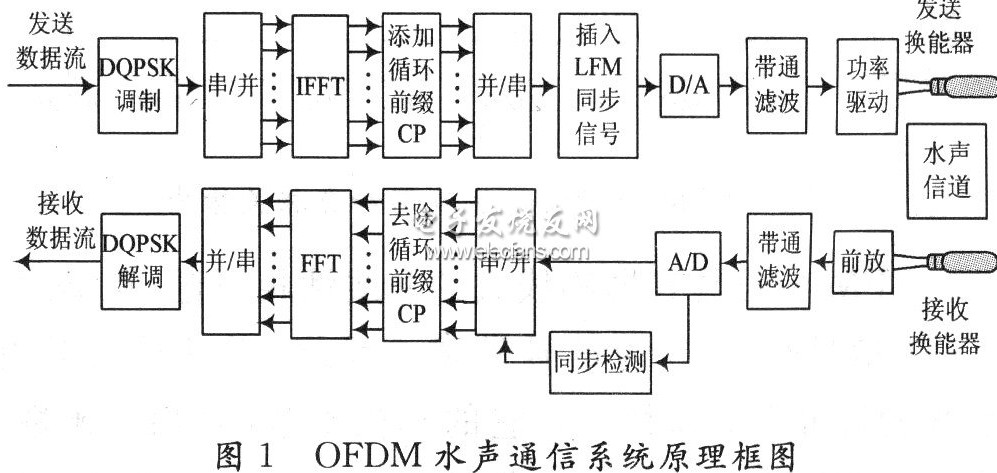

時(shí)、空、頻變的多徑信道,它具有強(qiáng)多徑、窄頻帶和強(qiáng)噪聲等特點(diǎn),將OFDM傳輸技術(shù)應(yīng)用到水聲通信中,實(shí)現(xiàn)OFDM水聲通信系統(tǒng)定時(shí)同步,已成為水聲通信的研究熱點(diǎn)之一,那我們具體該怎么做呢?

2019-08-01 06:52:06

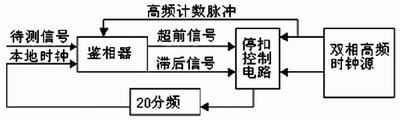

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時(shí)鐘信號(hào)不僅用于監(jiān)測(cè)輸入碼元信號(hào),確保收發(fā)同步,而且在獲取幀同步及對(duì)接收的數(shù)字碼元進(jìn)行各種處理的過(guò)程中也為系統(tǒng)提供了一個(gè)基準(zhǔn)

2019-08-05 06:43:01

,共同進(jìn)步。

歡迎加入FPGA技術(shù)微信交流群14群!

交流問(wèn)題(一)

Q:用FPGA實(shí)現(xiàn)一個(gè)通信系統(tǒng)(5GHz頻段,通信距離越10km)的發(fā)射端&接收機(jī),如何規(guī)劃學(xué)習(xí)路線?

完全0

2024-09-10 19:15:14

自適應(yīng)律,基于線性矩陣不等式技術(shù)給出了其指數(shù)同步的充分條件.利用所提出的指數(shù)同步方法解決了保密通信問(wèn)題,且更符合實(shí)際情況.所設(shè)計(jì)的控制器是實(shí)用有效,易于實(shí)現(xiàn).仿真示例驗(yàn)證了該方法的有效性【關(guān)鍵詞

2010-04-24 09:29:07

基于ZC序列的時(shí)頻域同步的FPGA實(shí)現(xiàn),題目沒(méi)有什么具體要求,通信系統(tǒng)只要設(shè)計(jì)收發(fā)就可以,信道直接用高斯白噪聲信道就可以。要求有matlab仿真驗(yàn)證和FPGa實(shí)現(xiàn)和仿真,不需要實(shí)物,有大神可以幫忙嘛,價(jià)錢(qián)可以商量。

2017-04-13 14:19:04

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時(shí)鐘的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。

2021-05-06 08:00:46

本帖最后由 eehome 于 2013-1-5 10:05 編輯

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 12:37:13

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 11:48:16

最近有個(gè)項(xiàng)目,要在一個(gè)芯片上取數(shù)據(jù),數(shù)據(jù)通信方式是I2C,我用fpga 與芯片通信,但是問(wèn)題來(lái)了?怎么看芯片的數(shù)據(jù),當(dāng)然是弄個(gè)上位機(jī)啦,但是fpga怎么和PC通信呢?我想起了單片機(jī)的u***串口通信

2014-10-17 21:21:26

充電嗎?問(wèn)題二:這是一個(gè)同步電荷提取電荷,想提取的是電容C1、C5、C3上電壓達(dá)到最大時(shí),把能量存儲(chǔ)到電感上。我仿真的結(jié)果,并沒(méi)有實(shí)現(xiàn)電壓突然降下來(lái)的功能。仿真如圖2.從理論分析上,當(dāng)VC5的電壓比

2017-01-10 19:24:18

幀同步系統(tǒng)的工作原理是什么?幀同步系統(tǒng)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2021-04-28 07:20:21

是整個(gè)溫控系統(tǒng)的硬件基礎(chǔ),其中涉及到溫度采集,與微處理器通信,串口輸出,控制數(shù)模轉(zhuǎn)換芯片等多個(gè)組成部分。本文提出一種高效實(shí)用的FPGA接口設(shè)計(jì),它能夠完成協(xié)調(diào)各個(gè)組成部分有序工作,準(zhǔn)確、快速實(shí)現(xiàn)數(shù)據(jù)傳輸

2020-08-19 09:29:48

基于4通道DDS器件AD9959實(shí)現(xiàn)測(cè)控通信系統(tǒng)的同步設(shè)計(jì)

2020-12-23 06:31:18

系統(tǒng)中,碼元同步對(duì)于實(shí)現(xiàn)信號(hào)的準(zhǔn)確判決碼元和降低系統(tǒng)誤碼率起著關(guān)鍵作用。本文介紹了在ADS仿真環(huán)境下實(shí)現(xiàn)16QAM接收機(jī)碼元同步算法。采用的定時(shí)誤差提取算法消除了傳統(tǒng)算法在16QAM系統(tǒng)中引起的時(shí)鐘抖動(dòng)

2019-06-27 06:04:50

針對(duì)計(jì)算機(jī)行同步信號(hào)產(chǎn)生的泄露發(fā)射信息問(wèn)題,提出一種提取該信息的相關(guān)檢測(cè)算法,介紹利用Matlab仿真軟件模擬提取行同步的策略,給出該算法在數(shù)字信號(hào)處理上的具體實(shí)現(xiàn)過(guò)

2009-04-09 09:06:21 21

21

字模提取及基于Proteus 的串行通信仿真::采用掃描VB 圖片框的方法提取字模,并利用VB、Proteus 和Keil 軟件聯(lián)合仿真了上位機(jī)和51 單片機(jī)的串行通信。實(shí)現(xiàn)了任意字體、16×16

2009-06-21 22:44:43 0

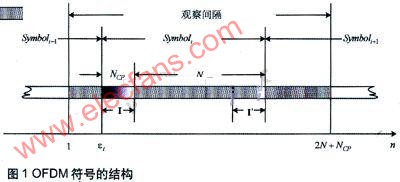

0 基于FPGA 的OFDM 寬帶數(shù)據(jù)通信同步系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):正交頻分復(fù)用(OFDM)是第四代移動(dòng)通信的核心技術(shù),本文介紹了一種基于FPGA的OFDM 寬帶數(shù)據(jù)通信同步系統(tǒng)的設(shè)計(jì)方案,該方案為OFDM

2009-06-25 08:18:06 44

44 對(duì)系統(tǒng)進(jìn)行軟件可定義的仿真是進(jìn)行通用性仿真的重要舉措,在仿真中實(shí)現(xiàn)對(duì)系統(tǒng)眾多參數(shù)方便、精確的軟件控制與調(diào)整是其必然需求與核心技術(shù)所在。本文針對(duì)通信系統(tǒng)軟件可

2009-08-24 09:40:37 8

8 無(wú)人機(jī)仿真系統(tǒng)把高度方向的運(yùn)動(dòng)參數(shù)轉(zhuǎn)化為水平方向的運(yùn)動(dòng)參數(shù),使得運(yùn)動(dòng)狀態(tài)容易控制。仿真系統(tǒng)的實(shí)時(shí)控制要求上位機(jī)與下位機(jī)之間實(shí)現(xiàn)高速數(shù)據(jù)通信,本系統(tǒng)設(shè)計(jì)了合理

2009-12-12 14:00:59 45

45 從時(shí)分復(fù)接系統(tǒng)對(duì)位同步系統(tǒng)的性能要求出發(fā),提出了一種基于FPGA的快速位同步系統(tǒng)的設(shè)計(jì)方案,給出了位同步系統(tǒng)的實(shí)驗(yàn)仿真,結(jié)果表明該系統(tǒng)有較快的位同步建立時(shí)間,節(jié)省了F

2010-07-28 18:13:40 22

22 本文設(shè)計(jì)了一種在數(shù)字通信系統(tǒng)中的數(shù)字鎖相位同步提取方案,詳細(xì)介紹了本設(shè)計(jì)的位同步提取原理及其各個(gè)組成功能模塊的VHDL語(yǔ)言實(shí)現(xiàn),并在Quartus II開(kāi)發(fā)平臺(tái)上仿真驗(yàn)證通過(guò)。本

2010-08-06 14:28:08 64

64 從時(shí)分復(fù)接系統(tǒng)對(duì)幀同步系統(tǒng)的性能要求出發(fā),提出了一種采用FPGA實(shí)現(xiàn)幀同步系統(tǒng)的設(shè)計(jì)方案,重點(diǎn)介紹了同步保護(hù)電路的設(shè)計(jì),并給出了FPGA設(shè)計(jì)的實(shí)驗(yàn)仿真,實(shí)驗(yàn)結(jié)果表明該電路

2010-08-06 16:46:59 24

24 為了滿(mǎn)足某測(cè)控平臺(tái)的設(shè)計(jì)要求,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計(jì)、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

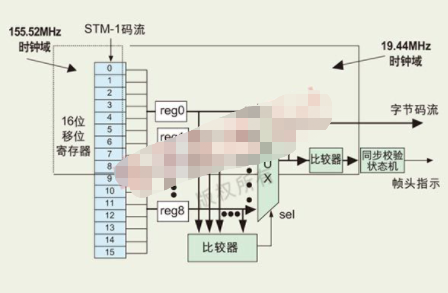

43 為實(shí)現(xiàn)設(shè)備中存在的低速數(shù)據(jù)光纖通信的同步復(fù)接/ 分接,提出一種基于FPGA 的幀同步頭信號(hào)提取檢測(cè)方案,其中幀頭由7 位巴克碼1110010 組成,在數(shù)據(jù)的接收端首先從復(fù)接數(shù)據(jù)中

2010-10-26 16:56:54 46

46 摘 要:本文主要介紹了基于FPGA技術(shù)實(shí)現(xiàn)與PC串行通信的過(guò)程,給出了各個(gè)模塊的具體實(shí)現(xiàn)方法,分析了實(shí)現(xiàn)結(jié)果,驗(yàn)證了串行通信的正確性。引言串行通信即

2006-03-24 13:31:51 5010

5010

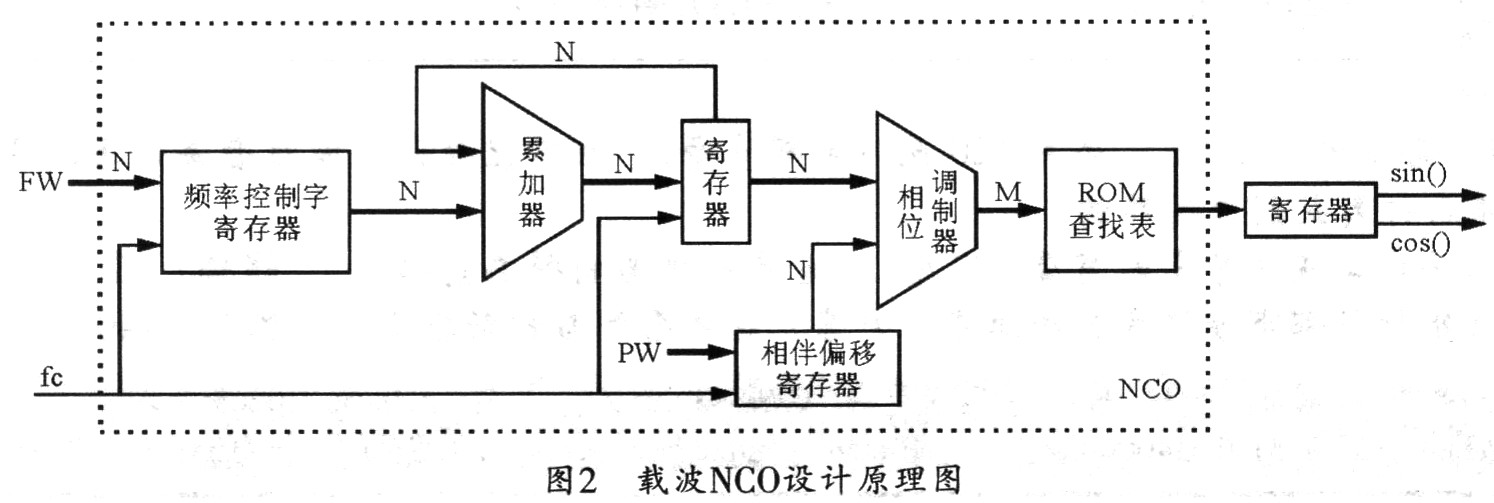

直擴(kuò)OQPSK系統(tǒng)載波跟蹤的 設(shè)計(jì)及FPGA實(shí)現(xiàn)

0 引言??? 載波同步是無(wú)線通信系統(tǒng)中一個(gè)重要的實(shí)際問(wèn)題,是基帶信號(hào)處理的關(guān)鍵技術(shù)。導(dǎo)致載波頻率及相位不

2009-12-12 11:32:02 1976

1976

基于FPGA的提取位同步時(shí)鐘DPLL設(shè)計(jì)

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時(shí)鐘信號(hào)不僅用于監(jiān)測(cè)輸入碼元信號(hào),確保收發(fā)

2010-01-25 09:36:18 3699

3699

基于FPGA的新型誤碼測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

本文設(shè)計(jì)實(shí)現(xiàn)了一種用于測(cè)量基帶傳輸信道的誤碼儀,闡述了主要模塊的工作原理,提出了一種新的積分鑒相同步時(shí)鐘提取的實(shí)

2010-02-09 10:42:01 1172

1172

基于802.16d的定時(shí)同步算法改進(jìn)及FPGA實(shí)現(xiàn)

0 引言

WiMAX ( Wordwide Interoperability for Mi-crowave Access)是代表空中接口滿(mǎn)足IEEE 802.16標(biāo)準(zhǔn)的寬帶無(wú)線通信系統(tǒng)。其

2010-02-22 09:38:31 1106

1106

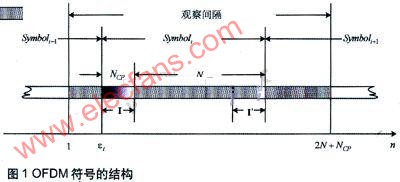

基于循環(huán)前綴的同步算法及FPGA實(shí)現(xiàn)

正交頻分復(fù)用(OrthogonalFrequency Division Multiplexing,OFDM)技術(shù)已經(jīng)成為第四代移動(dòng)通信研究的熱點(diǎn),同時(shí),OFDM同步又是OFDM的關(guān)鍵技

2010-03-23 09:27:48 1923

1923

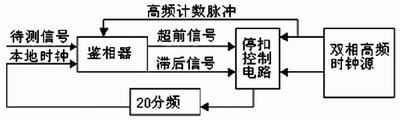

基于fpga的鎖相環(huán)位同步提取電路

該電路如圖所示,它由雙相高頻時(shí)鐘

2010-10-08 12:00:23 1743

1743

摘要:同步接口是光纖縱差保護(hù)裝置的重要組成部分,本文介紹了Cyclone II FPGA 在光纖縱差保護(hù)同步接口中的應(yīng) 用,詳細(xì)地闡述了FPGA 實(shí)現(xiàn)光纖縱差保護(hù)同步通信接口的原理。大規(guī)模可編

2011-04-06 16:42:11 40

40 為改變?nèi)珨?shù)字仿真實(shí)時(shí)性不足并簡(jiǎn)化DSP編程,提出了一種永磁同步電機(jī)HIL實(shí)時(shí)仿真方法。詳細(xì)設(shè)計(jì)了系統(tǒng)硬件,構(gòu)建了永磁同步電機(jī)的數(shù)學(xué)及HIL仿真模型

2011-04-22 16:14:20 89

89 本文闡述了主同步搜索的改進(jìn)型算法,并且針對(duì)這種算法提出了基于片上RAM 的實(shí)現(xiàn)方式,最大程度地節(jié)省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實(shí)現(xiàn)提供了很好的解決方案。這種技術(shù)可

2011-05-14 16:45:53 30

30 由于線性調(diào)頻信號(hào)具有良好的時(shí)頻聚集性,使得LFM信號(hào)適合作為OFDM水聲通信系統(tǒng)的定時(shí)同步信號(hào)。在接收端,利用LFM信號(hào)的自相關(guān)特性檢測(cè)其相關(guān)峰的位置,可以實(shí)現(xiàn)OFDM水聲通信系統(tǒng)的

2011-09-15 18:04:17 3818

3818

無(wú)線信道仿真和均衡器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2011-10-09 18:11:37 40

40 基于Map-X的微波通信規(guī)劃仿真系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2011-11-03 18:05:00 36

36 導(dǎo)頻疊加OFDM同步方法的FPGA實(shí)現(xiàn),目前正交頻分復(fù)用(OFDM)技術(shù)已經(jīng)成為第四代移動(dòng)通信研究的熱點(diǎn),同時(shí)OFDM同步又是OFDM的關(guān)鍵技術(shù)

2012-02-20 15:15:39 2575

2575

本文針對(duì)128 QAM調(diào)制信號(hào),設(shè)計(jì)了定時(shí)同步算法結(jié)構(gòu),并且用MATLAB做了仿真驗(yàn)證,最后在FPGA平臺(tái)上實(shí)現(xiàn)了該算法。

2012-11-23 11:15:17 7614

7614 同步技術(shù)是跳頻系統(tǒng)的核心。本文針對(duì)FPGA的跳頻系統(tǒng),設(shè)計(jì)了一種基于獨(dú)立信道法,同步字頭法和精準(zhǔn)時(shí)鐘相結(jié)合的快速同步方法,同時(shí)設(shè)計(jì)了基于雙圖案的改進(jìn)型獨(dú)立信道法,同步算

2013-05-06 14:09:20 22

22 基于FPGA的幀同步器的設(shè)計(jì)與仿真。。。。

2016-01-04 15:31:55 25

25 基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計(jì)與實(shí)現(xiàn)

2016-01-04 17:03:55 11

11 dac0832ad08098259a,825382508255等芯片的fpga實(shí)現(xiàn)及仿真

2016-01-20 15:12:47 13

13 位同步提取實(shí)驗(yàn)的實(shí)驗(yàn)報(bào)告,位同步提取實(shí)驗(yàn)的實(shí)驗(yàn)報(bào)告,位同步提取實(shí)驗(yàn)的實(shí)驗(yàn)報(bào)告

2016-05-26 10:58:41 0

0 三維掃描圖像光帶中心線提取的FPGA實(shí)現(xiàn),下來(lái)看看

2016-09-17 07:29:56 17

17 同步異步通信轉(zhuǎn)換的CPLD_FPGA設(shè)計(jì),有需要的下來(lái)看看

2016-12-16 22:13:20 8

8 為了能在GPS接收端獲取正確導(dǎo)航電文,研究了CJPS接收機(jī)位同步、幀同步的基本原理和實(shí)現(xiàn)方式。提出一種采用FPGA來(lái)實(shí)現(xiàn)位同步、幀同步系統(tǒng)的設(shè)計(jì)方案。使用Xilinx開(kāi)發(fā)軟件,通過(guò)Verilog代碼

2017-11-07 17:13:39 12

12 Madab仿真數(shù)字通信系統(tǒng)具有較強(qiáng)的可實(shí)現(xiàn)性,為實(shí)際應(yīng)用和科學(xué)合理地設(shè)計(jì)QAM通信系統(tǒng),提供了高效的仿真平臺(tái)。 2 QAM系統(tǒng)仿真 Simulink的通信模塊中有各種數(shù)字調(diào)制/解調(diào)器模塊。其有通帶( passhand)模塊和基帶(baseband)之分。通帶仿真的載波信號(hào)包含在模型的發(fā)

2017-11-16 16:57:54 28

28 信息提取模塊,并且在XST(Xilinx官方綜合工具)以及Synplify pro兩個(gè)綜合環(huán)境下進(jìn)行了仿真驗(yàn)證。通過(guò)對(duì)比仿真結(jié)果的差異,嘗試分析設(shè)計(jì)的寄存器傳輸級(jí)視圖(RTL視圖),并找出了影響狀態(tài)機(jī)工作的關(guān)鍵要素。強(qiáng)調(diào)了代碼風(fēng)格對(duì)FPGA設(shè)計(jì)的重要性。

2017-11-17 06:04:02 2595

2595

介紹了精密時(shí)鐘同步協(xié)議(PTP)的原理。本文精簡(jiǎn)了該協(xié)議,設(shè)計(jì)并實(shí)現(xiàn)了一種低成本、高精度的時(shí)鐘同步系統(tǒng)方案。該方案中,本地時(shí)鐘單元、時(shí)鐘協(xié)議模塊、發(fā)送緩沖、接收緩沖以及系統(tǒng)打時(shí)標(biāo)等功能都在FPGA中

2017-11-17 15:57:18 8779

8779

信號(hào)中的調(diào)制載波同頻同相的相干載波。這個(gè)載波的獲取稱(chēng)為載波提取或載波同步。在第4章的模擬調(diào)制以及第 7 章的數(shù)字調(diào)制學(xué)習(xí)過(guò)程中,我們了解到要想實(shí)現(xiàn)相干解調(diào),必須有相干載波。因此,載波同步是實(shí)現(xiàn)相干解調(diào)的先決條件。 (2)

2017-11-24 09:31:43 0

0 對(duì)直接擴(kuò)頻通信同步系統(tǒng)進(jìn)行了研究,使用PN碼作為擴(kuò)頻序列,利用其良好的自相關(guān)性,提出一種新式的滑動(dòng)相關(guān)法使收發(fā)端同步,并給出該系統(tǒng)的FPGA實(shí)現(xiàn)方法。利用ISE 10.1開(kāi)發(fā)軟件仿真驗(yàn)證,證明此

2017-11-24 16:16:01 1734

1734 、可靠的遙測(cè)同步和信道編碼系統(tǒng)。系統(tǒng)不僅降低了信號(hào)傳輸誤碼率,提高了數(shù)據(jù)傳輸?shù)目煽啃裕瑫r(shí)降低了硬件實(shí)現(xiàn)的復(fù)雜度并減少了資源消耗。實(shí)驗(yàn)結(jié)果標(biāo)明:該系統(tǒng)在占用資源較少的情況下,能準(zhǔn)確地完成遙測(cè)數(shù)據(jù)的同步和信道編碼,吞吐量可達(dá)72 Mbps,滿(mǎn)足深空通信要求。

2018-01-09 15:36:39 1

1 數(shù)字通信系統(tǒng)中,碼元同步對(duì)于實(shí)現(xiàn)信號(hào)的準(zhǔn)確判決碼元和降低系統(tǒng)誤碼率起著關(guān)鍵作用。本文介紹了在ADS仿真環(huán)境下實(shí)現(xiàn)16QAM接收機(jī)碼元同步算法。

2018-05-18 10:32:00 5273

5273

,給出核心模塊的設(shè)計(jì)電路圖和仿真結(jié)果。仿真結(jié)果表明:基于靈活自適應(yīng)空口波形技術(shù)可以在FPGA上實(shí)現(xiàn),而且由于FPGA具有天然的并行性,實(shí)際的通信系統(tǒng)中可以采用并發(fā)模式進(jìn)行,達(dá)到提高信號(hào)傳送速率的目的。

2018-07-23 17:21:00 3003

3003

一般的位同步電路大多采用標(biāo)準(zhǔn)邏輯器件按傳統(tǒng)數(shù)字系統(tǒng)設(shè)計(jì)方法構(gòu)成,具有功耗大,可靠性低的缺點(diǎn)。用FPGA設(shè)計(jì)電路具有很高的靈活性和可靠性,可以提高集成度和設(shè)計(jì)速度,增強(qiáng)系統(tǒng)的整體性能。本文給出了一種基于fpga的數(shù)字鎖相環(huán)位同步提取電路。

2019-04-19 08:24:00 4279

4279

在Altera Cyclone II 平臺(tái)上采用“自頂向下”的模塊化設(shè)計(jì)思想及VHDL 硬件描述語(yǔ)言,設(shè)計(jì)了串行通信控制系統(tǒng)。在Quartus II 軟件上編譯、仿真后下載到FPGA 芯片

2018-11-07 11:18:23 6

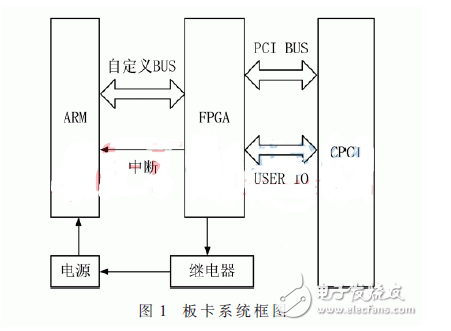

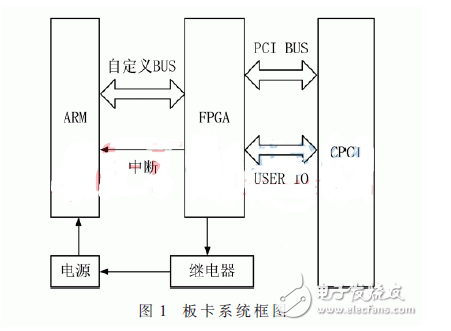

6 本文提出了一種基于FPGA的CPCI系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),使用廉價(jià)FPGA芯片實(shí)現(xiàn)CPCI通信協(xié)議,同時(shí)利用FPGA的可編程特性實(shí)現(xiàn)電源控制、靈活中斷、外部觸發(fā)、外部通信等特殊應(yīng)用的功能,解決了CPCI協(xié)議經(jīng)過(guò)CPCI橋時(shí)的沖突問(wèn)題。

2019-01-06 11:37:13 3401

3401

數(shù)字通信系統(tǒng)中,碼元同步對(duì)于實(shí)現(xiàn)信號(hào)的準(zhǔn)確判決碼元和降低系統(tǒng)誤碼率起著關(guān)鍵作用。本文介紹了在ADS仿真環(huán)境下實(shí)現(xiàn)16QAM接收機(jī)碼元同步算法。采用的定時(shí)誤差提取算法消除了傳統(tǒng)算法在16QAM系統(tǒng)中

2020-08-28 10:48:00 1

1 采用現(xiàn)場(chǎng)可編程門(mén)陣列FPGA實(shí)現(xiàn)軟件無(wú)線電技術(shù),控制和調(diào)整擴(kuò)頻通信系統(tǒng)的同步性能。該系統(tǒng)介紹了用FPGA實(shí)現(xiàn)對(duì)采樣信號(hào)正交數(shù)字下變頻,完成同步搜索和頻偏估計(jì),以及糾正載波頻偏和調(diào)整碼元速率,同步跟蹤

2020-07-27 16:53:15 14

14 通過(guò)對(duì)功率利用率,誤碼率,帶寬效率以及實(shí)現(xiàn)電路的復(fù)雜程度進(jìn)行比較,選用定長(zhǎng)數(shù)字脈沖間隔調(diào)制作為紫外光通信的調(diào)制解調(diào)方法,基于XILINX可編程邏輯器件XC4VSX35 FPGA設(shè)計(jì)實(shí)現(xiàn)了一個(gè)紫外光通信的調(diào)制解調(diào)系統(tǒng),詳細(xì)介紹了此調(diào)制解調(diào)系統(tǒng)的實(shí)現(xiàn)過(guò)程。ModeI Sim的仿真結(jié)果證明了該設(shè)計(jì)的正確性。

2021-04-01 10:54:04 10

10 基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)的講解。

2021-05-25 16:26:19 29

29 基于FPGA的無(wú)線通信系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2021-06-16 09:59:29 46

46 ,首先要從同步數(shù)據(jù)流中提取幀同步信息,幀同步提取性能的優(yōu)劣直接影響整個(gè)數(shù)據(jù)的處理質(zhì)量與整個(gè)系統(tǒng)的性能。使用FPGA技術(shù)可以實(shí)現(xiàn)同步系統(tǒng)的模塊化、小型化和芯片化,得到穩(wěn)定可靠的幀同步器。

2021-06-23 15:44:00 4152

4152

在無(wú)線通信系統(tǒng)中,普遍使用擴(kuò)頻通信技術(shù),因此擴(kuò)頻技術(shù)對(duì)通信系統(tǒng)具有重要的現(xiàn)實(shí)意義。直接序列擴(kuò)頻技術(shù)是應(yīng)用最廣的一種擴(kuò)頻技術(shù),FPGA具備高速度的并行性特點(diǎn)在無(wú)線通信系統(tǒng)中的優(yōu)勢(shì)日益增強(qiáng),利用FPGA實(shí)現(xiàn)直接序列擴(kuò)頻技術(shù),可增大傳輸速率,可以使擴(kuò)頻技術(shù)有更好的發(fā)展與應(yīng)用。

2021-07-05 14:29:08 3801

3801

本次的設(shè)計(jì)為多路UART/SPI通信系統(tǒng),可以實(shí)現(xiàn)一對(duì)多的通信。系統(tǒng)可以運(yùn)行在UART模式,也可以運(yùn)行在SPI模式。我選擇這一課題的原因主要是目前我所在的實(shí)驗(yàn)室需要寫(xiě)基于UART的快速通信。這一

2023-02-20 11:10:31 2392

2392 fpga與dsp通訊怎樣同步時(shí)鐘頻率?dsp和fpga通信如何測(cè)試? 在FPGA與DSP通訊時(shí),同步時(shí)鐘頻率非常重要,因?yàn)椴煌脑O(shè)備有不同的時(shí)鐘頻率,如果兩者的時(shí)鐘頻率不同步,會(huì)導(dǎo)致通訊數(shù)據(jù)的錯(cuò)誤或

2023-10-18 15:28:13 2793

2793 電子發(fā)燒友網(wǎng)站提供《基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-24 10:59:21 13

13 Calibre是一種先進(jìn)的電子設(shè)計(jì)自動(dòng)化(EDA)工具,用于電子電路的設(shè)計(jì)和仿真。它為工程師提供了一個(gè)強(qiáng)大的平臺(tái),可以進(jìn)行多個(gè)級(jí)別的仿真,包括電路級(jí)仿真、行為級(jí)仿真和系統(tǒng)級(jí)仿真。在使用Calibre

2024-01-04 17:24:59 2313

2313 FPGA(Field-Programmable Gate Array,現(xiàn)場(chǎng)可編程門(mén)陣列)仿真器接口的定義主要依賴(lài)于仿真器的具體設(shè)計(jì)和所支持的通信協(xié)議。在FPGA的設(shè)計(jì)和仿真過(guò)程中,接口的定義對(duì)于實(shí)現(xiàn)與仿真器、計(jì)算機(jī)或其他設(shè)備的通信至關(guān)重要。

2024-03-15 14:01:46 2800

2800

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論