從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過(guò)將配

2011-10-12 15:16:25 1928

1928

基于eFPGAsim的電機(jī)硬件在環(huán)測(cè)試系統(tǒng),是面向電驅(qū)HIL測(cè)試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術(shù)實(shí)現(xiàn),在獲得基于FPGA片上仿真

2017-08-09 10:52:21 3639

3639

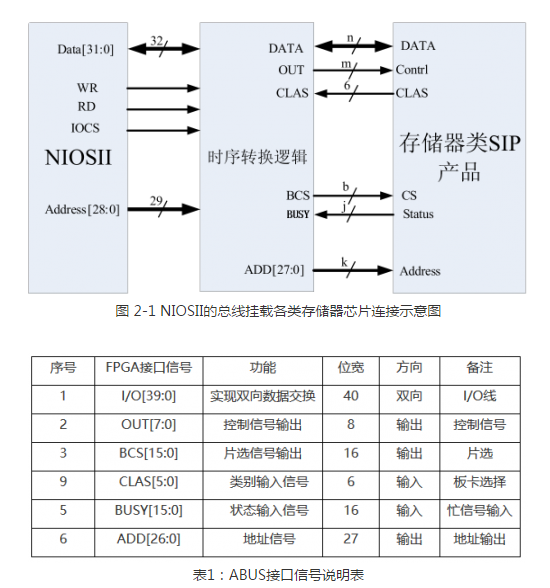

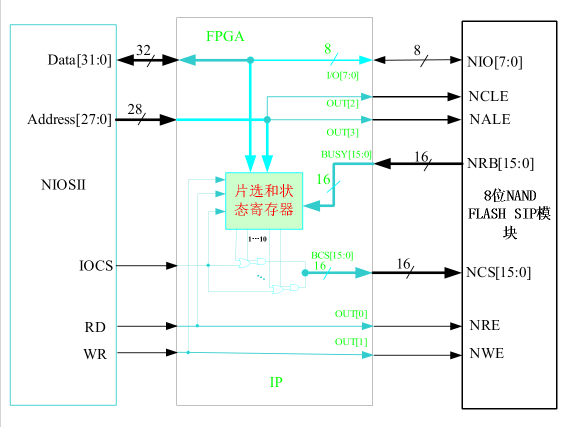

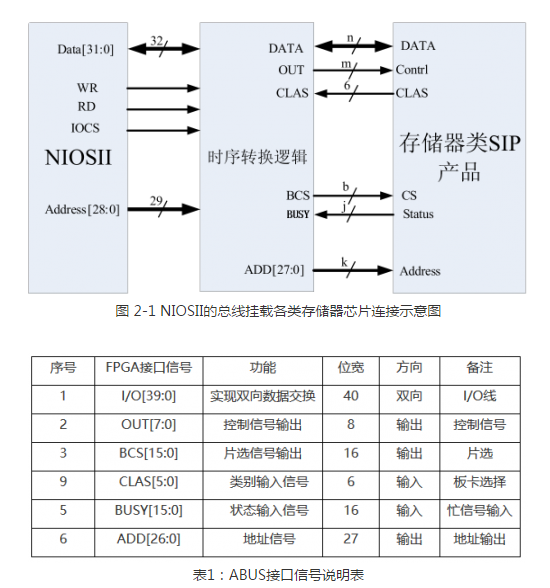

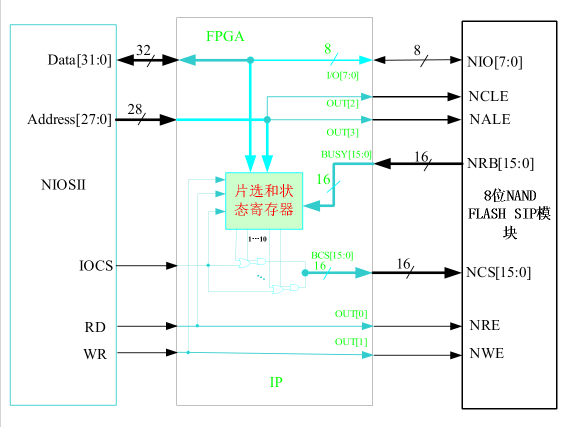

隨著電子技術(shù)的飛速發(fā)展, 存儲(chǔ)器的種類(lèi)日益繁多,每一種存儲(chǔ)器都有其獨(dú)有的操作時(shí)序,為了提高存儲(chǔ)器芯片的測(cè)試效率,一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)應(yīng)運(yùn)而生。本文提出了一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)硬件

2017-08-15 14:00:21 6230

6230

隨著電子技術(shù)的飛速發(fā)展, 存儲(chǔ)器的種類(lèi)日益繁多,每一種存儲(chǔ)器都有其獨(dú)有的操作時(shí)序,為了提高存儲(chǔ)器芯片的測(cè)試效率,一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)應(yīng)運(yùn)而生。本文提出了一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)硬件

2017-12-21 09:20:24 8474

8474

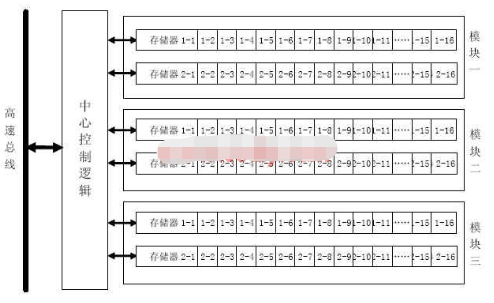

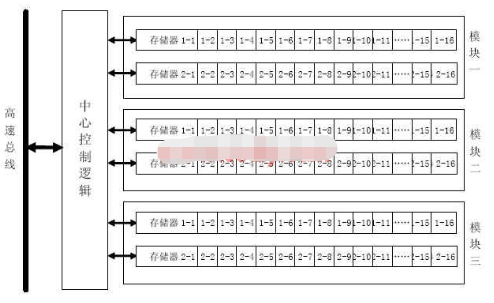

本文介紹了一種以FPGA作為控制器,F(xiàn)LASH MEMORY作為主存儲(chǔ)器的大容量高速存儲(chǔ)系統(tǒng)方案,并對(duì)關(guān)鍵技術(shù)及實(shí)現(xiàn)途徑進(jìn)行了論述,在存儲(chǔ)容量及存儲(chǔ)速度上實(shí)現(xiàn)了突破。

2020-07-30 17:53:54 3062

3062

本篇將詳細(xì)介紹如何利用Verilog HDL在FPGA上實(shí)現(xiàn)SRAM的讀寫(xiě)測(cè)試。SRAM是一種非易失性存儲(chǔ)器,具有高速讀取和寫(xiě)入的特點(diǎn)。在FPGA中實(shí)現(xiàn)SRAM讀寫(xiě)測(cè)試,包括設(shè)計(jì)SRAM接口模塊

2025-10-22 17:21:38 4118

4118

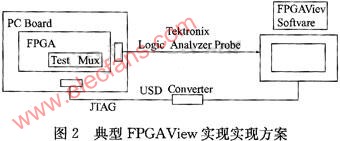

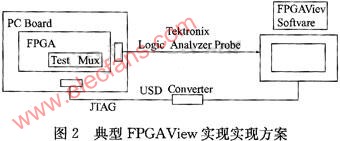

大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。嵌入式邏輯分析工具無(wú)法滿足通用性要求,外部測(cè)試工具可以把FPGA內(nèi)部信號(hào)與實(shí)際電路聯(lián)合起來(lái)觀察系統(tǒng)真實(shí)運(yùn)行情況。隨著FPGA技術(shù)的發(fā)展,大容量、高速

2019-08-07 07:50:15

FPGA在嵌入式測(cè)試系統(tǒng)中的優(yōu)勢(shì)是什么?FPGA在嵌入式測(cè)試系統(tǒng)中的不足是什么?

2021-05-06 07:19:22

FPGA在語(yǔ)音存儲(chǔ)與回放系統(tǒng)中的應(yīng)用是什么

2021-05-06 07:13:11

SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)面對(duì)不同的應(yīng)用場(chǎng)景,原始采樣數(shù)據(jù)可能包含多種不同樣式的信號(hào),這給傳統(tǒng)基于連續(xù)存儲(chǔ)方式的數(shù)據(jù)緩存系統(tǒng)帶來(lái)了挑戰(zhàn)。除此之外,由于對(duì)不同信號(hào)的處理往往需要不同的數(shù)據(jù)

2012-08-13 10:40:40

FPGA可重復(fù)配置和測(cè)試系統(tǒng)結(jié)構(gòu)概述FPGA重復(fù)配置和測(cè)試的實(shí)現(xiàn)

2021-04-29 06:58:20

求大佬分享一款不錯(cuò)的基于FPGA超高速雷達(dá)住處實(shí)時(shí)采集存儲(chǔ)系統(tǒng)

2021-04-15 06:56:25

和朋友開(kāi)發(fā)了幾個(gè)基于 FPGA 的高速存儲(chǔ) IP 核,考慮到工業(yè)相機(jī)等應(yīng)用場(chǎng)合需要有文件系統(tǒng)以方便做數(shù)據(jù)管理,所以將 NVMe 和 exFAT 兩大IP核集成一起,可以實(shí)現(xiàn)將數(shù)據(jù)寫(xiě)入SSD后,拔下

2022-06-03 11:35:06

現(xiàn)代科技對(duì)系統(tǒng)的可靠性提出了更高的要求,而FPGA技術(shù)在電子系統(tǒng)中應(yīng)用已經(jīng)非常廣泛,因此FPGA易測(cè)試性就變得很重要。要獲得的FPGA內(nèi)部信號(hào)十分有限、FPGA封裝和印刷電路板(PCB)電氣噪聲

2019-08-29 07:59:05

的XC6SLX150-2FG484C這款FPGA芯片,其內(nèi)部資源豐富,用戶可用IO數(shù)達(dá)168個(gè),滿足該系統(tǒng)的設(shè)計(jì)需求。2 系統(tǒng)設(shè)計(jì)2.1 總體方案被測(cè)樣機(jī)需對(duì)8個(gè)被測(cè)設(shè)備進(jìn)行循環(huán)測(cè)量與控制,并對(duì)測(cè)量數(shù)據(jù)進(jìn)行記錄判讀、存儲(chǔ)轉(zhuǎn)發(fā)

2018-08-07 10:08:19

設(shè)計(jì)高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲(chǔ)系統(tǒng),就是通過(guò)傳感器采集數(shù)據(jù),通過(guò)FPGA來(lái)控制,把數(shù)據(jù)存儲(chǔ)到存儲(chǔ)芯片上,回頭可以通過(guò)接口讀取數(shù)據(jù)顯示在計(jì)算機(jī)上,求大師給我指導(dǎo),我急需整個(gè)系統(tǒng)的protel原理圖,請(qǐng)各位幫忙,我將感激不盡。最好有附件畫(huà)出整個(gè)原理圖,謝謝!

2012-10-29 21:37:12

吞吐量大、功耗低的需求,因此選擇DDR3 SDRAM作為機(jī)載視頻圖形顯示系統(tǒng)的外部存儲(chǔ)器。本文以Kintex-7系列XC7K410T FPGA芯片和兩片MT41J128M16 DDR3 SDRAM芯片為硬件平臺(tái),設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的視頻圖形顯示系統(tǒng)的DDR3多端口存儲(chǔ)管理。

2019-06-24 06:07:53

要求:該系統(tǒng)將圖像采集、顯示和存儲(chǔ)功能集成到FPGA平臺(tái)上,本設(shè)計(jì)采用NIOS II 設(shè)計(jì)軟核系統(tǒng),通過(guò)FPGA初始化圖像傳感器OV7670,OV7670再等待場(chǎng)同步,行同步,將采集的數(shù)據(jù)在TFT

2012-05-22 09:22:09

安捷倫公司數(shù)字測(cè)試資深技術(shù)/市場(chǎng)工程師 冀衛(wèi)東為滿足日益復(fù)雜的數(shù)字化系統(tǒng)的設(shè)計(jì)要求,FPGA的密度及復(fù)雜性也在急速增長(zhǎng),越來(lái)越多的系統(tǒng)或子系統(tǒng)功能在FPGA內(nèi)部實(shí)現(xiàn),其先進(jìn)的功能和高集成度使FPGA成為極具吸引力的解決方案,進(jìn)而也使得基于內(nèi)核的FPGA測(cè)試方案浮出水面。

2019-07-11 06:15:12

的測(cè)試系統(tǒng)應(yīng)運(yùn)而生。本文提出了一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)硬件設(shè)計(jì)與實(shí)現(xiàn),對(duì)各種數(shù)據(jù)位寬的多種存儲(chǔ)器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)進(jìn)行了詳細(xì)的結(jié)口

2019-07-26 06:53:39

針對(duì)航天測(cè)試系統(tǒng)的應(yīng)用需求,利用FPGA的設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)勢(shì)在必行,那我們具體該怎么做呢?

2019-08-01 08:14:33

請(qǐng)問(wèn)怎么利用FPGA實(shí)現(xiàn)模式可變的衛(wèi)星數(shù)據(jù)存儲(chǔ)器糾錯(cuò)系統(tǒng)?

2021-04-13 06:10:54

怎么實(shí)現(xiàn)基于FPGA的VRLA蓄電池測(cè)試系統(tǒng)的設(shè)計(jì)?

2021-05-10 06:22:19

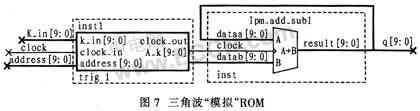

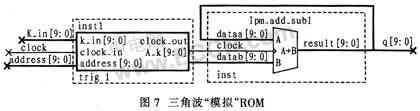

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號(hào)發(fā)生器,一路虛擬存儲(chǔ)示波器,具有外部觸發(fā)信號(hào)和采樣時(shí)鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

本文提出了基于SOPC(System On Programmable Chip)的設(shè)計(jì)方案[2],利 用其配置靈活、擴(kuò)展性強(qiáng)、接口豐富等優(yōu)點(diǎn),以Altera 公司的Cyclone II 系列FPGA 為基 礎(chǔ),設(shè)計(jì)傳感器節(jié)點(diǎn)數(shù)據(jù)采集存儲(chǔ)系統(tǒng),降低了設(shè)計(jì)的風(fēng)險(xiǎn),完善了傳感器節(jié)點(diǎn)功能要求。

2021-05-06 08:28:58

動(dòng)態(tài)測(cè)試技術(shù)是以捕捉和處理各種動(dòng)態(tài)信息為目的的一門(mén)綜合技術(shù),它在當(dāng)代科學(xué)技術(shù)中地位十分重要,在航天航空、儀器儀表、交通運(yùn)輸、軍事、醫(yī)療等研究中均應(yīng)用廣泛。常用的測(cè)試方法有遙測(cè)與存儲(chǔ)測(cè)試,與無(wú)線電遙測(cè)

2019-08-26 06:44:45

基于FPGA的新型數(shù)字微鏡芯片測(cè)試系統(tǒng)是由哪些部分組成的?怎樣去設(shè)計(jì)一種基于FPGA的新型數(shù)字微鏡芯片測(cè)試系統(tǒng)?

2021-11-10 06:05:57

使用高性能數(shù)字存儲(chǔ)示波器主要依靠國(guó)外產(chǎn)品,而且價(jià)格昂貴。因此研究數(shù)字存儲(chǔ)示波器具有重要價(jià)值。借于此,提出了一種簡(jiǎn)易數(shù)字存儲(chǔ)示波器的設(shè)計(jì)方案,經(jīng)測(cè)試,性能優(yōu)良。2 數(shù)字存儲(chǔ)示波器基本工作原理數(shù)字存儲(chǔ)示波器與模擬

2020-02-24 13:52:07

設(shè)計(jì)高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲(chǔ)系統(tǒng),就是通過(guò)傳感器采集數(shù)據(jù),通過(guò)FPGA來(lái)控制,把數(shù)據(jù)存儲(chǔ)到存儲(chǔ)芯片上,回頭可以通過(guò)接口讀取數(shù)據(jù)顯示在計(jì)算機(jī)上,求大師給我指導(dǎo),我急需整個(gè)系統(tǒng)的protel原理圖,請(qǐng)各位幫忙,我將感激不盡。最好有附件畫(huà)出整個(gè)原理圖,謝謝!

2012-10-29 21:29:15

半導(dǎo)體存儲(chǔ)器測(cè)試原理,半導(dǎo)體存儲(chǔ)器的性能測(cè)試,集成電路測(cè)試系統(tǒng).

2008-08-17 22:36:43 169

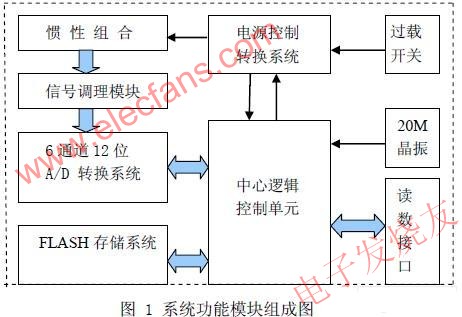

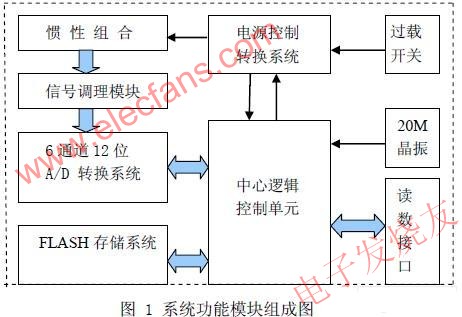

169 基于ATMEL 90 系列單片機(jī)AT90S8515 為系統(tǒng)控制器的過(guò)載存儲(chǔ)測(cè)試儀, 實(shí)現(xiàn)了野外過(guò)載存儲(chǔ)系統(tǒng)的小型化。該過(guò)載存儲(chǔ)測(cè)試儀由傳感器、電荷放大器、模數(shù)轉(zhuǎn)換接口、數(shù)據(jù)存儲(chǔ)器及單片機(jī)

2009-06-19 15:33:42 11

11 本文運(yùn)用黑盒測(cè)試的基本理論,提出了FPGA邏輯設(shè)計(jì)的測(cè)試模型,分析了FPGA邏輯設(shè)計(jì)的基本方法和步驟,最后結(jié)合一個(gè)實(shí)際項(xiàng)目說(shuō)明了FPGA邏輯設(shè)計(jì)的測(cè)試驗(yàn)證過(guò)程。關(guān)鍵詞:黑盒

2009-08-19 09:12:41 9

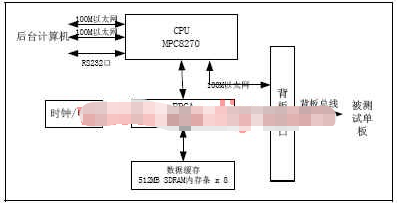

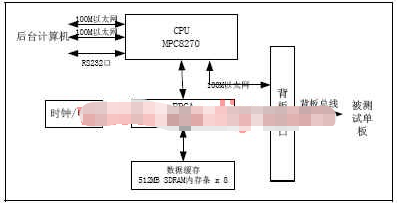

9 本文介紹了基帶測(cè)試系統(tǒng)中,如何應(yīng)用FPGA實(shí)現(xiàn)后臺(tái)計(jì)算機(jī)與測(cè)試環(huán)境數(shù)據(jù)交互以及存儲(chǔ)的電路設(shè)計(jì)流程,并已在某基站測(cè)試系統(tǒng)中成功應(yīng)用。

2010-08-09 15:00:32 27

27 采用大容量的固態(tài)Flash作為存儲(chǔ)介質(zhì),用FPGA作為存儲(chǔ)陣列的控制器,設(shè)計(jì)了高速大容量的存儲(chǔ)板卡,實(shí)現(xiàn)了數(shù)據(jù)采集過(guò)程中用相對(duì)低速的Flash存儲(chǔ)器存儲(chǔ)高速實(shí)時(shí)數(shù)據(jù)。FPGA既可作為

2010-12-08 17:25:08 29

29 設(shè)計(jì)了一種基于FPGA的單板單片主控器件的低成本即插即用虛擬測(cè)試系統(tǒng)。系統(tǒng)包括兩路分立信號(hào)源、一路虛擬存儲(chǔ)示波器和16路高速虛擬邏輯分析儀,結(jié)合FPGA、高速DAC/ADC設(shè)計(jì)特點(diǎn),

2010-12-14 10:07:12 16

16 隨著FPGA設(shè)計(jì)復(fù)雜度的增加,傳統(tǒng)測(cè)試方法受到限制。在高速集成FPGA測(cè)試中,其內(nèi)部信號(hào)的實(shí)時(shí)獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個(gè)

2010-12-17 15:25:17 16

16 為了提高飛行參數(shù)的測(cè)試水平,以完善飛行體的發(fā)射可信度,詳細(xì)論述了一種飛行參數(shù)采編存儲(chǔ)測(cè)試系統(tǒng)的設(shè)計(jì)原理及其應(yīng)用。它采用現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA),通過(guò)編寫(xiě)VHDL程序代

2010-12-20 16:41:01 23

23 設(shè)計(jì)一種基于FPGA的多通道同步數(shù)據(jù)采集存儲(chǔ)系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲(chǔ)模塊。系統(tǒng)設(shè)計(jì)采用多通道數(shù)據(jù)的同步實(shí)時(shí)采集以及壞塊檢測(cè)技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 70

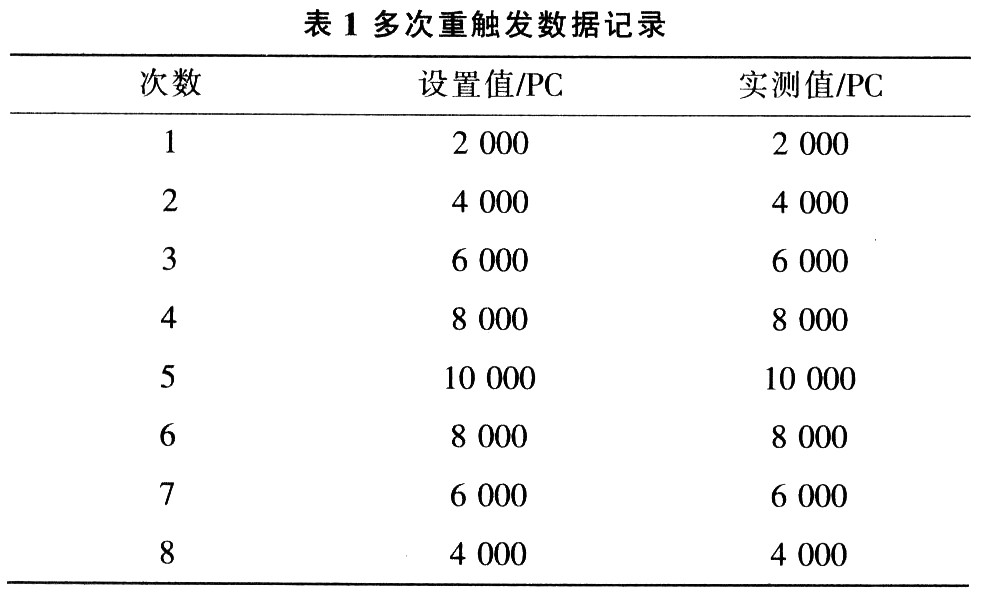

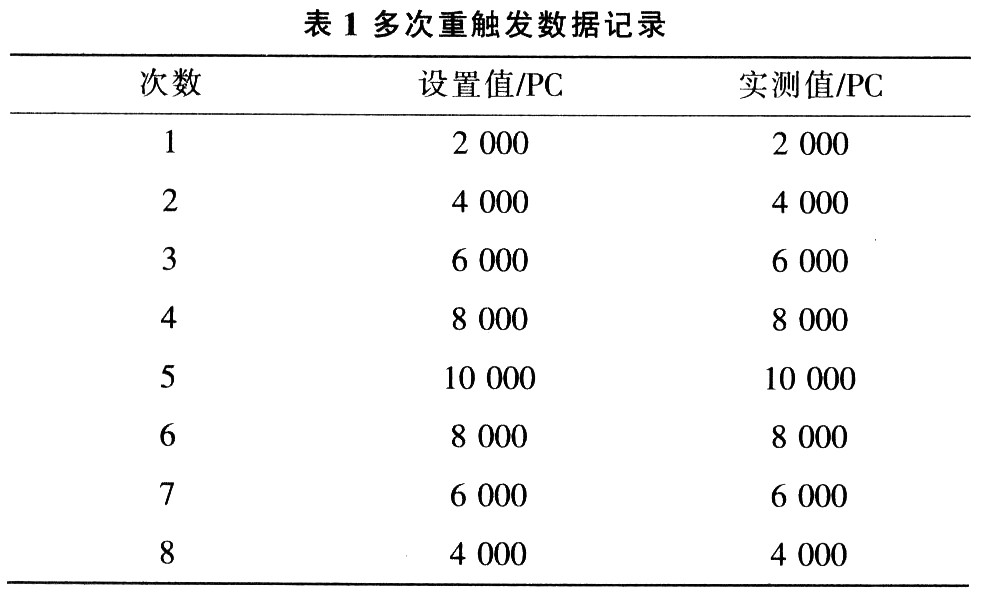

70 提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測(cè)試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制原理,并對(duì)CPLD控制電路仿真。該系統(tǒng)體積小、功耗低,能夠?qū)崟r(shí)記錄多次重觸發(fā)信號(hào)

2010-12-30 16:05:11 22

22 本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板

2009-02-12 11:49:27 778

778

FPGA 重復(fù)配置和測(cè)試的實(shí)現(xiàn)

從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括

2009-09-03 11:17:08 725

725

基于FPGA的微型數(shù)字存儲(chǔ)系統(tǒng)設(shè)計(jì)

1 引言 針對(duì)航天測(cè)試系統(tǒng)的應(yīng)用需求,提出一種基于FPGA的微型數(shù)字存儲(chǔ)系統(tǒng)設(shè)計(jì)方案。該系統(tǒng)是在傳統(tǒng)存儲(chǔ)測(cè)試系統(tǒng)的基

2009-11-04 10:46:38 1113

1113

基于FPGA的空間存儲(chǔ)器糾錯(cuò)系統(tǒng)的設(shè)計(jì)研究

1、引言

阿爾法磁譜儀(Alpha Magnetic Spectrometer,AMS)實(shí)驗(yàn)室是丁肇中博士領(lǐng)導(dǎo)的由美、俄、德、法、中等16個(gè)國(guó)家和

2009-12-18 10:10:07 576

576 FPGA在語(yǔ)音存儲(chǔ)與回放系統(tǒng)中的應(yīng)用

1 引言 隨著數(shù)字信號(hào)處理器、超大規(guī)模集成電路的高速發(fā)展,語(yǔ)音記錄技術(shù)已從模擬錄音階段過(guò)渡到數(shù)字錄音

2010-01-14 11:02:41 1840

1840

FPGA重復(fù)配置和測(cè)試的實(shí)現(xiàn)

從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA

2010-01-26 09:39:56 690

690

采用CPLD的多次重觸發(fā)存儲(chǔ)測(cè)試系統(tǒng)解決方案

概述:提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測(cè)試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制

2010-03-17 11:37:51 835

835

現(xiàn)代科技對(duì)系統(tǒng)的可靠性提出了更高的要求,而FPGA技術(shù)在電子系統(tǒng)中應(yīng)用已經(jīng)非常廣泛,因此FPGA易測(cè)試性就變得很重要。要獲得的FPGA內(nèi)部信號(hào)十分有限、FPGA封裝和印刷電路板(PCB)

2010-08-04 17:35:45 824

824

摘要:本文主要介紹了微型存儲(chǔ)測(cè)試系統(tǒng)在姿態(tài)測(cè)量中的設(shè)計(jì),結(jié)合飛行體在飛行時(shí)各種變化姿態(tài)的采集,編

2010-11-07 10:54:15 1483

1483

本文提出了一種基于文件結(jié)構(gòu)存儲(chǔ)方式的數(shù)據(jù)緩存系統(tǒng),該系統(tǒng)利用FPGA設(shè)計(jì)結(jié)構(gòu)化狀態(tài)機(jī)實(shí)現(xiàn)對(duì)SDRAM的控制,完成

2010-11-25 11:19:03 1442

1442

本文提出了一種基于SoPC的FPGA在線測(cè)試方法,是對(duì)現(xiàn)有FPGA在線測(cè)試方法的一種有效的補(bǔ)充。

2011-04-18 11:46:20 1551

1551

誤碼測(cè)試儀是檢測(cè)通信系統(tǒng)可靠性的重要設(shè)備。傳統(tǒng)的誤碼測(cè)試儀基于CPLD和CPU協(xié)同工作,不僅結(jié)構(gòu)復(fù)雜,價(jià)格昂貴,而且不方便攜帶。基于FPGA的高速誤碼測(cè)試儀,采用FPGA來(lái)完成控制和

2011-05-06 16:03:07 42

42 本文介紹了FPGA外部存儲(chǔ)器的設(shè)計(jì)方法,可以有效地解決雷達(dá)實(shí)時(shí)信號(hào)處理過(guò)程中海量數(shù)據(jù)的存儲(chǔ)問(wèn)題,同時(shí)也可以充分利用FPGA去控制SDRAM和FLASH,不僅保證了資源的充分利用,也可以

2011-08-18 11:46:45 8751

8751

基于對(duì)FPGA系統(tǒng)失效機(jī)理的深入分析, 提出了軟件測(cè)試技術(shù)在FPGA測(cè)試中的應(yīng)用, 并分析了其可行性; 通過(guò)對(duì)比FPGA與軟件系統(tǒng)的異同, 歸納出FPGA特有的測(cè)試要求,從而在軟件測(cè)試技術(shù)的基礎(chǔ)

2011-09-29 17:41:21 65

65 為解決現(xiàn)有采集存儲(chǔ)系統(tǒng)不能同時(shí)滿足高速率采集,大容量脫機(jī)且長(zhǎng)時(shí)間持續(xù)存儲(chǔ)的問(wèn)題,設(shè)計(jì)了一種基于SATA硬盤(pán)和FPGA的數(shù)據(jù)采集和存儲(chǔ)方案。本設(shè)計(jì)由AD9627轉(zhuǎn)換芯片,Altera Cyclone系列

2011-11-15 11:35:19 170

170 傳統(tǒng)測(cè)試測(cè)量?jī)x存在價(jià)格昂貴、體積龐大、數(shù)據(jù)傳輸速率低、存儲(chǔ)顯示困難等問(wèn)題,本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛

2012-05-15 10:45:07 1224

1224

基于FPGA的ADC指標(biāo)測(cè)量及測(cè)試系統(tǒng)。

2016-05-10 11:47:13 14

14 基于FPGA的多通道圖像采集存儲(chǔ)系統(tǒng)設(shè)計(jì)

2016-08-30 15:10:14 11

11 基于USB20和FPGA的圖像采集、存儲(chǔ)系統(tǒng)研究,感興趣的可以看看。

2016-09-22 14:08:55 32

32 基于FPGA控制的高速圖像實(shí)時(shí)存儲(chǔ),下來(lái)看看

2016-09-22 12:26:33 15

15 基于FPGA的可堆疊存儲(chǔ)陣列設(shè)計(jì)與優(yōu)化

2017-01-07 21:28:58 0

0 基于FPGA的數(shù)字存儲(chǔ)示波器的顯示技術(shù)

2017-01-18 20:35:09 36

36 基于LabVIEW與FPGA的飛行訓(xùn)練彈測(cè)試系統(tǒng)設(shè)計(jì)_劉克軒

2017-02-07 18:22:06 6

6 基于FPGA和無(wú)線通信的密立根油滴測(cè)試系統(tǒng)設(shè)計(jì)_徐富新

2017-03-19 19:08:35 0

0 性能。考慮到測(cè)試空間、預(yù)算等因素,廠商也希望能夠用一個(gè)集成的并且高度可靠的測(cè)試系統(tǒng)替代這些不同的分立測(cè)試設(shè)備,以期根據(jù)具體應(yīng)用定義功能,同時(shí)又能滿足測(cè)試環(huán)境和技術(shù)指標(biāo)的要求。 現(xiàn)場(chǎng)可編程門(mén)陣列FPGA(Field Prog

2017-09-05 14:38:31 1

1 采用DMA傳輸技術(shù)將存儲(chǔ)后的圖像數(shù)據(jù)上傳至計(jì)算機(jī)硬盤(pán)中作進(jìn)一步處理;同時(shí),利用SDRAM顯存實(shí)時(shí)刷新數(shù)據(jù),FPGA構(gòu)造相應(yīng)的VGA信號(hào),最終實(shí)現(xiàn)100 MB/s圖像數(shù)據(jù)的實(shí)時(shí)顯示。 隨著數(shù)據(jù)存儲(chǔ)設(shè)備被廣泛應(yīng)用于航空航天系統(tǒng)、醫(yī)療衛(wèi)生、工業(yè)自動(dòng)化等各行各業(yè),對(duì)于圖像設(shè)備采集的控制及實(shí)

2017-10-11 18:33:17 6

6 (FPGA)作為數(shù)字存儲(chǔ)示波器采樣控制系統(tǒng)的核心,從芯片間有效協(xié)助的角度,基于FPGA 設(shè)計(jì)ARM 接[ ]通信控制模塊和外圍芯片驅(qū)動(dòng)功能模塊,以FPGA 為核心有效地組織其它芯片,共同完成數(shù)字存儲(chǔ)示波器數(shù)據(jù)采樣過(guò)程,確保數(shù)據(jù)按需

2017-10-18 15:15:52 55

55 在空間受限、環(huán)境惡劣和無(wú)法實(shí)時(shí)傳輸數(shù)據(jù)的情況下,傳統(tǒng)測(cè)試技術(shù)受到很大限制,必須使用存儲(chǔ)測(cè)試方法。該方法是在不影響被測(cè)對(duì)象或影響在允許范圍內(nèi)的情況下,將微型存儲(chǔ)測(cè)試系統(tǒng)置入被測(cè)體內(nèi),現(xiàn)場(chǎng)實(shí)時(shí)完成信息

2017-10-26 15:00:03 1

1 利用雙環(huán)境模擬系統(tǒng)對(duì)熱電池進(jìn)行動(dòng)態(tài)模擬測(cè)試時(shí)存在兩個(gè)技術(shù)難點(diǎn):一是由于熱電池體積小、質(zhì)量輕,測(cè)試系統(tǒng)是與熱電池一同置于彈丸內(nèi),體積受到限制;二是由于測(cè)試的數(shù)據(jù)量較大,系統(tǒng)要有足夠的存儲(chǔ)空間,而且

2017-10-30 13:05:27 3

3 部分組成。對(duì)FPGA進(jìn)行測(cè)試要對(duì)FPGA內(nèi)部可能包含的資源進(jìn)行結(jié)構(gòu)分析,經(jīng)過(guò)一個(gè)測(cè)試配置(TC)和向量實(shí)施(TS)的過(guò)程,把FPGA配置為具有特定功能的電路,再?gòu)膽?yīng)用級(jí)別上對(duì)電路進(jìn)行測(cè)試,完成電路的功能及參數(shù)測(cè)試。 2 FPGA的配置方法 對(duì)FPGA進(jìn)行配置有多種方法可以選擇,包括邊界掃描配置方法等。

2017-11-18 10:44:37 3307

3307

設(shè)計(jì)、給出了用雙RAM訪問(wèn)CF卡的編程,并且利用FPGA作為FIFO對(duì)AD采集的數(shù)據(jù)進(jìn)行緩沖,然后存儲(chǔ)到大容量的CF卡中。

2017-11-23 15:01:03 15316

15316 從制造的角度來(lái)講,FPGA測(cè)試是指對(duì)FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測(cè)。完整的FPGA測(cè)試包括兩步,一是配置FPGA、然后是測(cè)試FPGA,配置FPGA是指將FPGA通過(guò)將

2017-11-24 20:55:53 8774

8774

摘要: 基于對(duì)FPGA系統(tǒng)失效機(jī)理的深入分析,提出了軟件測(cè)試技術(shù)在FPGA測(cè)試中的應(yīng)用,并分析了其可行性;通過(guò)對(duì)比FPGA與軟件系統(tǒng)的異同,歸納出FPGA特有的測(cè)試要求,從而在軟件測(cè)試技術(shù)的基礎(chǔ)上

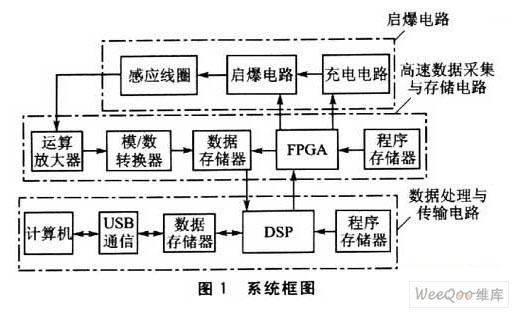

2018-01-19 22:34:59 3023

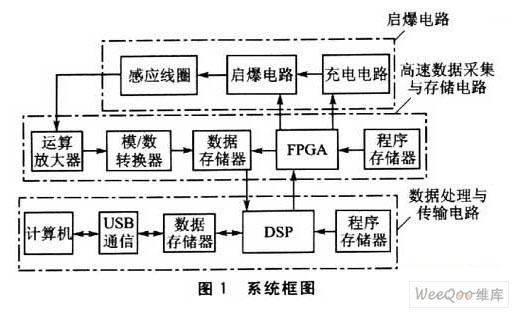

3023 整個(gè)系統(tǒng)的組成如圖1所示。當(dāng)啟爆電路在DSP和FPGA的控制下啟爆時(shí),感應(yīng)線圈取出啟爆電流,首先是高速數(shù)據(jù)采集與存儲(chǔ)電路,以FPGA為核心,對(duì)數(shù)據(jù)進(jìn)行高速采集與存儲(chǔ)。數(shù)據(jù)存儲(chǔ)完畢,FPGA發(fā)信號(hào)告知DSP采集完畢,開(kāi)始對(duì)采集的數(shù)據(jù)進(jìn)行相關(guān)的處理。

2018-10-07 12:03:03 3814

3814

FPGA可以通過(guò)專(zhuān)享的硬件資源進(jìn)行處理數(shù)據(jù),從而實(shí)現(xiàn)較高的吞吐率,可以比通過(guò)I/O硬件先獲取數(shù)據(jù)再通過(guò)軟件執(zhí)行數(shù)據(jù)處理的速率更快。結(jié)合FPGA技術(shù)的測(cè)試系統(tǒng),不是按照傳統(tǒng)意義上的“采集、數(shù)據(jù)傳輸

2018-10-07 11:47:47 5640

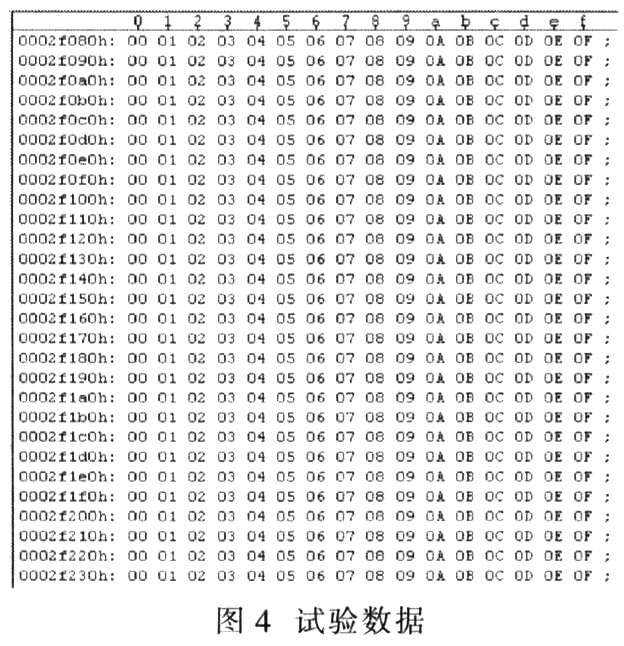

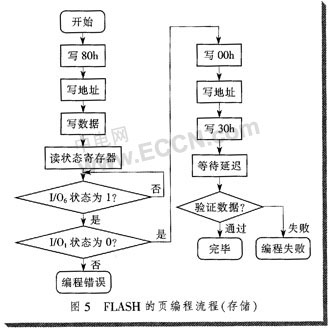

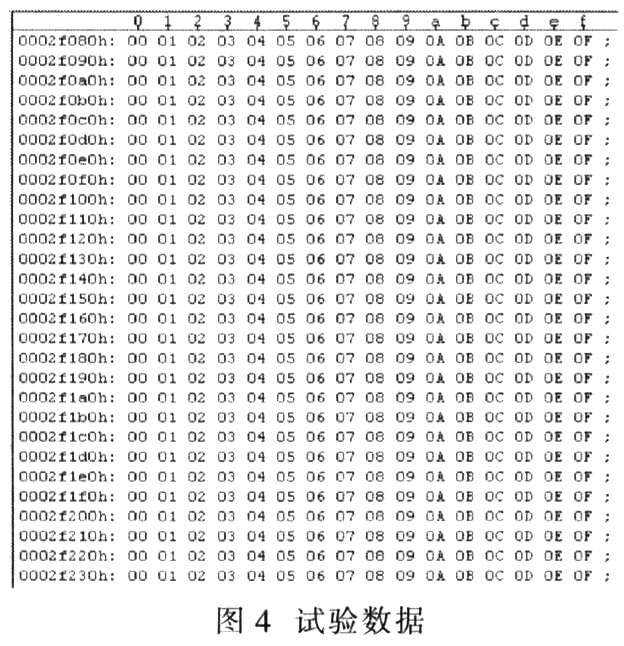

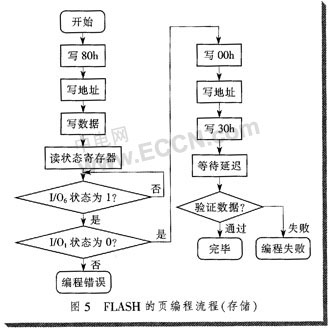

5640 詳細(xì)介紹基于FPGA的微型數(shù)字存儲(chǔ)系統(tǒng)的設(shè)計(jì).該系統(tǒng)利用FPGA對(duì)Flash存儲(chǔ)器進(jìn)行讀、寫(xiě)、擦除等操作,并將寫(xiě)入的數(shù)據(jù)通過(guò)計(jì)算杌US8接口讀入上住機(jī).以此實(shí)現(xiàn)數(shù)據(jù)讀出、顯示等功能。該系統(tǒng)

2018-09-07 17:14:47 9

9 FPGA的邏輯是通過(guò)向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來(lái)實(shí)現(xiàn)的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能,FPGA允許無(wú)限次的編程。

2019-11-12 07:09:00 1993

1993 基于FPGA的PCB測(cè)試機(jī)的硬件控制系統(tǒng),提高了PCB測(cè)試機(jī)的測(cè)試速度、簡(jiǎn)化電路的設(shè)計(jì)。

2020-04-01 17:56:56 2884

2884 基于FPGA的PCB測(cè)試機(jī)的硬件控制系統(tǒng),提高了PCB測(cè)試機(jī)的測(cè)試速度、簡(jiǎn)化電路的設(shè)計(jì)。

2019-10-23 15:15:45 2901

2901 在基站的模擬測(cè)試系統(tǒng)中,終端控制子系統(tǒng)負(fù)責(zé)生成上行測(cè)試數(shù)據(jù)并將其發(fā)送到被測(cè)基帶板,測(cè)試基帶板上行接收的功能及性能;同時(shí)根據(jù)后臺(tái)控制采集下行發(fā)射的基帶數(shù)據(jù)并送后臺(tái)進(jìn)行分析,測(cè)試其發(fā)射功能。而FPGA部分屬于終端控制子系統(tǒng)的前臺(tái)部分,負(fù)責(zé)IQ數(shù)據(jù)的發(fā)送及采集,基帶測(cè)試板的功能主要在這里面實(shí)現(xiàn)。

2020-08-07 17:53:52 1482

1482

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之FPGA的RAM存儲(chǔ)課件和工程文件。

2020-12-10 15:27:00 31

31 在高速圖像采集中.需要對(duì)采集的大量數(shù)據(jù)進(jìn)行實(shí)時(shí)存儲(chǔ)。介紹了一種基于FPGA控制的高速圖像實(shí)時(shí)存儲(chǔ)系統(tǒng),該系統(tǒng)能在脫機(jī)方式下由FPGA直接控制IDE硬盤(pán),實(shí)現(xiàn)高速圖像的實(shí)時(shí)存儲(chǔ),并通過(guò)PCI接口對(duì)硬盤(pán)進(jìn)行事后訪問(wèn)。目前,采用單硬盤(pán)時(shí)的記錄速度可達(dá)到24 MB/s。

2021-01-22 14:29:00 9

9 針對(duì)圖像信號(hào)的基本特征設(shè)計(jì)了對(duì)于四路間歇性數(shù)據(jù)并行存儲(chǔ)方案,整個(gè)圖像采集存儲(chǔ)系統(tǒng)分為控制模塊和存儲(chǔ)模塊兩個(gè)部分:控制模塊主要是采用FPGA對(duì)圖像數(shù)據(jù)進(jìn)行并行接收、數(shù)據(jù)編碼、控制存儲(chǔ)、全程工作控制

2021-01-29 15:27:00 6

6 基于FPGA的高速大容量FLASH存儲(chǔ)(單片機(jī)底層嵌入式開(kāi)發(fā))-該文檔為基于FPGA的高速大容量FLASH存儲(chǔ)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 16:46:45 13

13 視頻圖形顯示系統(tǒng)理想的架構(gòu)選擇。視頻處理和圖形生成需要存儲(chǔ)海量數(shù)據(jù),FPGA內(nèi)部的存儲(chǔ)資源無(wú)法滿足存儲(chǔ)需求,因此需要配置外部存儲(chǔ)器。 ??? 與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 2788

2788 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。 嵌入式邏輯分析工具無(wú)法滿足通用性要求,外部測(cè)試工具可以把FPGA內(nèi)部信號(hào)與實(shí)際電路聯(lián)合起來(lái)觀察系統(tǒng)真實(shí)運(yùn)行情況。 隨著

2023-10-23 15:20:01 1956

1956

FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)是一種高度靈活的硬件設(shè)備,可以根據(jù)特定的需求進(jìn)行重新配置。FPGA通常用于處理大量數(shù)據(jù)和實(shí)時(shí)計(jì)算。然而,FPGA通常并沒(méi)有內(nèi)置大容量的數(shù)據(jù)存儲(chǔ)器,例如硬盤(pán)或固態(tài)硬盤(pán)。這就

2023-12-15 15:42:51 4664

4664

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論