電子發燒友網報道(文/吳子鵬)在AI技術向千行百業加速滲透、算力需求呈現多元化與碎片化特征的當下,領域專用架構(DSA)已成為突破通用計算瓶頸的關鍵路徑。然而,高門檻、長周期等痛點,嚴重制約了DSA的規模化落地。在此背景下,隼瞻科技聯合創始人兼CTO姚彥斌在RISC-V×AI生態大會暨ArchitStudio用戶大會上發表《全面解碼ArchitStudio:基于DSA方法論的行業革新》主題演講,系統性拆解核心技術體系,為行業揭示了一套“全流程自動化”的處理器設計革新方案,正推動整個行業的設計模式實現根本性轉變。

?

?

這些優勢讓我們正迎來DSA發展的黃金時代。

?

不過,設計人員也必須認識到當前DSA落地面臨的難題。姚彥斌以端側AI應用為例具體剖析了這些挑戰,包括:

- 端側AI應用場景豐富多樣:語音識別、圖像識別、視頻分析、自然語言處理等場景碎片化,需求呈現多元化特征;

- AI模型種類繁多且持續演進:CNN、RNN、Transformer、輕量化模型等新模型層出不窮,架構復雜度不斷提升;

- 新數據類型和算子不斷涌現:低比特整型、FP8等對硬件的可編程性和擴展性提出了更高要求;- 硬件資源受限是核心挑戰:存在功耗限制、面積約束,且對實時性要求較高。

?

對此,他總結道:“AI應用的多樣性以及對算力需求的持續增長,與端側芯片在功耗、面積上的約束形成永恒矛盾;同時,處理器瀑布式的長周期開發模式與DSA的敏捷快速迭代需求相悖,這是限制DSA處理器落地的根本障礙。”

?

為幫助行業破解這些難題,隼瞻科技推出了自研產品——DSA處理器敏捷開發平臺ArchitStudio。該平臺實現了需求“左移”和方案“右移”,為DSA處理器設計提供了一種敏捷開發方法。

?

?

?

該平臺的第一大優勢是界面友好,可為設計人員提供流暢的交互流程與豐富的可視化操作,支持“樂高”式積木搭建專用處理器;第二大優勢是語言專業,采用與程序員廣泛使用的C語言近似的語法,兼具高層抽象與微架構細節表達能力,可靈活支撐AI、通信、工業控制等各類領域專用處理器的按需構建;第三大優勢是極致效率,能夠實現分鐘級生成完整交付包,提供PPA(性能、功耗、面積)預估與瓶頸分析,助力架構級敏捷迭代,同時支持MHz級時序精準仿真,加速驗證迭代優化;第四大優勢是全棧閉環,實現了“定義即交付”,打通了從架構創新到硬件落地的最后一公里。

?

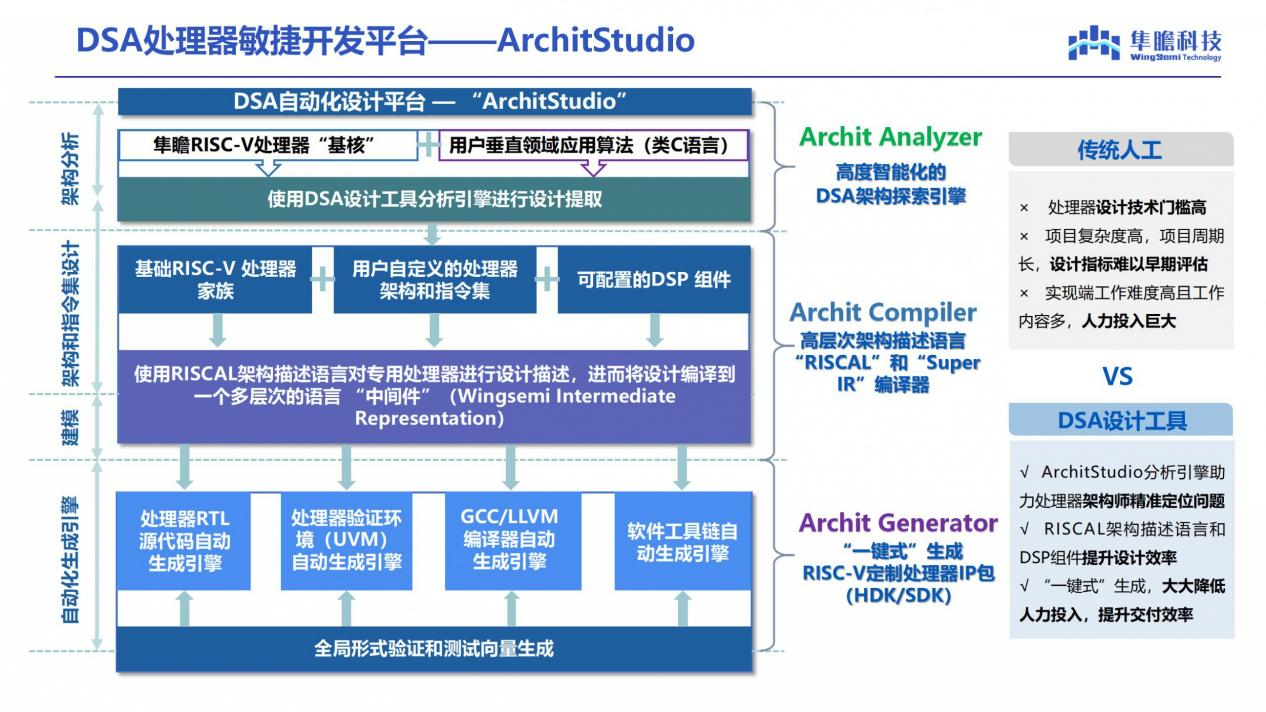

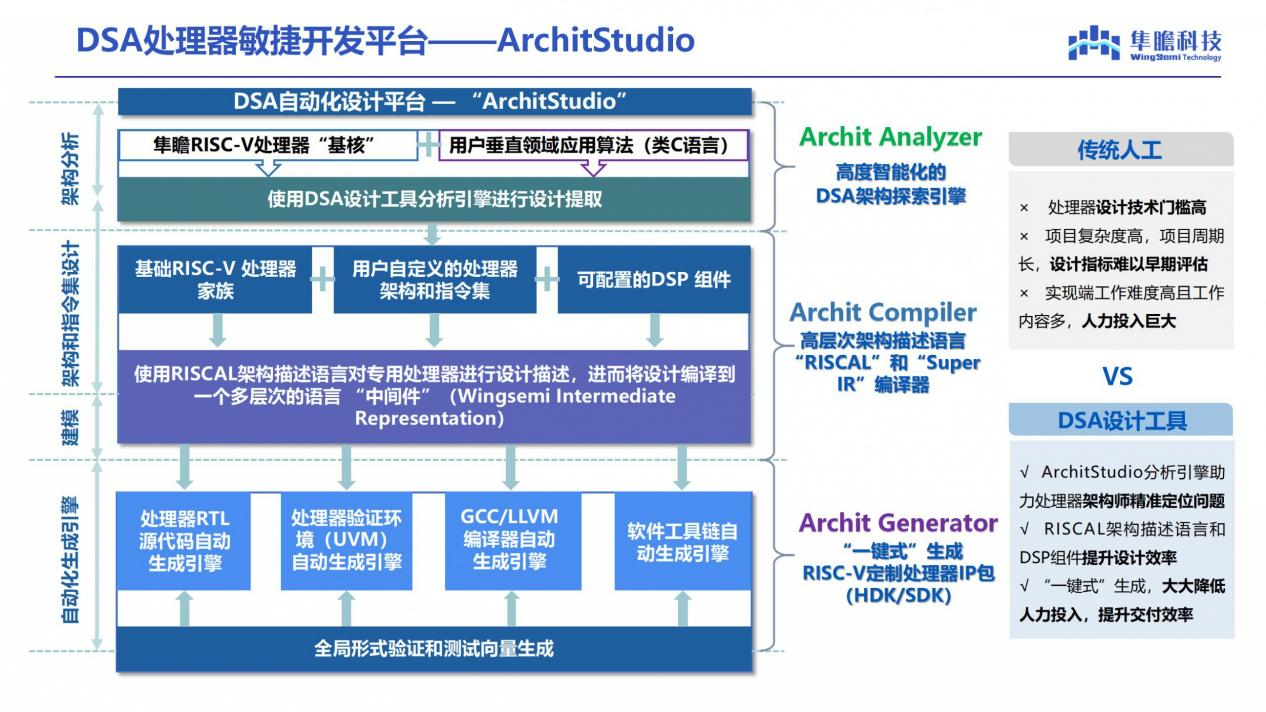

完整的ArchitStudio包含四大核心組件:高度智能化的DSA架構探索引擎Archit Analyzer、高度自由化的設計器Archit Designer及統一的語言編譯基礎設施Archit Compiler、“一鍵式”生成RISC-V定制處理器IP包(HDK/SDK)的Archit Generator。

?

其中,Archit Analyzer配備豐富的分析引擎,從架構、微架構以及程序代碼三個維度提供宏觀到微觀的DSA設計指導,助力處理器架構師精準定位設計瓶頸與性能問題,優化決策。該引擎提供處理器匯編指令的運行信息,包括指令統計餅狀圖、指令細粒度分析、運行周期數等,設計人員可依據Profiling結果判斷處理器運行效率,借助多層次性能分析輸出輔助業務優化。

?

此外,Archit Analyzer可協助設計人員完成Pipeline Stall(流水線阻塞)分析,輔助算法優化——通過剖析流水線阻塞點和指令覆蓋率,制定軟硬件協同定制指令優化方案,顯著提升特定算法的執行效率。同時,設計人員可借助該引擎結合算法行為特征與目標工藝庫,構建從指令級、模塊級到系統級的全層級功耗預測模型,精準定位功耗熱點,將能效比優化15%-30%。

?

Archit Designer則是提供Core Editor與RISCAL Editor兩種設計入口。用戶可以像搭建樂高積木一樣,通過拖拽配置處理器核、擴展協處理器、定義自定義指令,所見即所得。平臺同時集成了出色的C/C++ IDE,支持軟硬件協同開發與調試。

?

Archit Compiler采用隼瞻自研的高級架構描述語言“RISCAL”及對應的編譯框架,能讓設計人員高效、精確地描述專用處理器的架構意圖,并將其編譯為統一的中間表示(Wingsemi Intermediate Representation),為后續自動化流程奠定堅實基礎。該編譯器構建了覆蓋處理器微架構參數(流水線深度、緩存容量、分支預測策略等)的高維設計空間,利用深度強化學習(DRL)算法探索性能(DMIPS/MHz)、面積(mm2)、功耗(mW)的PPA最優解,開發效率較傳統模式大幅提升。借助該編譯器,設計人員可實現“所見即所得”的代碼及組件生成,將繁瑣的底層代碼設計編寫轉化為“樂高”式模塊搭建。

?

Archit Generator能幫助設計人員“一鍵式”生成完整的、可直接投入使用的RISC-V定制處理器IP包(包含HDK硬件開發包和SDK軟件開發包)。其自動化生成引擎將傳統需要數月甚至數年的繁重手工編碼與集成工作縮短至數周,大幅降低人力投入,顯著提升項目交付效率與確定性。

?

在ArchitStudio平臺中,除各類工具和編譯器外,高級處理器架構描述語言RISCAL同樣占據重要地位。RISCAL的名稱包含“Retargetable”“RISC”和“CAL”三大核心內涵:

?

- “Retargetable”(可重定向):秉持可重定向的設計哲學,能夠基于用戶需求快速迭代生成定制化指令集,精準匹配細分場景的計算需求;

- “RISC”(精簡指令集):以開放、開源的RISC-V架構為根基,賦能領域特定指令集的敏捷定義與高效實現,讓DSA設計回歸開放與簡潔的本質;

- “CAL”(語言驅動):實現語言驅動的編譯器與硬件RTL同源共生,從指令定義到工具鏈生成無縫一致,徹底消除架構與實現之間的語義鴻溝。

?

因此,姚彥斌認為,當前端側AI規模化落地面臨算力適配不精準、開發效率偏低、成本控制難度大三大核心挑戰,而RISC-V架構的開源靈活特性與ArchitStudio平臺的自動化開發能力形成完美互補,構建起“架構+工具”的雙輪驅動模式,為破解端側AI落地難題提供了有效路徑。

?

隼瞻科技聯合創始人兼CTO姚彥斌,圖源:隼瞻科技

?DSA的黃金時代和落地痛點

姚彥斌以《A New Golden Age for Computer Architecture》論文為引展開了話題,這篇論文闡述了DSA的發展潛能及給行業帶來的機遇。論文認為,DSA是一種為特定領域可編程且通常是圖靈完整的架構,專門針對特定應用程序類別進行定制。從這個意義上說,DSA與專用集成電路(ASIC)存在差異:后者通常用于單一功能,代碼極少變更;而DSA可實現更優性能,核心原因在于其更貼近應用程序需求——既能構建針對特定應用的并行程序,又能更高效地利用內存層級架構。DSA的典型例子包括圖形處理單元(GPU)、用于深度學習的張量處理器(TPU)以及用于通信領域的數字信號處理器(DSP)。?

這些優勢讓我們正迎來DSA發展的黃金時代。

?

不過,設計人員也必須認識到當前DSA落地面臨的難題。姚彥斌以端側AI應用為例具體剖析了這些挑戰,包括:

- 端側AI應用場景豐富多樣:語音識別、圖像識別、視頻分析、自然語言處理等場景碎片化,需求呈現多元化特征;

- AI模型種類繁多且持續演進:CNN、RNN、Transformer、輕量化模型等新模型層出不窮,架構復雜度不斷提升;

- 新數據類型和算子不斷涌現:低比特整型、FP8等對硬件的可編程性和擴展性提出了更高要求;- 硬件資源受限是核心挑戰:存在功耗限制、面積約束,且對實時性要求較高。

?

對此,他總結道:“AI應用的多樣性以及對算力需求的持續增長,與端側芯片在功耗、面積上的約束形成永恒矛盾;同時,處理器瀑布式的長周期開發模式與DSA的敏捷快速迭代需求相悖,這是限制DSA處理器落地的根本障礙。”

?

為幫助行業破解這些難題,隼瞻科技推出了自研產品——DSA處理器敏捷開發平臺ArchitStudio。該平臺實現了需求“左移”和方案“右移”,為DSA處理器設計提供了一種敏捷開發方法。

?

?

ArchitStudio:DSA處理器的“一站式”智能設計工廠

ArchitStudio是隼瞻科技在第五屆RISC-V中國峰會發布的重磅產品,也是該公司“2+N”平臺戰略的重要一環。其核心使命是將復雜、冗長且充滿不確定性的DSA處理器設計流程,轉化為高度自動化、智能化的敏捷開發體驗,集成了隼瞻科技在處理器架構、自動化工具鏈領域的深厚積累。?

隼瞻科技“2+N”平臺戰略,電子發燒友網記者拍攝

?該平臺的第一大優勢是界面友好,可為設計人員提供流暢的交互流程與豐富的可視化操作,支持“樂高”式積木搭建專用處理器;第二大優勢是語言專業,采用與程序員廣泛使用的C語言近似的語法,兼具高層抽象與微架構細節表達能力,可靈活支撐AI、通信、工業控制等各類領域專用處理器的按需構建;第三大優勢是極致效率,能夠實現分鐘級生成完整交付包,提供PPA(性能、功耗、面積)預估與瓶頸分析,助力架構級敏捷迭代,同時支持MHz級時序精準仿真,加速驗證迭代優化;第四大優勢是全棧閉環,實現了“定義即交付”,打通了從架構創新到硬件落地的最后一公里。

?

完整的ArchitStudio包含四大核心組件:高度智能化的DSA架構探索引擎Archit Analyzer、高度自由化的設計器Archit Designer及統一的語言編譯基礎設施Archit Compiler、“一鍵式”生成RISC-V定制處理器IP包(HDK/SDK)的Archit Generator。

?

ArchitStudio平臺,圖源:隼瞻科技

?其中,Archit Analyzer配備豐富的分析引擎,從架構、微架構以及程序代碼三個維度提供宏觀到微觀的DSA設計指導,助力處理器架構師精準定位設計瓶頸與性能問題,優化決策。該引擎提供處理器匯編指令的運行信息,包括指令統計餅狀圖、指令細粒度分析、運行周期數等,設計人員可依據Profiling結果判斷處理器運行效率,借助多層次性能分析輸出輔助業務優化。

?

此外,Archit Analyzer可協助設計人員完成Pipeline Stall(流水線阻塞)分析,輔助算法優化——通過剖析流水線阻塞點和指令覆蓋率,制定軟硬件協同定制指令優化方案,顯著提升特定算法的執行效率。同時,設計人員可借助該引擎結合算法行為特征與目標工藝庫,構建從指令級、模塊級到系統級的全層級功耗預測模型,精準定位功耗熱點,將能效比優化15%-30%。

?

Archit Designer則是提供Core Editor與RISCAL Editor兩種設計入口。用戶可以像搭建樂高積木一樣,通過拖拽配置處理器核、擴展協處理器、定義自定義指令,所見即所得。平臺同時集成了出色的C/C++ IDE,支持軟硬件協同開發與調試。

?

Archit Compiler采用隼瞻自研的高級架構描述語言“RISCAL”及對應的編譯框架,能讓設計人員高效、精確地描述專用處理器的架構意圖,并將其編譯為統一的中間表示(Wingsemi Intermediate Representation),為后續自動化流程奠定堅實基礎。該編譯器構建了覆蓋處理器微架構參數(流水線深度、緩存容量、分支預測策略等)的高維設計空間,利用深度強化學習(DRL)算法探索性能(DMIPS/MHz)、面積(mm2)、功耗(mW)的PPA最優解,開發效率較傳統模式大幅提升。借助該編譯器,設計人員可實現“所見即所得”的代碼及組件生成,將繁瑣的底層代碼設計編寫轉化為“樂高”式模塊搭建。

?

Archit Generator能幫助設計人員“一鍵式”生成完整的、可直接投入使用的RISC-V定制處理器IP包(包含HDK硬件開發包和SDK軟件開發包)。其自動化生成引擎將傳統需要數月甚至數年的繁重手工編碼與集成工作縮短至數周,大幅降低人力投入,顯著提升項目交付效率與確定性。

?

在ArchitStudio平臺中,除各類工具和編譯器外,高級處理器架構描述語言RISCAL同樣占據重要地位。RISCAL的名稱包含“Retargetable”“RISC”和“CAL”三大核心內涵:

?

- “Retargetable”(可重定向):秉持可重定向的設計哲學,能夠基于用戶需求快速迭代生成定制化指令集,精準匹配細分場景的計算需求;

- “RISC”(精簡指令集):以開放、開源的RISC-V架構為根基,賦能領域特定指令集的敏捷定義與高效實現,讓DSA設計回歸開放與簡潔的本質;

- “CAL”(語言驅動):實現語言驅動的編譯器與硬件RTL同源共生,從指令定義到工具鏈生成無縫一致,徹底消除架構與實現之間的語義鴻溝。

?

因此,姚彥斌認為,當前端側AI規模化落地面臨算力適配不精準、開發效率偏低、成本控制難度大三大核心挑戰,而RISC-V架構的開源靈活特性與ArchitStudio平臺的自動化開發能力形成完美互補,構建起“架構+工具”的雙輪驅動模式,為破解端側AI落地難題提供了有效路徑。

電子發燒友App

電子發燒友App

評論