使用RISC-V進(jìn)行高效數(shù)據(jù)處理的方法涉及多個(gè)方面,包括處理器內(nèi)核與DSA(領(lǐng)域特定加速器)之間的通信優(yōu)化、內(nèi)存管理優(yōu)化、多線程性能提升等。以下是一些具體的方法:

一、處理器內(nèi)核與DSA之間的通信優(yōu)化

- DSA緩存 :

- RISC-V為優(yōu)化處理器內(nèi)核和DSA之間的細(xì)粒度通信提供了一個(gè)獨(dú)特的方法。例如,DSA可以導(dǎo)出到位于每個(gè)RISC-V內(nèi)核旁邊的DSA緩存。

- 內(nèi)核可以從DSA緩存中輪詢狀態(tài)的變化,從而將內(nèi)核與DSA之間的交互延遲減少到數(shù)十個(gè)周期。

- DSA緩存可以通過從DSA中預(yù)取數(shù)據(jù)并將較小的IO空間中合并寫入成較大的區(qū)塊,從而進(jìn)一步提高內(nèi)核與DSA的交互性能。

- 流水線方式實(shí)現(xiàn)IO負(fù)載 :

- RISC-V的實(shí)現(xiàn)機(jī)制通常是在內(nèi)核與DSA之間互連的作用下以流水線方式實(shí)現(xiàn)此類IO負(fù)載。

- 如果網(wǎng)狀拓?fù)涫褂脧膬?nèi)核到DSA(可能通過IO橋接器)的固定路徑(例如X-Y路徑),則互連可以保證其排序并且允許對DSA內(nèi)存進(jìn)行非常高的帶寬訪問。

- IO排序模式 :

- RISC-V架構(gòu)本身提供了另外兩種可選IO排序模式,包括保守的IO排序模式和高帶寬的自由定序模式。

- 保守的IO排序模式可以有選擇地使用它來保證必要時(shí)達(dá)到的強(qiáng)制排序狀態(tài)。

- 高帶寬的自由定序模式允許IO加載和存儲(chǔ)在該模式下進(jìn)行重新排序。

二、內(nèi)存管理優(yōu)化

- 繞過最后一級緩存 :

- 基于RISC-V的SoC可以使用繞過最后一級緩存的方法,直接將數(shù)據(jù)寫入內(nèi)存中。

- 這可以通過將要寫入的數(shù)據(jù)標(biāo)記為未緩存來實(shí)現(xiàn),或者DMA引擎可以向最后一級緩存提供一個(gè)提示,不分配最后一級緩存中的數(shù)據(jù),而是直接寫入內(nèi)存。

- 高性能內(nèi)存和存儲(chǔ)技術(shù) :

三、多線程性能提升

- 高效的線程調(diào)度算法 :

- RISC-V架構(gòu)支持多種線程調(diào)度算法,如CFS(完全公平調(diào)度器)等。

- 選擇合適的線程調(diào)度算法可以提高多線程應(yīng)用程序的響應(yīng)速度和整體性能。

- 硬件支持 :

- RISC-V架構(gòu)支持一些硬件特性,如硬件線程調(diào)度、原子操作等。

- 這些特性可以簡化多線程程序的設(shè)計(jì),并提高性能。

- 并行計(jì)算 :

- 利用RISC-V架構(gòu)提供的并行計(jì)算資源,如SIMD(單指令多數(shù)據(jù))指令集、向量處理單元等。

- 通過將計(jì)算任務(wù)分解為多個(gè)并行子任務(wù),并利用硬件資源同時(shí)執(zhí)行這些子任務(wù),可以實(shí)現(xiàn)更高的計(jì)算吞吐量和更低的延遲。

- 代碼優(yōu)化 :

- 針對特定的多線程應(yīng)用程序,可以通過代碼優(yōu)化來提高性能。

- 例如,減少鎖的使用、避免不必要的數(shù)據(jù)拷貝、使用更高效的算法和數(shù)據(jù)結(jié)構(gòu)等。

- 調(diào)優(yōu)編譯器 :

- 編譯器是連接應(yīng)用程序和硬件的橋梁,其優(yōu)化程度直接影響程序的性能。

- 可以通過調(diào)整編譯器的選項(xiàng)來優(yōu)化生成的代碼,例如使用更激進(jìn)的優(yōu)化選項(xiàng)、啟用并行化編譯等。

四、其他優(yōu)化方法

- 精簡指令集 :

- RISC-V精簡了指令集,以提高運(yùn)行效率和降低設(shè)計(jì)復(fù)雜度。

- 可擴(kuò)展性 :

- RISC-V可以根據(jù)需要進(jìn)行擴(kuò)展,從而適應(yīng)不同的應(yīng)用場景和性能需求。

- 兼容性 :

- RISC-V提供多個(gè)標(biāo)準(zhǔn)擴(kuò)展,包括浮點(diǎn)、向量、加密等,以滿足不同的處理器需求。

綜上所述,使用RISC-V進(jìn)行高效數(shù)據(jù)處理需要從多個(gè)方面進(jìn)行綜合考慮和優(yōu)化。通過優(yōu)化處理器內(nèi)核與DSA之間的通信、內(nèi)存管理、多線程性能以及其他方面的優(yōu)化方法,可以顯著提高RISC-V處理器的數(shù)據(jù)處理效率。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

通信

+關(guān)注

關(guān)注

18文章

6391瀏覽量

140038 -

多線程

+關(guān)注

關(guān)注

0文章

279瀏覽量

21027 -

數(shù)據(jù)處理

+關(guān)注

關(guān)注

0文章

648瀏覽量

29985 -

RISC-V

+關(guān)注

關(guān)注

48文章

2886瀏覽量

52990

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

新思科技VC Formal解決方案在RISC-V驗(yàn)證中的應(yīng)用

——地球上人均 6 顆。從“RISC-V 將無處不在”到“RISC-V,就現(xiàn)在”,RISC-V 已幾乎覆蓋所有應(yīng)用。當(dāng)前,RISC-V 已成功躋身世界主流

新思科技ARC-V處理器驅(qū)動(dòng)RISC-V市場無限機(jī)遇

從 2010 年美國加州大學(xué)伯克利分校的教授與他的研究生團(tuán)隊(duì)耗時(shí)三個(gè)月完成 RISC-V 指令集的開發(fā)工作,到 2015 年,RISC-V 在學(xué)術(shù)界聲名鵲起,再到 2025 年成為主流架構(gòu)之一

探索RISC-V在機(jī)器人領(lǐng)域的潛力

的硬件配置給人留下了深刻的第一印象:

? 核心處理器: 搭載了進(jìn)迭時(shí)空的K1系列高性能RISC-V處理器,具備強(qiáng)大的通用計(jì)算能力和AI加速特性。

? 內(nèi)存與存儲(chǔ): 板載LPDDR4內(nèi)存和eMMC

發(fā)表于 12-03 14:40

為什么RISC-V是嵌入式應(yīng)用的最佳選擇

最近RISC-V基金會(huì)在社交媒體上發(fā)文,文章說物聯(lián)網(wǎng)和嵌入式系統(tǒng)正在迅速發(fā)展,需要更高的計(jì)算性能、更低的功耗和人工智能。RISC-V是為未來而建的,包括超高效的MCU到高性能應(yīng)用處理器

基于E203 RISC-V的音頻信號處理系統(tǒng) -協(xié)處理器的乘累加過程

協(xié)處理器簡介

RISC-V具有很高的可擴(kuò)展性,既預(yù)留出了指令編碼空間,也提供了預(yù)定義的Custom指令;RISC-V的標(biāo)準(zhǔn)指令集僅使用了少部分指令編碼空間,更多的指令編碼空間被預(yù)留給用戶進(jìn)行

發(fā)表于 10-28 06:18

risc-v P擴(kuò)展(一) P指令集簡介

解碼、醫(yī)學(xué)成像、計(jì)算機(jī)視覺、嵌入式控制、機(jī)器人技術(shù)、人機(jī)界面等。

P指令集擴(kuò)展提高了RISC-V CPU IP產(chǎn)品的DSP算法處理能力。隨著RISC-V P指令集擴(kuò)展的增加,RISC-

發(fā)表于 10-23 07:40

提高RISC-V在Drystone測試中得分的方法

:編譯器如何優(yōu)化生成的機(jī)器代碼也會(huì)影響Drystone的得分。優(yōu)化的編譯器能夠生成更高效的機(jī)器代碼,從而提高性能。

提高 RISC-V 在 Drystone 測試中得分的方法主要有:

優(yōu)化處

發(fā)表于 10-21 13:58

RISC-V B擴(kuò)展介紹及實(shí)現(xiàn)

,可以被任何支持RISC-V ISR的處理器解釋執(zhí)行。

需要注意,B擴(kuò)展是與基本RV32I/RV64I RISC-V指令集完全兼容的。因此,使用支持B擴(kuò)展的芯片可以同時(shí)享受到原始架構(gòu)指令集以及B擴(kuò)展的優(yōu)勢

發(fā)表于 10-21 13:01

國產(chǎn)!全志T113-i 雙核Cortex-A7@1.2GHz 工業(yè)開發(fā)板—RISC-V案例開發(fā)手冊(上)

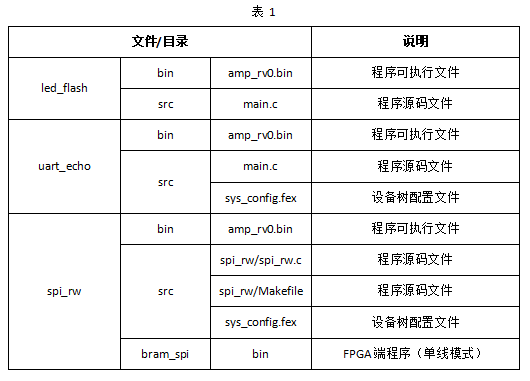

本文檔主要介紹T113-i處理器的RISC-V案例開發(fā),演示RISC-V核心RTOS案例的編譯與加載方法。適用開發(fā)環(huán)境如下。

2025新思科技RISC-V科技日活動(dòng)圓滿結(jié)束

新思科技深度參與2025 RISC-V中國峰會(huì)并于2025年7月16日舉辦同期活動(dòng)“新思科技RISC-V科技日”技術(shù)論壇,聚焦“從芯片到系統(tǒng)重構(gòu)RISC-V創(chuàng)新”主題,議題覆蓋當(dāng)前最前沿的技術(shù)領(lǐng)域

RISC-V International CEO:RISC-V 應(yīng)用全面開花,2031 年滲透率將達(dá) 25.7%

and RISC-V Adoption in 2025》。 ? 當(dāng)前,RISC-V 的成功已從嵌入式計(jì)算領(lǐng)域加速向存儲(chǔ)技術(shù)與高性能計(jì)算(HPC)領(lǐng)域滲透,展現(xiàn)出跨行業(yè)的顛覆性潛力。Andrea Gallo 分享了 The SHD Group 2024 年 10 月的

發(fā)表于 07-17 10:28

?3698次閱讀

沁恒微電子:從互連互通應(yīng)用推動(dòng)RISC-V落地發(fā)展

沁恒微電子邀您共襄盛舉沁恒微電子專注于連接技術(shù)和微處理器內(nèi)核研究,基于多層次青稞RISC-V微處理器、多類型物理層收發(fā)器構(gòu)建USB/藍(lán)牙/以太網(wǎng)接口芯片和青稞RISC-V系列MCU/S

RISC-V和ARM有何區(qū)別?

在微處理器架構(gòu)領(lǐng)域,ARM與RISC-V是兩個(gè)備受關(guān)注的體系。ZLG致遠(yuǎn)電子在推出ARM核心版后,又推出了基于RISC-V的MR6450核心版,這引發(fā)了人們對這兩種架構(gòu)差異的深入探討。ARM

HPM5E31IGN單核 32 位 RISC-V 處理器

HPM5E31IGN單核 32 位 RISC-V 處理器在當(dāng)今嵌入式系統(tǒng)領(lǐng)域,RISC-V架構(gòu)正以開源、靈活和高性價(jià)比的優(yōu)勢快速崛起。HPM5E31IGN作為先楫半導(dǎo)體的一款單核32位RISC

發(fā)表于 05-29 09:23

FPGA與RISC-V淺談

RISC-V處理器的SoC數(shù)量在2024年約為20億顆,到2031年有望突破200億顆。 RISC-V的概念與優(yōu)勢 RISC-V是一種全新的開源指

發(fā)表于 04-11 13:53

?672次閱讀

使用 RISC-V 進(jìn)行高效數(shù)據(jù)處理的方法

使用 RISC-V 進(jìn)行高效數(shù)據(jù)處理的方法

評論