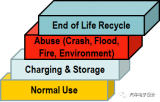

先經過以上的處置,來評估事故車輛接下來的處置,主要是包括有沒有可能會起火,主要判斷火焰、煙類似電弧之類的。接下來判斷電池有沒有損壞,包括電池的電解液、液冷系統里面的冷卻液或者其他液體;再看里面整體的線束還有其他關鍵的核心單元,這個事情其實真的不是插個CAN口那么簡單的。

2018-06-15 08:47:46 5228

5228

開關電源一般由脈沖寬度調制PWM控制IC和MOSFET構成,控制開關管時間比率維持穩定的輸出電壓。由于鐵圈匝數以及鐵芯體積的減少,開關電源的損耗很低,效率普遍較高,一般都能達到90%的電源效率。再加上其體積小,輸出穩定,在很多方面都優勢明顯。 ? ? ? 但換個角度看,其缺點也很明顯。電路復雜、電源噪聲大、瞬態響應不足、輸出紋波復雜、易產生電磁干擾等等問題也是擺在面前的,對于一些低噪聲電路,開關電源往往無能為力。這些缺點產生

2022-06-06 10:11:08 3371

3371 楷登電子今日正式推出Cadence? Tensilica? Vision Q6 DSP。該DSP基于速度更快的新處理器架構,面向嵌入式視覺和AI技術量身打造。第五代Vision Q6 DSP的視覺和AI性能較上一代Vision P6 DSP提高達1.5倍,峰值性能下的功耗效率提高1.25倍。

2018-04-12 12:35:39 16836

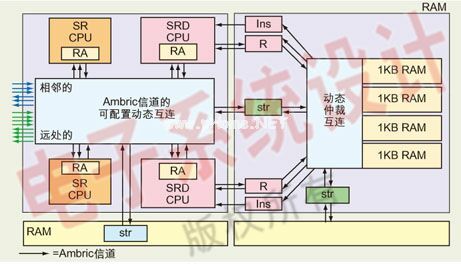

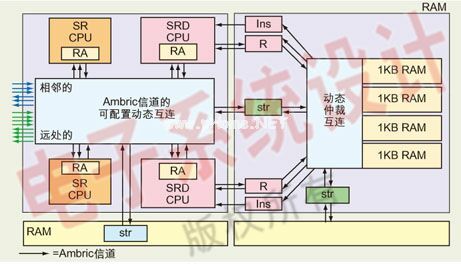

16836 技術實現多IP核集成可以顯著減少芯片的研發成本;與方法二相比,改進方法不僅能夠有效整合芯片內部資源,還可以降低系統功耗,提高芯片的整體性能。

2020-09-08 17:58:00 4232

4232

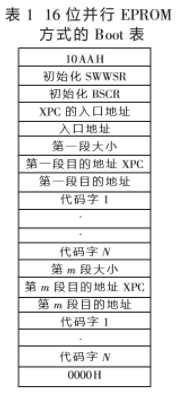

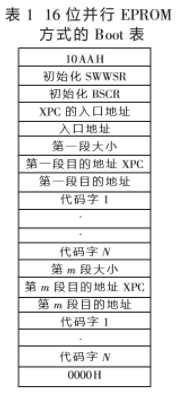

DSP芯片的BootLoader程序用于實現用戶程序上電自舉,它有多種工作方式。上電自舉就是將用戶存放在片外的非易失性、慢速的存儲器中的程序裝載到片內易失的、高速的存儲空間中,以保證用戶程序在DSP核內的高速運行。

2020-12-11 10:16:00 1967

1967

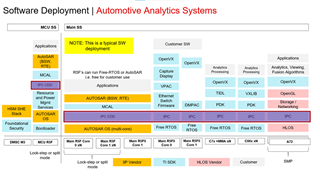

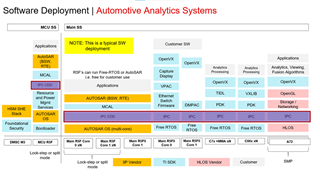

以運行在不同的模式,比如A72可以運行的SMP模式,雙核R5F可以運行在Lockstep或Split Mode上,因此,核間通信方案要充分利用硬件提供的機制,實現高效的核間通信,從而充分發揮Soc的整體性能

2022-11-03 07:26:19

語言編寫的浮點矩陣相乘處理單元[1],其關鍵技術是乘累加單元的設計,這樣設計的硬件,其性能依賴于設計者的編程水平。此外,FPGA廠商也推出了一定規模的浮點矩陣運算IP核[2],雖然此IP核應用了本廠家的器件,并經過專業調試和硬件實測,性能穩定且優于手寫代碼,但仍可對其進行改進,以進一步提高運算速度。

2019-08-22 06:41:38

,不過現在其他也有了,見賢思齊。再一方面他有專用的硬件算法電路,用以完成DSP運算,比如最基本的乘法累加。上過 DSP的就知道,蝶形算法FFT什么的,拆成最基本單元就是乘法累加,把這部分加速了,整體性能就有非常大的提高。

2020-10-22 11:28:52

為設計提供可編程邏輯解決方案所固有的靈活性特點,以及定制門陣列(如ASIC)解決方案所具有的高性能及集成度。 增強DSP處理能力的傳統方法是采用多個處理器。選擇此類方案的缺點是成本昂貴,需要眾多附加

2011-02-17 11:21:37

我正在查看MPLAB-X版本3.30的一些帖子,我看到有一些問題。一般來說,它的整體性能如何?幾個星期后我就開始設計PIC32MZ20248EFG了,我認為3.30和3.26是支持處理器的唯一版本。使用3.30版本的人能提供一些關于這個工具的反饋嗎?

2019-08-19 12:14:07

核心板的整體性能。SRAM采用快速靜態隨機存儲器SRAM(256K x 16bit),硬件如下圖:電源接口和撥碼開關采用5V@2A直流電源供電,J1為電源接口,SW1為電源擺動開關...

2021-10-28 06:02:38

SOM-TL2837x核心板的整體性能。圖 1 TL2837x-EasyEVM正面圖處理器TI TMS320F2837x單/雙核具有200MHz的高速處理能力,雙核擁有多達12路的PWM輸出。以下分別

2020-09-03 16:05:13

最先進的高性能邏輯架構之外,Virtex-5 FPGA包含許多硬IP系統級塊,包括功能強大的36 Kb塊RAM / FIFO,第二代25 x 18 DSP片,具有內置數字控制阻抗的SelectIO

2021-04-26 15:41:14

dm816x 系列,對其中C674x dsp核開發算法,有沒有可用的csl片上支持庫文件,還有該系列的DSP/BIOS什么地方下載

以前的單dsp核都有csl.h系列文件,方便配置內部寄存器,C816x 系列沒有找到。請問有提供嗎?還有DSP/BIOS,是不是下載支持C674x核的就可以用?

2018-06-21 18:58:47

核心板的測試平臺,用于快速評估som-tl5728核心板的整體性能。tl5728-easyevm底板采用沉金無鉛工藝的4層板設計,不僅為客戶提供豐富的am5728入門教程,還協助客戶進行底板的開發

2023-10-09 08:37:28

申請理由:(1)我公司變頻器核心控制系統基于DSP+FPGA平臺,重點實現算法控制,上位界面、對外通信等功能較弱,如果融入ARM平臺,將會大大提高整體性能;(2)受市場影響,我公司目前面臨產品多元化

2015-07-27 09:32:01

載能力實驗。詳情請參看附件。整體而言,表現優異,特別是電源紋波。特別適用于小型化低功耗的嵌入式需要,但是使能的響應問題請其他同學和廠家確認。

2019-03-25 20:27:15

、數據量大、距離遠、通訊協議不統一等問題。支持多種通訊規約,實現各種自動化裝置、智能儀表、變電站智能輔助設備和計算機之間信息傳遞。提供一個信息轉換率高、速度快、可靠性高的平臺,大大提高了系統整體性能。

2015-07-07 17:28:04

TMS320C6657管腳Pin to Pin兼容,它為用戶提供了SOM-TL665x核心板的測試平臺,用于快速評估SOM-TL665x核心板的整體性能。了解更多>>

2016-11-28 19:37:33

工藝的 4 層板設計,它為用戶提供了 SOM-TL6678 核心板的測試平臺,用于快速評估 SOM-TL6678 核心板的整體性能。了解更多>>

2018-10-15 10:57:23

研究都多有其應用。一個用于視頻壓縮的SoC 系統中有三個核,為了處理器間的同步和數據交換而不給AMBA系統總線增加負擔,用三個2 kB 的雙端口SRAM 將三個核兩兩相連,從而提高系統的整體性能。宇芯

2020-07-06 16:26:25

引信的核心部件,是方位識別功能和目標檢測功能的主要實現單元。其結構和性能對引信的整體性能有著至關重要的影響。隨著FPGA、DSP技術的發展,數字信號處理技術在引信中的應用大幅增強了引信信號的處理能力

2020-04-20 07:24:20

平臺。該平臺支持同一時間內32 個時鐘運行,也就是說每個片上網絡的內核可以在一個獨立的時鐘下運行, 從而使每個路由器和IP 核都運行在最佳頻率上。因此適用于設計多時鐘片上網絡,實現高性能分組交換片上網絡。

2019-08-21 06:47:43

中比較重要的一個參數,其精度對系統的整體性能有重大影響。我們自主研發的新型激光多普勒測速儀可以為純慣性導航系統提供高精度的速度值,修正純慣性導航的累積誤差,從而提高傳統慣性導航系統的穩定性和準確性

2022-08-15 14:54:31

整流濾波電路 - 基于UC3842的電動車用開關電源設計

2019-03-11 11:08:45

一種方案是采用更高主頻和更多片內資源的單核 MCU/DSP,分時地完成數據處理和輔助通信或顯示功能,這種方案顯著增加了系統成本和功耗,最致命的是,當客戶的產品需要增加新的功能的時候,工程師需要重新計算

2019-07-04 07:49:02

無論您的系統是用于無線通信、雷達,還是 EMI/EMC 測試,系統的性能水平都是由其中的天線決定的。系統天線的性能決定了系統的整體質量,最終可能會影響整個程序或應用軟件的效率。本文介紹了 5 個旨在幫助您提高天線性能的關鍵要點。

2021-02-24 07:24:14

了SOM-TL6748核心板的測試平臺,用于快速評估SOM-TL6748的整體性能。了解更多>>市場價:¥1450免費提供:50個免費申請

2015-10-21 12:11:04

適用于并行處理的現場可編程門陣列(FPGA)器件的快速發展,采用大規模FPGA為核心處理器的圖像聲納,在提高了整體性能的同時,其系統結構也更加簡單。

2019-10-09 06:04:36

做氧化鋅納米棒涂在PET上用來做TFT,想知道怎么引出電極測它的半導體性能.

2019-06-11 17:48:30

SOM-TL6678核心板的測試平臺,用于快速評估SOM-TL6678核心板的整體性能。SOM-TL6678引出CPU全部資源信號引腳,二次開發極其容易,客戶只需要專注上層運用,降低了開發難度和時間成本,讓產品快速

2018-03-21 12:10:33

以及電源模塊如何為各種子系統生成所需的電源軌。 圖1:使用電源模塊的DAQ電源架構使用電源模塊有助于提高整體性能、效率和可靠性。電源模塊還具有以下優勢:同一封裝中的輸出電流通過優化的成本提供設計靈活性

2022-11-10 08:06:14

較少·處理頂點的成本較高。

處理的頂點數量越少,整體性能就越好。

擁有更少的三角形意味著游戲可以在更多的設備上發布,而不僅僅是擁有最強大的GPU的設備。

2023-08-29 07:13:17

請問A/D轉換器MAX1324最常見的誤差源有哪些?怎么大幅度提高系統整體性能,有哪些誤差補償的方法?

2021-04-08 06:39:26

DM648比DM642整體性能提升有多少50%以上有嗎?

2019-02-20 09:56:16

如何利用ADIsimRF對零中頻分立式發射機進行電平規劃?如何了解各個器件對整體性能的貢獻?器件噪聲和失真對整個信號鏈有什么影響?

2021-04-13 06:45:07

CPU,以RS—485,CAN和LonWorks作為數據通信網絡,大多采用單板或自定義的小總線,有較強的針對性,系統結構緊湊,整體性能和可靠性較高,但存在著通用性、可擴充性以及系統升級等方面的不足。后者

2019-08-09 06:15:02

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-02 13:52:47

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-09 10:12:15

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-16 11:00:00

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-30 11:12:53

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-07 10:40:35

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-14 11:09:20

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-25 11:21:12

架構的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA XC7K325T

2016-03-23 11:03:18

基于DSP的多傳感器陣列數據采集與處理試驗平臺

2009-05-08 17:10:52 17

17 本文根據嵌入式高速DSP系統的工作特點,分析了基于該類系統中軟件設計的特殊考慮以及對系統效率的影響,從工程實際的角度提出了提高系統整體性能所要考慮的幾個重要方面的

2009-05-09 13:15:10 17

17 基本的移動IPv6 協議所定義的切換性能很差,其中延時過長的問題嚴重的影響了主機網絡的整體性能,因而不能滿足實時業務的要求。本文針對這個問題,首先分析了目前的一些解決

2009-08-12 09:08:58 13

13 BIOS設置對系統性能的影響非常大,優化的BIOS設置,可大大提高PC整體性能,不恰當的設置會導致系統性能下降,運行不穩定,甚至出現死機等現象。下面就BIOS中影響系統性能選

2009-10-10 14:27:25 43

43 賽靈思宣布開始向市場交付針對高性能數字信號處理(DSP)而優化的65 nm Virtex-5 SXT現場可編程門陣列(FPGA)器件的首批產品。SXT平臺創造了DSP性能的行業新紀錄--550MHz下性能達352 GMAC

2009-11-28 14:08:02 23

23 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 開發下一代DSP硬件平臺的挑戰包括數字信號處理(DSP)在內的下一代產品,需要提高性能和靈活性,同時縮短開發周期,降低成本與功耗。FPGA的靈活性能實現高度并行性,即便最嚴

2010-07-01 13:24:57 15

15 摘要:介紹了利用雙核DSP芯片TMS320VC5421的片內Bootloader程序實現并行引導的設計方案,給出了其軟件及硬件的具體實現方法。1 引言

2006-03-11 17:39:42 2946

2946

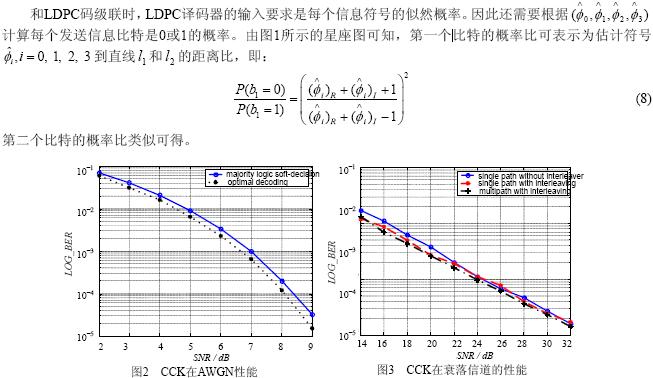

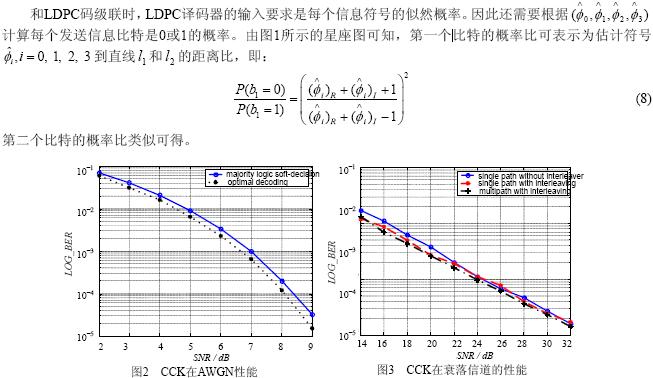

CCK調制

CCK是一種已編碼調制技術,它把擴頻、信道編碼和調制作為一個整體進行設計,從而提高系統的整體性能。CCK碼由256個8碼片的碼字

2009-03-01 17:40:19 22415

22415

高性能電源保護電路

摘要:對電源產品來講,保護電路是不可缺少的。電源配有一個高性能的保護電路對其整體性能的提高又是至關重要

2009-07-17 11:35:32 950

950

TI新推6核DSP,兼具極低功耗和高性能

以前我們依靠時鐘衡量DSP性能高低,然而這樣的對應關系并非線性,而市場的需求卻在線性增長,那如何實現性能的提升?

2009-11-06 09:35:25 911

911 BIST在SoC片上嵌入式微處理器核上的應用

引 言

隨著科技的不斷發展,集成電路的制造工藝和設計水平得到了飛速提高,設計者能夠將非常復雜的功能集成到

2009-11-07 11:18:03 1952

1952

用RapidIO提高DSP陣列的性能

“采用SERDES(串行/解串器)技術后只需少量引腳就能獲得很高的帶寬。由于硬件全部承擔了協議棧的處理,RapidIO減少了原來僅用于在系統中傳

2010-03-01 10:36:39 1787

1787

摘要:從應用角度介紹了ADSP21160 DSP芯片的基本性能,并用ADSP21160實現了基本的陣列信號測向算法-MUSIC算法著重討論了如何利用ADSP 21160的結構和開發環境來提高程序的執行效率,滿足系統設計的要求。 關鍵詞:SHARC DSP;陣列信號處理;MUSIC;測向算法

2011-02-28 23:59:15 33

33 摘要:在DSP芯片中采用DMA技術.可將DSP從數據傳輸任務中解放出來.專門從事復雜的信號處理任務,提高系統整體性能。文中介紹一種商性能32位雙通道可編程DMA控制器的設計,重點討論了該DMA的主要功能、設計構思、控制單元及主要部分的電路實現。通過對具體電

2011-03-01 01:03:29 51

51 控制的實現在調節閥, 調節閥 的控制在閥門定位器。閥門定位器的選擇,將直接影響調節閥和控制系統的整體性能和品質。選擇智能閥門定位器,提高調節閥整體性能,實現控制性能

2011-07-01 15:27:12 51

51 Tensilica1月9日宣布,推出用于(SoC)片上系統設計的HiFi 3音頻DSP(數字信號處理器)IP核。Tensilica的第四代音頻DSP提供高性能和低功耗的音頻后處理和語音處理算法功能

2012-01-11 09:02:02 4376

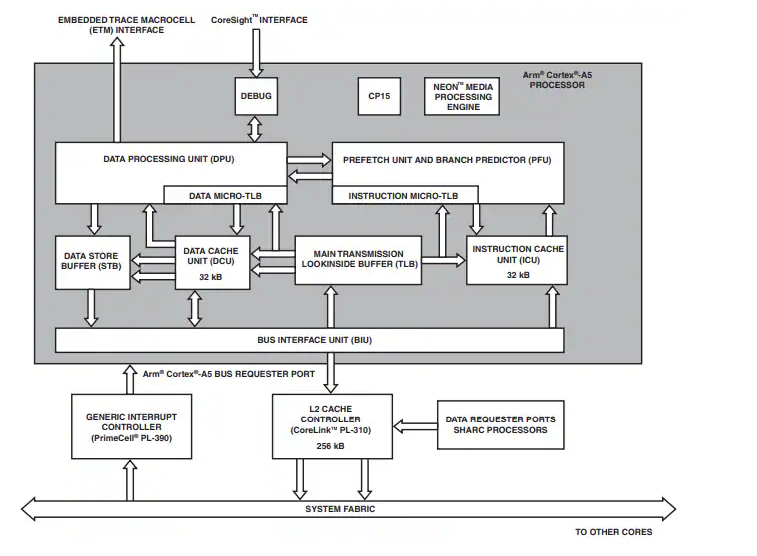

4376 。 16.2.1 存儲管理 由于在ARMv6體系結構中引入新的存儲管理機制,處理器的整體性能得到提高。在新的體系結構中,平均指令預取和數據等待時間大幅度減少,存取過程中Cache命中率顯著提高。由于存儲機制的改善,系統整體性能的提高達到30%。 另外,存儲系統的改善使系

2017-10-17 16:23:38 1

1 ,TI即推出其全新的6核DSP處理器,在實現高達4.2GHz的處理能力的同時,僅有0.15mW/MIPS的低功耗,完美契合了高性能、嚴格功率預算的應用所需。 高性能,低功耗 TMS320C6472內部

2017-10-25 14:45:22 1

1 雙核雙性能 多核不一定會使你的手機或電腦速度更快,但它將提高你的PC的整體性能,這是一個有所不同的細微的技術特色。多核處理器的性能提升并不是簡單CPU核心的倍數,因為受到兩(多)個核之間共享資源的拖累。比如雙核性能只是單核的1.4~1.8倍,實際情況取決于具體的應用。

2018-04-04 13:11:00 8397

8397 針對智能變電站二次設備故障機理復雜、通過單一指標難以有效評估設備潛在隱患的問題,根據裝置內部可觀測參數,提出一種基于變權理論與梯形云模型的二次設備整體性能模糊綜合評判方法。全面建立包含繼電保護

2018-03-02 10:58:43 0

0 Cortex-M3系列一個突出的特點就是功耗低。本文以TI公司的LM3S5749作為例子,通過試驗說明ARM的V7M版本在低功耗方面的獨特優勢,并對LM3S5749的實際功耗情況進行測試,分析不同的節電方式對系統整體性能的影響。

2018-05-09 10:52:42 13

13 高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 4833

4833 C2000整體介紹

2018-08-20 02:05:00 5077

5077 通過在可編程邏輯器件中嵌入低成本、高性能的處理器,芯片開發商不但能提高系統的整體性能,而且能夠從可編程邏輯器件原本就具備的開發時間短、上市快的特點受益。利用本文談到的Floorplanner工具可以對嵌入式處理器、相關的IP和定制邏輯進行布局控制和分組,簡化復雜系統級芯片的開發,提高系統整體性能。

2019-05-13 08:06:00 3036

3036 針對于電池企業的面臨的現實痛點,定位于全球化的智能裝備制造及技術服務型企業的贏合科技,順勢而變進行了快速應變,通過一系列積極的技術升級來探索提供套整體性的解決思路和方案,并得到了多家客戶的應用和認可。

2018-10-10 14:25:13 3408

3408 高通在香港正式發布了驍龍675處理器,其定位接近驍龍670和驍龍710。驍龍675基于三星11nm LPP工藝打造,CPU采用了全新的Kryo 460架構。高通稱,驍龍675在游戲、拍照和AI體驗方面有所提升,特別是AI應用的整體性能可提高50%。

2018-10-25 09:36:15 8652

8652 用了電容式觸摸屏。觸摸屏的實現對屏功能的擴展十分有利,應用范圍因此大大擴展。更大的屏幕尺寸對觸摸屏開辟了更廣闊的市場空間,同時也提出了更高的要求。如何保證觸摸屏系統的穩定性,如何提高系統的整體性能,如何增強用戶體驗,

2018-11-08 11:05:20 14

14 號稱“新一代神U”的驍龍710移動平臺采用10nm低功耗制程工藝,內置Kryo 360 CPU + Adreno 616 GPU組合,搭載多核人工智能引擎AI Engine,與前代相比整體性能可實現20%的提升,在AI應用中可實現高達2倍的整體性能提升。

2019-03-25 15:54:36 5132

5132 在選購筆記本時,很多童鞋只關心處理器和獨立顯卡的規格,總會忽視硬盤對整體性能的影響。

2019-05-21 09:11:36 10318

10318 材料的技術創新、性能提升,對于動力電池整體性能及成本管控起到關鍵作用。

2019-06-24 17:31:08 4190

4190 6月25日,聯發科發布了新一代手機芯片平臺Helio P65, 采用12nm制程,集成兩顆Arm Cortex-A75 CPU和六顆Cortex-A55 CPU,搭配Arm G52 GPU, 相比上代八核架構的競品,整體性能提升了25% 。

2019-08-07 15:49:30 4429

4429 因此,應根據實際的需要與可能,在確保主要指標實現的基礎上,放寬對次要指標的要求,以求得高的性能價格比。在設計、制造傳感器時,合理選擇其結構、材料和參數是保證具有良好性能價格比的前提。

2019-11-13 15:56:38 1647

1647 今日,MIUI官微公布了昨天第一次在小米社區舉行的 MIUI負責人在線總結。有用戶提議,希望MIUI應用商店提供64位App下載,對性能提高影響很大,希望小米能跟上。

2020-03-06 11:47:09 2945

2945 據外媒報道,韓國科學技術研究院能源材料中心的Hyoungchul Kim博士研究團隊成功研發了一款基于硫化物的超離子導體,可作為一種高性能固態電解質,用于全固態電池。

2020-05-20 09:05:17 1601

1601 通常在談到關于DSP解碼與系統整體性能表現時,我們主要利用了傳統的SNR、瞬時誤差和相位誤差等方法進行判斷。本文以心理-聲學壓縮設計的方法來考察DSP解碼的性能與表現,介紹了基于心理-聲學的音頻壓縮解碼概念,并給出了基于心理-聲學的DSP性能分析。

2020-09-18 10:16:00 4121

4121 用于便攜式IP核的WISHBONE1片上系統(SoC)互連結構是一種靈活的設計方法,可用于半導體IP核。其目的是通過緩解片上系統集成問題來促進設計重用。這是通過在IP核之間創建一個公共接口來實現的。這提高了系統的可移植性和可靠性,并縮短了最終用戶的上市時間。

2021-01-19 15:23:59 21

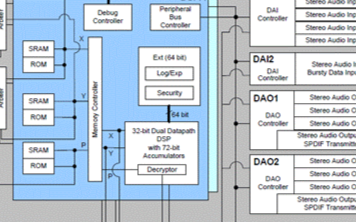

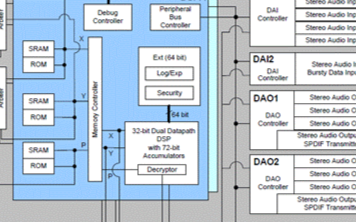

21 CS4953xx DSP系列是CS495xx DSP系列的增強版本,具有更高的整體性能和更低的系統成本。CS4953xx在片上ROM中包含所有主流音頻處理代碼。這樣可以節省用于存儲代碼的外部存儲器

2021-03-18 17:04:49 6472

6472

為了最大限度地提高利用率,應用程序的結構應該盡可能多地暴露并行性,并有效地將這種并行性映射到系統的各個組件,以使它們大部分時間都處于忙碌狀態。

2022-04-21 16:23:40 2280

2280 紋波可能會對電路產生各種危害,而且對電路極其致命。首先紋波一旦產生就容易引起諧波,對電路本身造成危害的同時降低電源效率。較高的紋波則會造成浪涌,直接破壞電路。即便不直接破壞掉電路,也會大大干擾數字電路的邏輯關系影響運行。

2022-06-06 10:26:07 2908

2908 (Inter-processor Communication)機制。核間通信的主要目標是,充分利用硬件提供的機制,實現高效的核間通信,從而充分發揮Soc的整體性能。

2023-03-16 09:19:08 1899

1899

電機性能測試系統是對電機整體性能和質量進行測量和評定的設備

2023-06-05 11:43:41 2639

2639

企業級存儲作為現代企業的“剛需”,要求高性能、高可靠性、高擴展性、高性價比,選購硬盤可就不能這么簡單粗暴,得考慮方方面面的參數。

2024-01-15 09:47:59 2456

2456 核DSP : 擁有兩個獨立的處理器核心,能夠并行處理多個任務。 主頻通常較高,能夠提供更高的計算性能,適合處理復雜且計算量大的數字信號。 能夠在同一時間內執行多個指令,提高處理速度和效率。 單核DSP : 只有一個處理器核心,按順序執行指令。 處理能力相對有限,適用

2024-09-24 16:14:58 2693

2693 提高網絡性能的阻抗優化技巧涉及多個層面,包括電路板設計、網絡架構設計、以及具體設備配置等。以下是一些關鍵的阻抗優化技巧,旨在提升網絡的整體性能: 一、電路板設計層面的阻抗優化 合理設計布線 : 在

2024-12-10 10:09:50 1382

1382 Super Harvard架構(SHA)。ADSP-SC592雙核DSP優化用于高性能音頻/浮點應用,具有大容量片上靜態隨機存取存儲器 (SRAM)。主要特性包括一個強大的DMA系統(具有8個MEMDMA)、片上內存保護和集成安全特性。

2025-06-07 11:37:00 911

911

? ?優化高多層PCB線路板的層疊結構是提升其整體性能的關鍵步驟,以下從信號完整性、電源完整性、電磁兼容性、散熱性能四大核心目標出發,結合具體優化策略和案例進行說明: 一、信號完整性優化 信號層

2025-07-10 14:56:42 412

412

電子發燒友App

電子發燒友App

評論